# SONY

# **CXD2018AQ**

# **Vertical Deflection Processing for TV**

# Description

The CXD2018AQ is a vertical deflection processing IC compatible with multi-standard TV systems.

#### **Features**

- I2C bus compatible

- Excellent synchronized stability performance and high precision deflection compensation are possible through software control.

- Non-interlace, double-speed deflection, wideaspect processing and HDTV

# **Applications**

**CRT**

#### Structure

Silicon gate CMOS IC

# Absolute Maximum Ratings (Ta=25 °C)

| <ul> <li>Supply voltage</li> </ul> | VDD   | Vss-0.5 to +7.0     | ٧ |

|------------------------------------|-------|---------------------|---|

| <ul> <li>Input voltage</li> </ul>  | Vi    | Vss-0.5 to VDD +0.5 | ٧ |

| Output voltage                     | Vo    | Vss-0.5 to VDD +0.5 | ٧ |

| - Onerating temper                 | atura |                     |   |

Operating temperature

Topr -20 to +75 °C

• Storage temperature

Tstg -55 to +150 °C

# **Recommended Operating Conditions**

• Supply voltage Vcc 4.5 to 5.5

Operating temperature

DataSheet4U.com Topr –20 to +75 °C

DataShe

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

-1-

F96801-TE

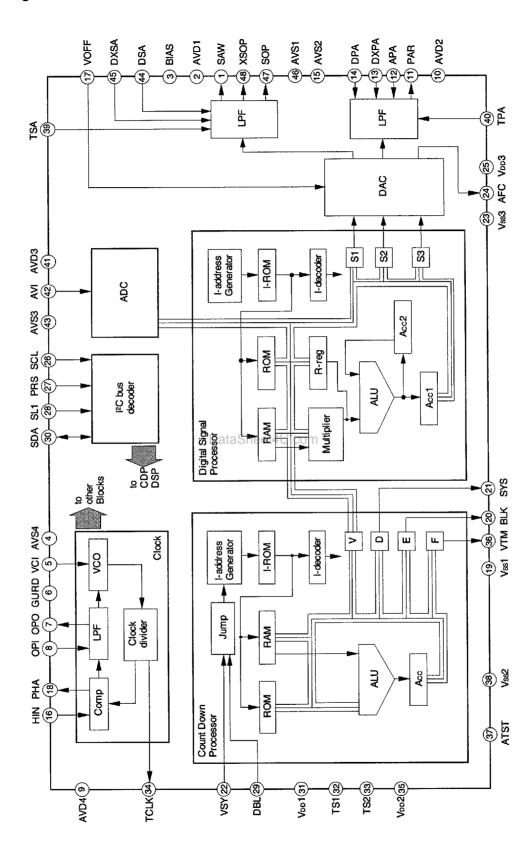

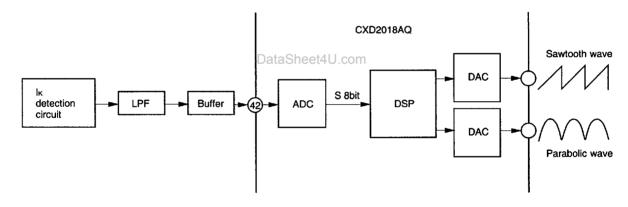

# **Block Diagram**

et4U.com

DataShe

--2--

DataSheet4U.com

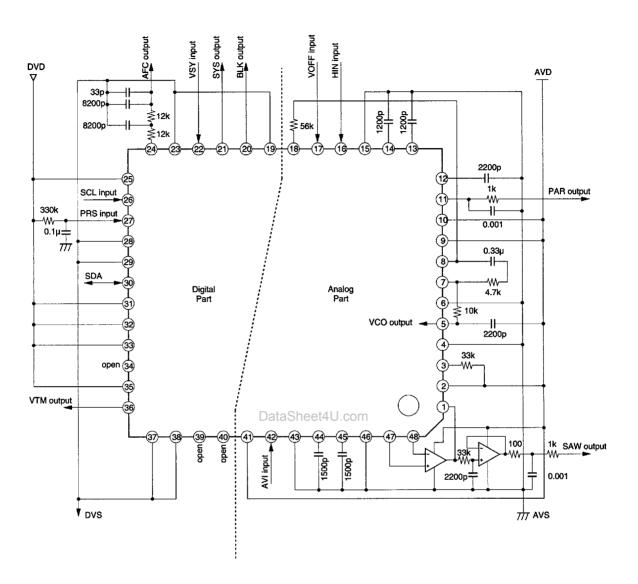

# **Pin Description**

| 1 SAW O Sawtooth wave output 2 AVD1 — Power supply for sawtooth wave output circuit (+5 V) 3 BIAS I Operational amplifier bias 4 AVS4 — GND for PLL 5 VCI I VCO for PLL 5 VCI I VCO for PLL 6 GURD — GND connection 7 OPO O PLL operational amplifier output 8 OPI I PLL operational amplifier input 9 AVD4 — PLL power supply (+5 V) 10 AVD2 — Power supply (+5 V) 11 PAR O Parabolic wave output for horizontal deflection compensation 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output for coult circuit 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output 25 Vobo3 — AFC compensation signal output 26 SCL I* IPC bus interface clock input 27 PRS I I RC bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 28 SDA I/O* IPC bus interface clock input 39 SDA I/O* IPC bus interface clock input 30 SDA I/O* IPC bus interface clock input 31 Vool — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally fixed to "High" 37 ATST I Test; normally open 38 Vss2 — GND 39 TSA O Test; normally open 40 TPA O Test; normally open | Pin No. | Symbol            | I/O      | Description                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|----------|------------------------------------------------------------------------------|

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                   |          |                                                                              |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                   |          |                                                                              |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                   | 1        |                                                                              |

| 5         VCI         I         VCO for PLL           6         GURD         — GND connection           7         OPO         O         PLL operational amplifier output           8         OPI         I         PLL operational amplifier input           9         AVD4         — PLL power supply (+5 V)           10         AVD2         — Power supply for parabolic wave output circuit (-5 V)           11         PAR         O         Parabolic wave output circuit deflection compensation           12         APA         I         Capacitor for parabolic wave output circuit           13         DXPA         I         Capacitor for parabolic wave output circuit           14         DPA         I         Capacitor for parabolic wave output circuit           15         AVS2         — Parabolic wave output circuit GND           16         HIN         I         Horizontal sync signal input           17         VOFF         I         Sawtooth wave output mute (Low: output; High: mute)           18         PHA         O         PLL phase comparison output           19         Vss1         — GND           20         BLK         O         Vertical sync signal input           21         SyS <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                           |         |                   |          |                                                                              |

| 6 GURD — GND connection 7 OPO O PLL operational amplifier output 8 OPI I PLL operational amplifier input 9 AVD4 — PLL power supply (+5 V) 10 AVD2 — Power supply for parabolic wave output circuit (-5 V) 11 PAR O Parabolic wave output for horizontal deflection compensation 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output power supply (+5 V) 25 Voc3 — AFC compensation signal output power supply (+5 V) 26 SCL I* ICC bus decoder power on reset 28 SL1 I ICC bus decoder power on reset 28 SL1 I ICC bus decoder power on reset 29 DBL I ICC bus interface clock input 29 DBL I ICC bus interface data I/O 31 Voc1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally fixed to "High" 35 Voc2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open                                                                                                                             | 5       |                   | ı        | VCO for PLL                                                                  |

| 7 OPO O PLL operational amplifier output 8 OPI I PLL operational amplifier input 9 AVD4 — PLL power supply (+5 V) 10 AVD2 — Power supply for parabolic wave output circuit (-5 V) 11 PAR O Parabolic wave output for horizontal deflection compensation 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output 25 Voo3 — AFC compensation signal output 26 SCL I* IPC bus interface clock input 27 PRS I IPC bus decoder power on reset 28 SL1 I IPC bus decoder power on reset 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by IPC bus) 30 SDA I/O* IPC bus interface data I/O 31 Voo1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally fixed to "High" 35 Voo2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND                                                                                            |         |                   |          | GND connection                                                               |

| 9 AVD4 — PLL power supply (+5 V) 10 AVD2 — Power supply for parabolic wave output circuit (-5 V) 11 PAR O Parabolic wave output for horizontal deflection compensation 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output 24 AFC O AFC compensation signal output 25 Vdd3 — AFC compensation signal output power supply (+5 V) 26 SCL I* I/C bus interface clock input 27 PRS I I/C bus decoder power on reset 28 SL1 I I/C bus decoder power on reset 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I/C bus) 30 SDA I/O* I/C bus interface data I/O 31 Vdd1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vdd2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND                                                                                                                                                                        |         | OPO               | 0        | PLL operational amplifier output                                             |

| 10 AVD2 — Power supply for parabolic wave output circuit (-5 V)  11 PAR O Parabolic wave output for horizontal deflection compensation  12 APA I Capacitor for parabolic wave output circuit  13 DXPA I Capacitor for parabolic wave output circuit  14 DPA I Capacitor for parabolic wave output circuit  15 AVS2 — Parabolic wave output circuit GND  16 HIN I Horizontal sync signal input  17 VOFF I Sawtooth wave output mute (Low: output; High: mute)  18 PHA O PLL phase comparison output  19 Vss1 — GND  20 BLK O Vertical blanking pulse output  21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output power supply (+5 V)  26 SCL I* IPC bus interface clock input  27 PRS I IPC bus decoder power on reset  28 SL1 I IPC bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by IPC bus)  30 SDA I/O* IPC bus interface data I/O  31 Voo1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Voo2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND                                                                                                                                                                              | 8       | OPI               | Ī        | PLL operational amplifier input                                              |

| 11 PAR O Parabolic wave output for horizontal deflection compensation 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output 25 Vpp3 — AFC compensation signal output 26 SCL I* IPC bus decoder power on reset 27 PRS I IPC bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by IPC bus) 30 SDA I/O* IPC bus interface data I/O 31 Vpp1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vpp2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND                                                                                                                                                                                                                                                                                           | 9       | AVD4              |          | PLL power supply (+5 V)                                                      |

| 12 APA I Capacitor for parabolic wave output circuit 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output power supply (+5 V) 25 Voo3 — AFC compensation signal output power supply (+5 V) 26 SCL I* I²C bus interface clock input 27 PRS I I²C bus decoder power on reset 28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus) 30 SDA I/O* I²C bus interface data I/O 31 Vop1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vop2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND                                                                                                                                                                                                                                                                                  | 10      | AVD2              | _        | Power supply for parabolic wave output circuit (-5 V)                        |

| 13 DXPA I Capacitor for parabolic wave output circuit 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output 25 Voo3 — AFC compensation signal output 26 SCL I* I²C bus interface clock input 27 PRS I I²C bus decoder power on reset 28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus 30 SDA I/O* I²C bus interface data I/O 31 Vpp1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vpp2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                   | 11      | PAR               | 0        | Parabolic wave output for horizontal deflection compensation                 |

| 14 DPA I Capacitor for parabolic wave output circuit 15 AVS2 — Parabolic wave output circuit GND 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output gover supply (+5 V) 26 SCL I* I2C bus interface clock input 27 PRS I I2C bus decoder power on reset 28 SL1 I I2C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus) 30 SDA I/O* I2C bus interface data I/O 31 Vbb1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally fixed to "High" 35 Vbb2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                  | 12      | APA               | ı        | Capacitor for parabolic wave output circuit                                  |

| 15 AVS2 — Parabolic wave output circuit GND  16 HIN I Horizontal sync signal input  17 VOFF I Sawtooth wave output mute (Low: output; High: mute)  18 PHA O PLL phase comparison output  19 Vss1 — GND  20 BLK O Vertical blanking pulse output  21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 Vbb3 — AFC compensation signal output  26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 Vbb1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Vbb2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13      | DXPA              | ı        | Capacitor for parabolic wave output circuit                                  |

| 16 HIN I Horizontal sync signal input 17 VOFF I Sawtooth wave output mute (Low: output; High: mute) 18 PHA O PLL phase comparison output 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output power supply (+5 V) 26 SCL I* I2C bus interface clock input 27 PRS I I2C bus decoder power on reset 28 SL1 I I2C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus) 30 SDA I/O* I2C bus interface data I/O 31 Vop1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vop2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14      | DPA               | ı        | Capacitor for parabolic wave output circuit                                  |

| 17 VOFF I Sawtooth wave output mute (Low: output; High: mute)  18 PHA O PLL phase comparison output  19 Vss1 — GND  20 BLK O Vertical blanking pulse output  21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 Vob3 — AFC compensation signal output power supply (+5 V)  26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder power on reset  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 Vob1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Vob2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15      | AVS2              | <b>—</b> | Parabolic wave output circuit GND                                            |

| 18 PHA O PLL phase comparison output  19 Vss1 — GND  20 BLK O Vertical blanking pulse output  21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 Vob3 — AFC compensation signal output power supply (+5 V)  26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 Vob1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Vob2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16      | HIN               | ı        | Horizontal sync signal input                                                 |

| 19 Vss1 — GND 20 BLK O Vertical blanking pulse output 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output 25 Vop3 — AFC compensation signal output power supply (+5 V) 26 SCL I* I²C bus interface clock input 27 PRS I I²C bus decoder power on reset 28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus) 30 SDA I/O* I²C bus interface data I/O 31 Vop1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vop2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17      | VOFF              | ı        | Sawtooth wave output mute (Low: output; High: mute)                          |

| BLK O Vertical blanking pulse output  21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 Vop3 — AFC compensation signal output power supply (+5 V)  26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 Vop1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Vop2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18      | PHA               | 0        | PLL phase comparison output                                                  |

| 21 SYS O System discrimination output (High: system M (60 Hz); Low: system B/G, I, L)  22 VSY I Vertical sync signal input  23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 VDD3 — AFC compensation signal output power supply (+5 V)  26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19      | Vss1              | _        | GND                                                                          |

| 22 VSY I Vertical sync signal input 23 Vss3 — AFC compensation signal output GND 24 AFC O AFC compensation signal output 25 Vbb3 — AFC compensation signal output 26 SCL I* I²C bus interface clock input 27 PRS I I²C bus decoder power on reset 28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus) 30 SDA I/O* I²C bus interface data I/O 31 Vbb1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vbb2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20      | BLK               | 0        | Vertical blanking pulse output                                               |

| 23 Vss3 — AFC compensation signal output GND  24 AFC O AFC compensation signal output  25 Vpp3 — AFC compensation signal output power supply (+5 V)  26 SCL I* I2C bus interface clock input  27 PRS I I2C bus decoder power on reset  28 SL1 I I2C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus)  30 SDA I/O* I2C bus interface data I/O  31 Vpp1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 Vpp2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21      | SYS               | 0        | System discrimination output (High: system M (60 Hz); Low: system B/G, I, L) |

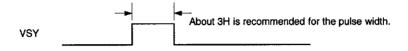

| 24 AFC O AFC compensation signal output 25 Vop3 — AFC compensation signal output power supply (+5 V) 26 SCL I* I²C bus interface clock input 27 PRS I I²C bus decoder power on reset 28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H)) 29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus) 30 SDA I/O* I²C bus interface data I/O 31 Vop1 — Power supply (+5 V) 32 TS1 I Test; normally fixed to "High" 33 TS2 I Test; normally fixed to "High" 34 TCLK O Test; normally open 35 Vop2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22      | VSY               | I        |                                                                              |

| 25 VDD3 — AFC compensation signal output power supply (+5 V) 26 SCL I* I2C bus interface clock input 27 PRS I I2C bus decoder power on reset 28 SL1 I I2C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus)  30 SDA I/O* I2C bus interface data I/O 31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23      | Vss3              | _        | AFC compensation signal output GND                                           |

| 26 SCL I* I²C bus interface clock input  27 PRS I I²C bus decoder power on reset  28 SL1 I I²C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I²C bus)  30 SDA I/O* I²C bus interface data I/O  31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24      | AFC               | 0        |                                                                              |

| 27 PRS I I2C bus decoder power on reset  28 SL1 I I2C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus)  30 SDA I/O* I2C bus interface data I/O  31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25      | VDD3              | _        |                                                                              |

| 28 SL1 I I <sup>2</sup> C bus decoder slave address switching (Low: 86 (H); High: 8E (H))  29 DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I <sup>2</sup> C bus)  30 SDA I/O* I <sup>2</sup> C bus interface data I/O  31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26      | SCL               | l*       |                                                                              |

| DBL I Double scan enable (Low: forced normal scan; High: normal/double scan selected by I2C bus)  SDA I/O* I2C bus interface data I/O  1 VDD1 — Power supply (+5 V)  Test; normally fixed to "High"  Test; normally fixed to "High"  TCLK O Test; normally open  TCLK O Test; normally open  VDD2 — Power supply (+5 V)  VDD2 — Power supply (+5 V)  Test; normally open (Or GND connection)  Test; normally open (Or GND connection)  Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27      | PRS               |          |                                                                              |

| 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28      | SL1               |          |                                                                              |

| 31 VDD1 — Power supply (+5 V)  32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29      | DBL               | 1        |                                                                              |

| 32 TS1 I Test; normally fixed to "High"  33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30      | SDA               | I/O*     | I <sup>2</sup> C bus interface data I/O                                      |

| 33 TS2 I Test; normally fixed to "High"  34 TCLK O Test; normally open  35 VDD2 — Power supply (+5 V)  36 VTM O Vertical sync timing pulse output  37 ATST I Test; normally open (Or GND connection)  38 Vss2 — GND  39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31      | V <sub>DD</sub> 1 |          | Power supply (+5 V)                                                          |

| 34 TCLK O Test; normally open 35 VDD2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32      | TS1               | 1        | Test; normally fixed to "High"                                               |

| 35 VDD2 — Power supply (+5 V) 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33      | TS2               | 1        | Test; normally fixed to "High"                                               |

| 36 VTM O Vertical sync timing pulse output 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34      | TCLK              | 0        | Test; normally open                                                          |

| 37 ATST I Test; normally open (Or GND connection) 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35      | VDD2              | <u> </u> | Power supply (+5 V)                                                          |

| 38 Vss2 — GND 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36      | VTM               | 0        | Vertical sync timing pulse output                                            |

| 39 TSA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37      | ATST              | Ī        | Test; normally open (Or GND connection)                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38      | Vss2              | _        | GND                                                                          |

| 40 TPA O Test; normally open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39      | TSA               | 0        | Test; normally open                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40      | TPA               | 0        | Test; normally open                                                          |

<sup>\*</sup>The protective diode on the  $\ensuremath{\mathsf{Vpp}}$  side for SCL and SDA pins has been eliminated.

DataShe

et4U.com

| Pin No. | Symbol | I/O | Description                                                                                   |  |  |  |  |  |

|---------|--------|-----|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 41      | AVD3   | _   | AD converter power supply                                                                     |  |  |  |  |  |

| 42      | AVI    | i   | AD converter input                                                                            |  |  |  |  |  |

| 43      | AVS3   |     | AD converter GND                                                                              |  |  |  |  |  |

| 44      | DSA    | ı   | Capacitor for vertical deflection sawtooth wave output circuit                                |  |  |  |  |  |

| 45      | DXSA   | ı   | Capacitor for vertical deflection sawtooth wave output circuit                                |  |  |  |  |  |

| 46      | AVS1   | _   | GND for vertical deflection sawtooth wave output circuit                                      |  |  |  |  |  |

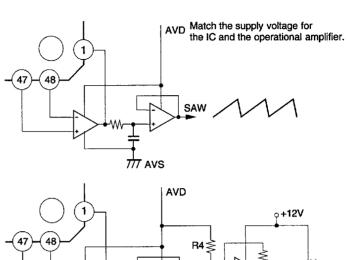

| 47      | SOP    | 0   | External operational amplifier V + input for vertical deflection sawtooth wave output circuit |  |  |  |  |  |

| 48      | XSOP   | 0   | External operational amplifier V - input for vertical deflection sawtooth wave output circuit |  |  |  |  |  |

et4U.com

DataSheet4U.com

# **Electrical Characteristics**

# **DC Characteristics**

V<sub>DD</sub>=5 V±10 %, Vss=0 V, Topr=-20 to +75 °C

|                     | ltem       | Symbol | Conditions                     | Min.    | Тур. | Max.    | Unit | Remarks |

|---------------------|------------|--------|--------------------------------|---------|------|---------|------|---------|

| Input               | High level | ViH    |                                | 0.7 VDD |      |         | ٧    |         |

| voltage 1           | Low level  | VıL    |                                |         |      | 0.3 VDD | ٧    |         |

| <b>1</b>            |            | Vt+    |                                | 0.8 VDD |      |         | ٧    | *1      |

| Input               |            | Vt-    |                                |         |      | 0.2 VDD | ٧    | *1      |

| voltage 2           | Hysteresis | Vt+Vt  |                                | 0.7     | 0.9  |         | ٧    | *1      |

| Output              |            | Vон    | Iон=−2 mA                      | VDD-0.8 |      |         | ٠٧   |         |

| voltage 1           |            | Vol    | loL=4 mA                       |         |      | 0.4     | ٧    |         |

| Output              |            | Vон    | Iон=-4 mA                      | VDD-0.8 |      |         | ٧    | *2      |

| voltage 2           |            | Vol    | loL=4 mA                       |         |      | 0.4     | ٧    | *2      |

| Input leak          | current    | lu     | Bi-directional pin input state | -40     |      | 40      | μΑ   | *3      |

| Output leak current |            | lız    | High-impedance<br>state        | -40     |      | 40      | μА   | *4      |

<sup>\*1.</sup> HIN, VSY pins, \*2. PHA pin, \*3. SDA pin, \*4. PHA, SDA pins

# I/O Pin Capacitance

VDD=Vi=0 V, f=1 MHz

| Item       | Symbol | Conditions      | Min. | Тур. | Max. | Unit |

|------------|--------|-----------------|------|------|------|------|

| Input pin  | Cin    |                 |      |      | 9    | pF   |

| Output pin | Соит   |                 |      |      | 11   | pF   |

| I/O pin    | Ci/o   | DataSheet4U.com |      |      | 11   | pF   |

et4U.com

## **Description of Function**

#### 1. Description

The CXD2018AQ is a vertical deflection processing IC compatible with multi-standard TV systems. This device basically consists of two different functional sections: countdown processor (CDP) and digital signal processor (DSP), which are respectively controlled through software. The CDP, by performing complex processing under the control of software, yields excellent synchronized stability performance to signals that contain a great deal of noise or that are missing a synchronizing component. Synchronization tracking performance during CH/VIDEO switching, system switching, and special playback operations for VCR is also outstanding in comparison with earlier systems. In addition, by performing high-level operation processing for various parameters set via the I<sup>2</sup>C bus system, the DSP permits high precision deflection compensation, making it possible to display images on large screens with little distortion. Furthermore, this IC is compatible with non-interlace, double-speed deflection, wide-aspect processing and HDTV.

et4U.com

DataSheet4U.com

# SONY

# 2. I2C Bus System

# 2.1. I2C Bus Register Map

SLAVE ADDRESS

86H, 8EH: RECEIVER MODE

87H, 8FH: TRANSMITTER MODE

| CUD ADDDESS | bit7         | bit6    | bit5         | bit4    | bit3    | bit2     | bit1     | bitO |  |  |

|-------------|--------------|---------|--------------|---------|---------|----------|----------|------|--|--|

| SUB ADDRESS |              |         | -            | V-SIZE  |         |          |          |      |  |  |

| 00 (H)      | 0            | 0       |              |         |         |          |          |      |  |  |

| 01 (H)      | 0            | 0       |              |         | V-SHIFT |          |          |      |  |  |

| 02 (H)      |              | S-CO    | RRECTION     |         |         | V-LINEAR | RITY     |      |  |  |

| 03 (H)      | 0            | 0       |              |         | H-SIZE  |          |          |      |  |  |

| 04 (H)      | 1            |         |              | PIN-AMP |         |          |          | 0    |  |  |

| 05 (H)      | 0            | 0       | 0            |         | Т       | ILT      |          | 10.1 |  |  |

| 06 (H)      |              | UPPE    | R-CORNER-F   | PIN     | İ       | LOWER-C  | CORNER-P | IN   |  |  |

|             | <del> </del> | V-      | BOW          |         |         | V-A      | NGLE     |      |  |  |

| 07 (H)      |              | V-      | 104 00140 11 |         |         |          |          |      |  |  |

| 08 (H)      | 1            | ·       | HV-COIVII -V |         |         |          |          |      |  |  |

| 09 (H)      | *            | †1      | †2           | *       | †3      | †4       | †5       | †6   |  |  |

| 0A (H)      | 0            | H-SHIFT |              |         |         |          |          | 0    |  |  |

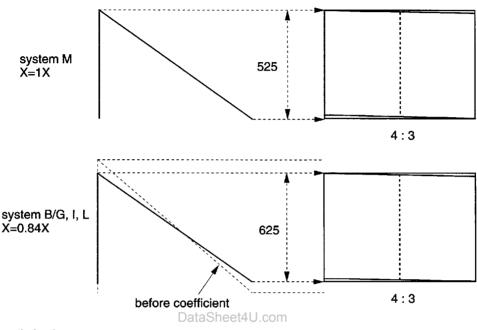

†1 Wide Aspect Ratio Frame Position

(0: center; 1: upper) (0: off; 1: on)

†2 60 Hz Fixed Mode for HDTV

(0: 100 Hz; 1:120 Hz)

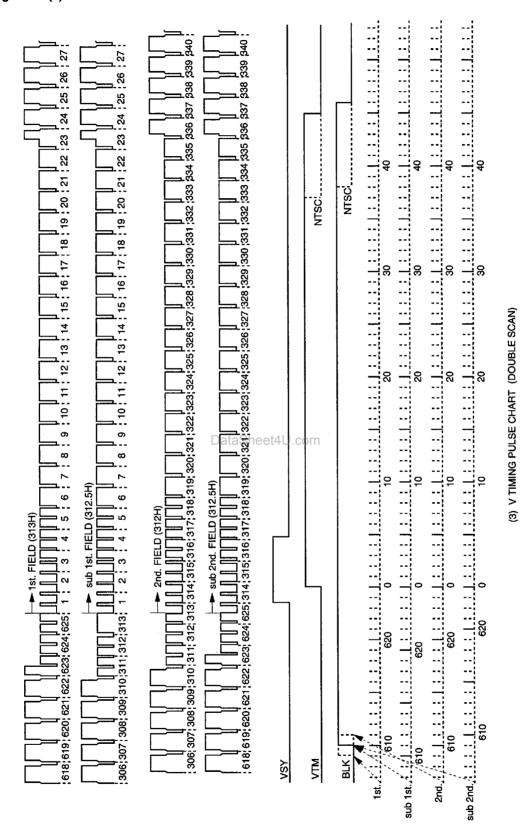

†3 System in Double Scan Mode

(0: 3:4; 1:9:16)

†4 Aspect Ratio

†5 Vertical Scan Speed

(0: 50/60 Hz; 1: 100/120 Hz)

†6 Scan Type (Interlace/Non interlace)

DataSl(0ethormatn1 : reverse)

don't care

et4U.com

#### 2.2. Description of Operation for Each Register

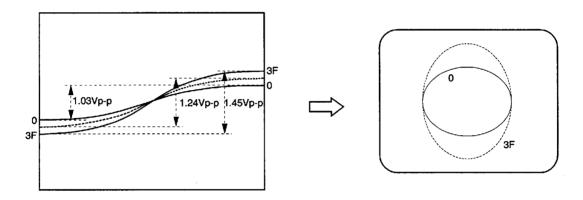

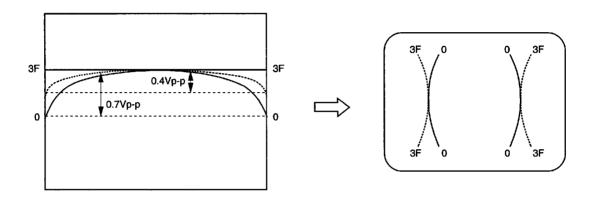

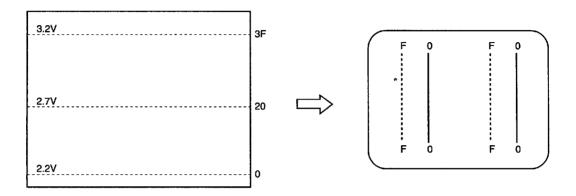

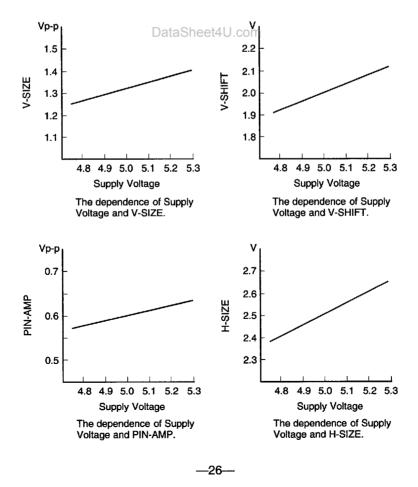

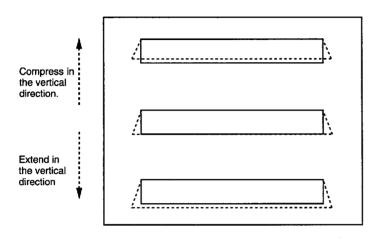

#### 2.2.1. V-SIZE

This register is used to adjust the size of the image in the vertical direction by changing the amplitude of the sawtooth wave used for vertical deflection. Because this register uses 6 bits, the size can be adjusted over a range of 64 steps. The range of adjustment is:

Maximum: 1.45 Vp-p (data = 3 F) Typical: 1.24 Vp-p (data = 20) Minimum: 1.03 Vp-p (data = 0)

et4U.com

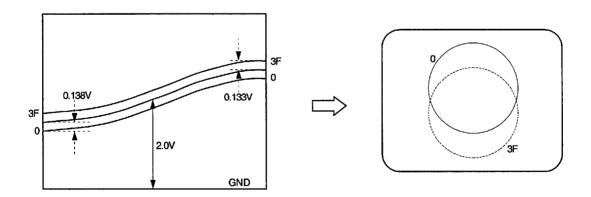

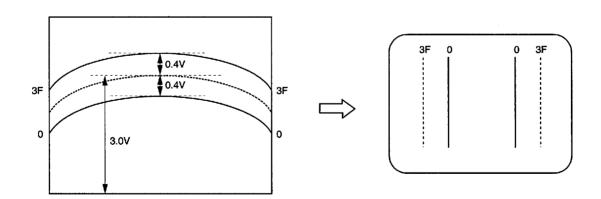

# 2.2.2. V-SHIFT

# DataSheet4U.com

This register is used to adjust the position of the image in the vertical direction by changing the DC component of the sawtooth wave used for vertical deflection. Because this register uses 6 bits, the position can be adjusted over a range of 64 steps. Using a reference value of 2.0 V, the range of adjustment is:

Maximum: +0.133 V (data = 3 F) Typical: 0 V (data = 20) Minimum: -0.138 V (data = 0)

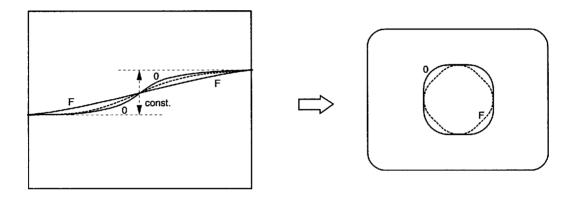

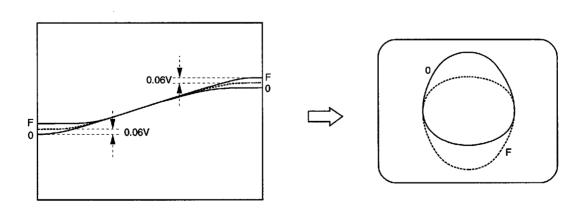

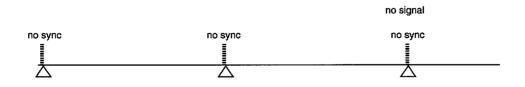

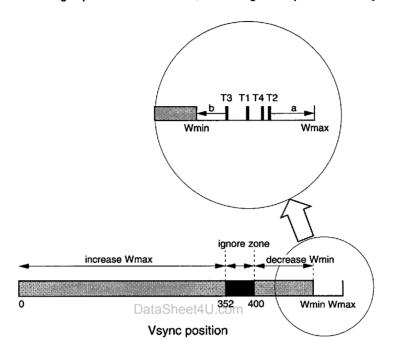

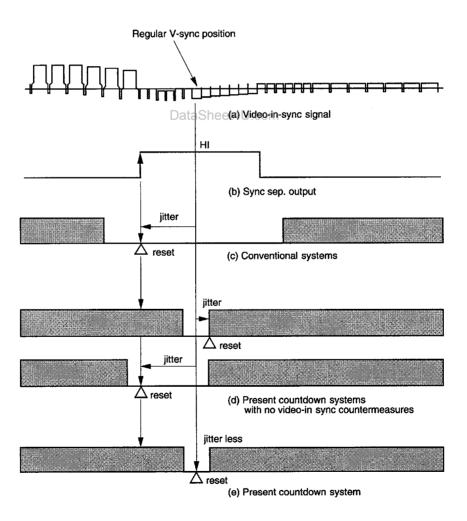

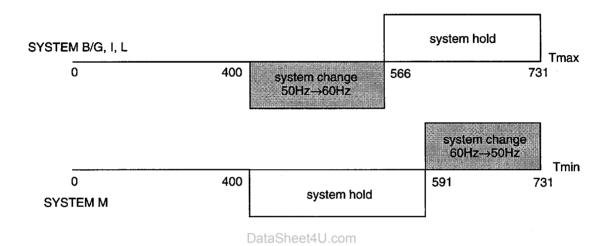

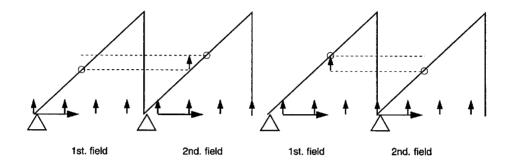

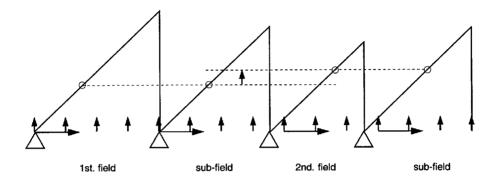

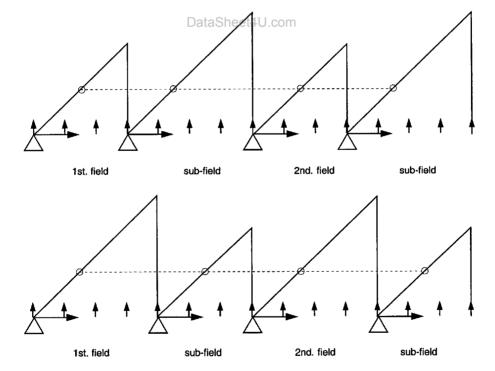

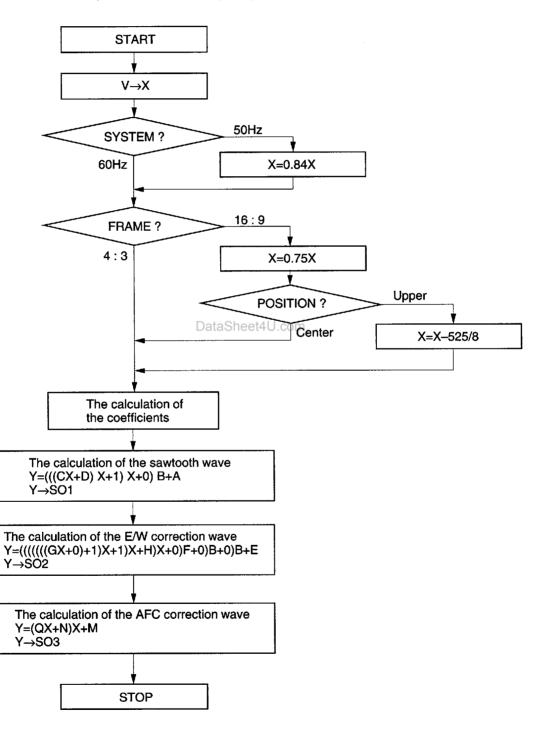

#### 2.2.3. S-CORRECTION