# MICROPOWER DC VOLTAGE DETECTOR

#### **GENERAL DESCRIPTION**

The PCF1251 is a CMOS micropower DC voltage detector and it is especially designed for power-on/off voltage detection monitoring and reset. The IC has an extremely low current consumption and is therefore particularly suited for battery operated applications. The internal bandgap reference voltage is stable with temperature variations. The voltage trip-point and the hysteresis can be set independently with external resistors. Two of the four outputs can be delayed with an external capacitor.

#### **Features**

- Extremely low current consumption

- Built-in bandgap voltage reference

- Wide range of voltage trip-points

- Two pairs of outputs; one pair with delay possibility

- 8-lead DIL or SO8 mini-pack (plastic packages).

### QUICK REFERENCE DATA

| parameter                                            | symbol<br>aSheet4U.cor | min. | typ. | max. | unit |

|------------------------------------------------------|------------------------|------|------|------|------|

| Supply voltage range with respect to V <sub>SS</sub> | V <sub>DD</sub>        | 1    | _    | 6    | ٧    |

| Supply current                                       | IDD                    | -    | 1    | -    | μΑ   |

| Output currents at V <sub>DD</sub> = 1 V             | 10                     | -    | 2    | -    | mA   |

| Bandgap voltage reference at 25 °C                   | V <sub>REF</sub>       | 1,05 | 1,15 | 1,25 | ٧    |

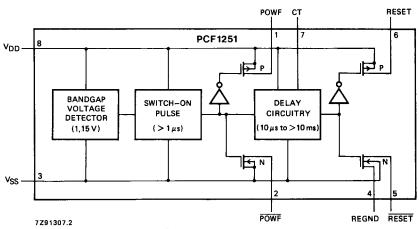

Fig. 1 Block diagram.

DataSheet4 PACKAGE OUTLINES

PCF1251P: 8-lead DIL; plastic (SOT97).

PCF1251T: 8-lead mini-pack; plastic (SO8; SOT96A).

www.DataSheet4U.com

# PCF1251

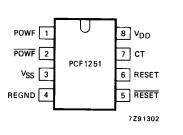

Fig. 2 Pinning diagram.

### **PINNING**

- **POWF**

- POWF

- 3  $V_{SS}$ negative supply voltage

- 4 REGND reset ground

- 5 RESET reset output (inverted; delayed)

- 6 RESET reset output (delayed)

- 7 CT 8

- $v_{DD}$ positive supply voltage

power-fail output

power-fail output (inverted)

capacitor for additional delay

## **FUNCTIONAL DESCRIPTION**

The PCF1251 consists of a bandgap voltage reference, a comparator and delay circuitry (see Fig. 1). The supply voltage of the circuit (VDD with respect to VSS) is compared with an internal bandgap voltage reference by means of a special comparator. This comparator is connected to the circuit supply voltage. As long as the supply voltage is above the reference voltage level, the four open-drain outputs are all switched off and an extended drain-source voltage of up to 6 V is allowed. When the supply voltage is reduced and reaches the reference voltage level (VREF), the power-fail outputs are switched on (p-channel for POWF and n-channel for POWF outputs). After a delay, determined by an external capacitor between pins CT and VDD, the outputs RESET and RESET are switched on. The same delay will be active when the supply voltage is increased again and exceeds the internal voltage reference, resulting in switching off the outputs.

### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

|    | max.                                                            | min.               | symbol                                    | parameter                                                                                                                                                                                                                                                                                                           |

|----|-----------------------------------------------------------------|--------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ٧  | 8                                                               | _                  | $V_{DD}$                                  | Supply voltage with respect to V <sub>SS</sub>                                                                                                                                                                                                                                                                      |

| V  | 8                                                               |                    | V <sub>2</sub>                            | Output voltage at pin 2<br>V <sub>DD</sub> with respect to V <sub>2</sub>                                                                                                                                                                                                                                           |

| V  | 8                                                               | _                  | V <sub>5</sub>                            | Output voltage at pin 5 (pin 4 at V <sub>SS</sub> )  V <sub>DD</sub> with respect to V <sub>5</sub>                                                                                                                                                                                                                 |

| V  | 8                                                               | _                  | V <sub>1</sub>                            | Output voltage at pin 1 V <sub>1</sub> with respect to V <sub>SS</sub>                                                                                                                                                                                                                                              |

| V  | 8                                                               | _                  | V <sub>6</sub>                            | Output voltage at pin 6 V <sub>6</sub> with respect to V <sub>SS</sub>                                                                                                                                                                                                                                              |

| V  | V <sub>DD</sub> + 0,5                                           | -0,5               | ٧7                                        | Voltage at pin 7 (CT)                                                                                                                                                                                                                                                                                               |

| mA | 20                                                              | _                  | 17                                        | Current at pin 7 (CT)                                                                                                                                                                                                                                                                                               |

| mΑ | 25                                                              | _                  | II <sub>O</sub> I                         | Output currents at pins 1, 2, 5 and 6                                                                                                                                                                                                                                                                               |

| mW | 150                                                             | _                  | P <sub>tot</sub>                          | Total power dissipation                                                                                                                                                                                                                                                                                             |

| οС | + 85                                                            | -40                |                                           | Operating ambient temperature range                                                                                                                                                                                                                                                                                 |

| οС | +125                                                            | -55                | T <sub>stg</sub>                          | Storage temperature range                                                                                                                                                                                                                                                                                           |

|    | 8<br>8<br>8<br>V <sub>DD</sub> + 0,5<br>20<br>25<br>150<br>+ 85 | -<br>-<br>-<br>-40 | V <sub>5</sub> V1 V6 V7 I7 IIOI Ptot Tamb | Output voltage at pin 5 (pin 4 at VSS)  VDD with respect to V5  Output voltage at pin 1  V1 with respect to VSS  Output voltage at pin 6  V6 with respect to VSS  Voltage at pin 7 (CT)  Current at pin 7 (CT)  Output currents at pins 1, 2, 5 and 6  Total power dissipation  Operating ambient temperature range |

### **HANDLING**

DataSheet4U. Inputs and outputs are protected against electrostatic charge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see 'Handling MOS Devices').

et4U.com

## **CHARACTERISTICS**

$V_{DD} = 1$  to 6 V;  $V_{SS} = 0$  V;  $T_{amb} = -40$  to + 85 °C; unless otherwise specified

| parameter                                                                                                                                               | symbol                | min. | typ. | max. | unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| Operating supply voltage                                                                                                                                | V <sub>DD</sub>       | 1    |      | 6    | V    |

| Operating supply current  VDD = 6 V; all outputs open                                                                                                   | IDD                   | _    | 1    | 3    | μΑ   |

| Bandgap voltage reference; T <sub>amb</sub> = 25 °C                                                                                                     | V <sub>REF</sub>      | 1,05 | 1,15 | 1,25 | .V   |

| V <sub>REF</sub> temperature coefficient                                                                                                                | ΔV <sub>REF</sub> /ΔΤ | _    | -0,4 | _    | mV/K |

| Output current at pins 2 and 5<br>$T_{amb} = 25  {}^{o}C; V_{DD} < V_{REF};$<br>$V_{O} = 0,4  V$ with respect to $V_{SS}$                               | Io                    | 1    | 2    | _    | mA   |

| Output current at pins 1 and 6  T <sub>amb</sub> = 25 °C; V <sub>DD</sub> < V <sub>REF</sub> ;  -V <sub>O</sub> = 0.4 V with respect to V <sub>DD</sub> | -10                   | 1    | 2    | _    | mA   |

DataShe

(1) For correct switching of the outputs the slew rate of the supply voltage should be less than 1 V/ms.

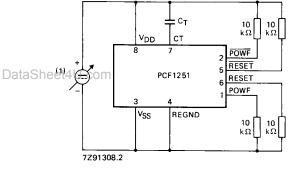

Fig. 3 Test circuit for timing measurements.

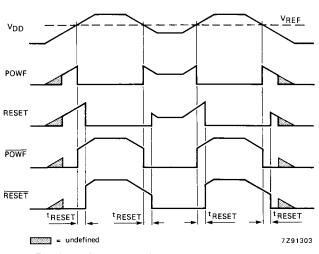

Fig. 4 Timing diagram for slow supply voltage changes.

www.DataSheet4U.com

DataSheet4U.com

# PCF1251

b)  $C_T \ge 0.1 \text{ nF: } t_{RESET} =$

$\left[0,1+3,2 \text{ ms x C}_{T}\left(\frac{nF}{nF}\right)\right]_{-50\%}^{+75\%}$

$V_{DD}$ POWF RESET POWF RESET tRESET (1) tPOWF > 1 µs (typ. 25 µs) 7291304.2 = undefined (typ. 7 μs)

et4U.com

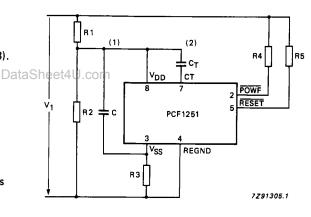

### APPLICATION INFORMATION

(1) The value of capacitor C is chosen to limit the slew rate of the supply

Fig. 5 Timing diagram for fast supply

voltage switching on (non-repetitive).

- voltage to less than 1 V/ms (e.g. the hysteresis voltage step on resistor R3). (2) CT (pin 7) is a high-impedance connection for the capacitor CT. This capacitor adds to the reset delay time provided by an internal current source (120 nA) and capacitor. Care must be taken to

- avoid external leakage current at this pin but the pin should not be left open circuit as stray capacitances to VSS can then disturb the delay function.

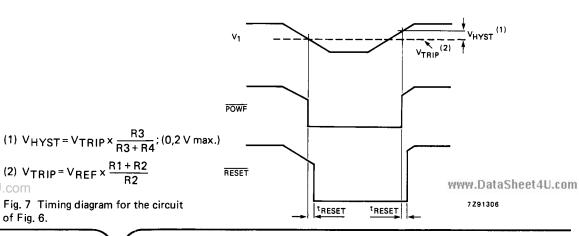

Fig. 6 Application circuit diagram.

(2)  $V_{TRIP} = V_{REF} \times \frac{R1 + R2}{R2}$

Fig. 7 Timing diagram for the circuit of Fig. 6.