# **DUAL FORWARD-CONDUCTING P-GATE THYRISTOR** PROGRAMMABLE OVERVOLTAGE PROTECTOR

# **TISP61089HDM Overvoltage Protector**

Intended for Use in GR-1089-CORE Issue 3 Compliant **Line Cards**

**Dual, Voltage-Programmable SLIC Protector**

- Low 15 mA max. Gate Triggering Current

- Supports Battery Voltages Down to -155 V

- High 150 mA min. Holding Current

### Rated for GR-1089-CORE Issue 3 Conditions

| Impulse Waveshape | GR-1089-C        | I <sub>PPSM</sub> |     |

|-------------------|------------------|-------------------|-----|

| impuise wavesnape | Section          | Test #            | Α   |

| 2/10              | 4.6.7<br>4.6.8   | 4<br>1            | 500 |

| 10/1000           | 4.6.7<br>4.6.7.1 | 1, 3<br>1         | 100 |

### Meets GR-1089-CORE First Level A.C. Power Fault Conditions

| GR-1089-CORE             | IRMS | Power Fault Duration |

|--------------------------|------|----------------------|

| Section 4.6.10<br>Test # | Α    | s                    |

| 1                        | 0.33 | 900                  |

| 2                        | 0.17 | 900                  |

| 3                        | 1    | 1                    |

| 4                        | 1    | 1                    |

| 6                        | 0.5  | 30                   |

| 7                        | 2.2  | 2                    |

| 8                        | 3    | 1.1                  |

| 9                        | 5    | 0.4                  |

GR-1089-CORE Second Level A.C. Power Fault Conditions are Detailed in the 'Applications Information' Section

\*\* ...... UL Recognized Component

### **Additional Information**

Click these links for more information:

PRODUCT TECHNICAL INVENTORY SAMPLES

## **Agency Recognition**

| Description |                             |  |

|-------------|-----------------------------|--|

| UL          | File Number: <u>E215609</u> |  |

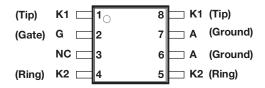

### 8-SOIC (210 mil) Package (Top View)

NC - No internal connection Terminal typical application names shown in parenthesis MD-8SOIC(210)-001-b

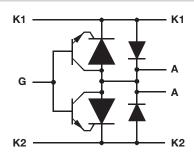

### **Device Symbol**

The negative protection voltage is controlled by the voltage, V<sub>GG</sub>, applied to the G terminal.

## **How To Order**

| Device       | Package          | Carrier              | Order As        | Marking Code | Standard Quantity |

|--------------|------------------|----------------------|-----------------|--------------|-------------------|

| TISP61089HDM | 8-SOIC (210 mil) | Embossed Tape Reeled | TISP61089HDMR-S | 61089H       | 2000              |

The products described herein and this document are subject to specific legal disclaimers as set forth on the last page of this document, and at www.bourns.com/docs/legal/disclaimer.pdf.

# **TISP61089HDM Overvoltage Protector**

# **BOURNS**®

#### Description

The TISP61089HDM is a dual forward-conducting buffered p-gate thyristor (SCR) overvoltage protector. It is designed to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. The TISP61089HDM limits voltages that exceed the SLIC supply rail voltage. The TISP61089HDM parameters are specified to allow equipment compliance with Telcordia GR-1089-CORE, Issue 3 and ITU-T recommendations K.20, K.21 and K.45.

The SLIC line driver section is typically powered from 0 V (ground) and a negative voltage in the region of -20 V to -155 V. The protector gate is connected to this negative supply. This references the protection (clipping) voltage to the negative supply voltage. The protection voltage will then track the negative supply voltage and the overvoltage stress on the SLIC is minimized.

Positive overvoltages are clipped to ground by diode forward conduction. Negative overvoltages are initially clipped close to the SLIC negative supply rail value. If sufficient current is available from the overvoltage, then the protector SCR will switch into a low voltage on-state condition. As the overvoltage subsides the high holding current of TISP61089HDM SCR prevents d.c. latchup.

The TISP61089HDM is designed to be used with a pair of Bourns® SF-3812TM125T-2 fuses for overcurrent protection. Level 2 power fault compliance requires the series overcurrent element to become open-circuit or high impedance. For equipment compliant to ITU-T recommendations K.20, K.21 or K.45 only, the series resistor value is set by the coordination requirements. For coordination with a 400 V limit GDT, a minimum series resistor value of  $6.5 \Omega$  is recommended.

# Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                                             | Symbol            | Value       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|------|

| Repetitive peak off-state voltage, V <sub>GK</sub> = 0                                                                                                                                                                             | V <sub>DRM</sub>  | -170        | ٧    |

| Repetitive peak gate-cathode voltage, V <sub>KA</sub> = 0                                                                                                                                                                          | V <sub>GKRM</sub> | -167        | ٧    |

| Non-repetitive peak impulse current (see Notes 1, 2 and 3)                                                                                                                                                                         |                   |             |      |

| 10/1000 μs (Telcordia GR-1089-CORE, Issue 3)                                                                                                                                                                                       |                   | 100         |      |

| 5/310 μs (ITU-T K.20, K.21 & K.45, K.44 open-circuit voltage wave shape 10/700 μs) 10/360 μs (Telcordia GR-1089-CORE, Issue 3) 1.2/50 μs voltage waveshape (Telcordia GR-1089-CORE, Issue 3), including 3 Ω non-inductive resistor |                   | 150         |      |

|                                                                                                                                                                                                                                    |                   | 100         | Α    |

| 1.2/50 $\mu$ s voltage waveshape (Telcordia GR-1089-CORE, Issue 3), including 3 $\Omega$ non-inductive resistor                                                                                                                    |                   | 500         |      |

| 2/10 μs (Telcordia GR-1089-CORE, Issue 3)                                                                                                                                                                                          |                   | 500         |      |

| Non-repetitive peak on-state current, 50 Hz / 60 Hz (see Notes 1, 2, 3 and 4)                                                                                                                                                      |                   |             |      |

| 0.5 s                                                                                                                                                                                                                              |                   | 7.7         |      |

| 0.5 s<br>1 s                                                                                                                                                                                                                       |                   | 6.1         |      |

| 2 s                                                                                                                                                                                                                                | L                 | 4.8         | Α    |

| 5 s                                                                                                                                                                                                                                | ITSM              | 3.7         | _ ^  |

| 30 s                                                                                                                                                                                                                               |                   | 2.8         |      |

| 900 s                                                                                                                                                                                                                              |                   | 2.6         |      |

| Junction temperature                                                                                                                                                                                                               | TJ                | -40 to +150 | °C   |

| Storage temperature range                                                                                                                                                                                                          | T <sub>stg</sub>  | -65 to +150 | °C   |

- NOTES: 1. Initially the device must be in thermal equilibrium with T<sub>J</sub> = 25 °C. The surge may be repeated after the device returns to its initial

- 2. The rated current values may be applied either to the Ring to Ground or to the Tip to Ground terminal pairs. Additionally, both terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the rated current value of an individual terminal pair). Ratings are obtained by using the gate circuitry as shown in Fig. 3.

- 3. Rated currents only apply if pins 1 & 8 (Tip) are connected together, pins 4 & 5 (Ring) are connected together and pins 6 & 7 (Anode) are connected together.

- 4. EIA/JESD51-2 environment and EIA/JESD51-7 high effective thermal conductivity test board (multi-layer) connected with 0.6 mm printed wiring track widths.

## Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                     | Parameter                              | Test Conditions                                                                                                                                         |                                                  | Min  | Тур | Max            | Unit |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|-----|----------------|------|

| I <sub>D</sub>      | Off-state current                      | $V_D = V_{DRM}, V_{GK} = 0$                                                                                                                             | $T_A = 25 ^{\circ}C$<br>$T_A = 85 ^{\circ}C$     |      |     | -5<br>-50      | μΑ   |

| V <sub>GK(BO)</sub> | Gate-cathode impulse breakover voltage | 10/1000 μs, $I_{TM}$ = 100 A, $V_{GG}$ = -100 V 5/310 μs, $I_{TM}$ = 150 A, $V_{GG}$ = -100 V 2/10 μs, $I_{TM}$ = 200 A, $V_{GG}$ = -100 V (see Note 5) |                                                  |      |     | 12<br>12<br>20 | V    |

| V <sub>F</sub>      | Forward voltage                        | I <sub>F</sub> = 5 A, t <sub>W</sub> = 200 μs                                                                                                           |                                                  |      |     | 3              | V    |

| V <sub>FRM</sub>    | Peak forward recovery voltage          | 10/1000 μs, $I_F$ = 100 A, $V_{GG}$ = -100 V<br>5/310 μs, $I_F$ = 150 A, $V_{GG}$ = -100 V<br>2/10 μs, $I_F$ = 200 A, $V_{GG}$ = -100 V (see Note 5)    |                                                  |      |     | 6<br>7<br>10   | V    |

| I <sub>H</sub>      | Holding current                        | $I_T = -1 \text{ A, di/dt} = 1 \text{ A/ms, } V_{GG} = -100 \text{ V}$                                                                                  |                                                  | -150 |     |                | mA   |

| I <sub>GKS</sub>    | Gate reverse current                   | $V_{GG} = V_{GK} = V_{GKRM}, V_{KA} = 0$                                                                                                                | T <sub>A</sub> = 25 °C<br>T <sub>A</sub> = 85 °C |      |     | -5<br>-50      | μΑ   |

| I <sub>GT</sub>     | Gate trigger current                   | $I_T = -3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -100 \text{ V}$                                                                             |                                                  |      |     | 15             | mA   |

| V <sub>GT</sub>     | Gate-cathode trigger voltage           | $I_T = -3 \text{ A}, t_{p(g)} \ge 20 \mu \text{s}, V_{GG} = -100 \text{ V}$                                                                             |                                                  |      |     | 2.5            | V    |

| C <sub>KA</sub>     | Cathode-anode off-state capacitance    | $f = 1 \text{ MHz}, V_d = 1 \text{ V rms}, V_D = -50 \text{ V}, I_G = 0$                                                                                |                                                  |      |     | 40             | рF   |

NOTE: 5. Voltage measurements should be made with an oscilloscope with limited bandwidth (20 MHz) to avoid high frequency noise.

## Thermal Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|   | Parameter Test Conditions                              |                                                                                 | Min | Тур | Max | Unit |

|---|--------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| F | $R_{\theta JA}$ Junction to ambient thermal resistance | EIA/JESD51-7 PCB, EIA/JESD51-2 Environment, P <sub>TOT</sub> = 4 W (See Note 6) |     | 55  |     | °C/W |

NOTE 6. EIA/JESD51-7 high effective thermal conductivity test board (multi-layer) connected with 0.6 mm printed wiring track widths.

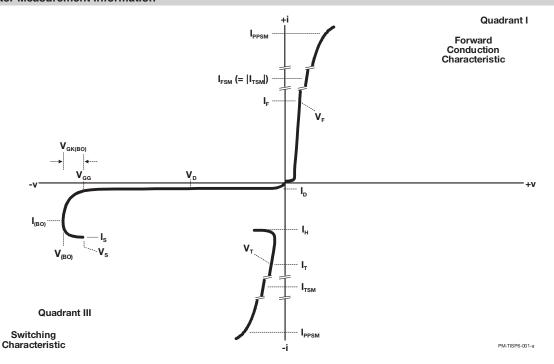

#### **Parameter Measurement Information**

Figure 1. Voltage-Current Characteristic Unless Otherwise Noted, All Voltages are Referenced to the Anode

## **Thermal Information**

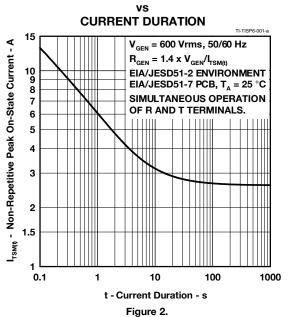

## **NON-REPETITIVE PEAK ON-STATE CURRENT**

#### **APPLICATIONS INFORMATION**

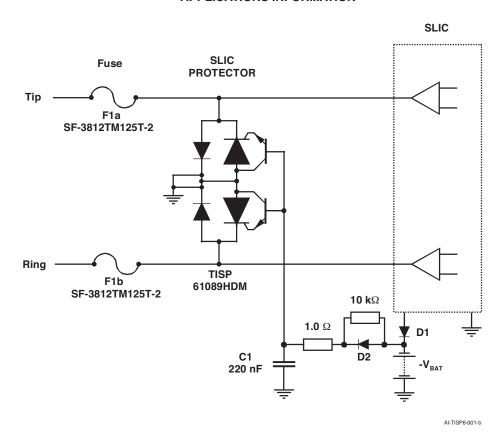

Figure 3. Line Protection with TISP61089HDM

Figure 3 illustrates how a typical SLIC protection circuit may look for a TISP61089HDM and a pair of Bourns® SinglFuse™ Telefuse™ Telecom Protectors. This is a generic circuit that is designed to withstand both lightning surge testing and AC power fault testing. As applications can differ, it is recommended you contact your Bourns representative for detailed applications guidance on your specific design.

## **APPLICATIONS INFORMATION (Continued)**

GR-1089-CORE Issue A.C. Power Fault testing has been comprehended in the design of the TISP61089HDM. For compliance, circuit designs must pass both First Level and Second Level A.C. Power Fault testing.

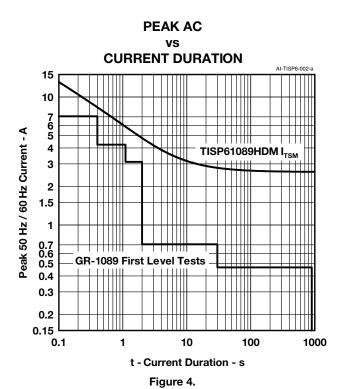

First Level Power Fault testing requires that the equipment shall not be damaged and continues to operate correctly without disruption to other parts of the system. In laboratory tests it has been shown that the circuit shown in Figure 3 can pass these tests without damage. Figure 4 shows the TISP61089HDM I<sub>TSM</sub> rating to be above the level of GR-1089-CORE First Level tests.

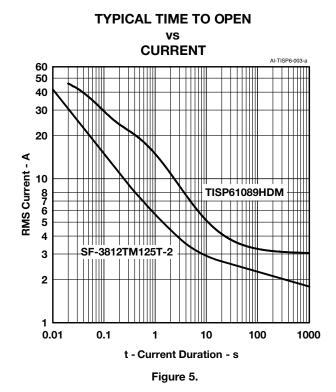

Second Level Power Fault testing may result in the equipment becoming non-operational, but any component failure should not allow the equipment to become a hazard. The system should not burn, fragment, or become an electrical safety hazard. The test data in Figure 5 illustrates that the TISP61089HDM and the SF-3812TM125T-2 are current coordinated, as the fuse interrupt time is shorter than the time it takes to damage the TISP61089HDM package for a given current.

# **BOURNS**®

Asia-Pacific: Tel: +886-2 2562-4117 • Email: asiacus@bourns.com

EMEA: Tel: +36 88 885 877 • Email: eurocus@bourns.com

The Americas: Tel: +1-951 781-5500 • Email: americus@bourns.com

www.bourns.com

"TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in the U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.

MAY 2004 - REVISED APRIL 2022

Specifications are subject to change without notice.

Users should verify actual device performance in their specific applications.

The products described herein and this document are subject to specific legal disclaimers as set forth on the last page of this document, and at www.bourns.com/docs/legal/disclaimer.pdf.

# **Legal Disclaimer Notice**

This legal disclaimer applies to purchasers and users of Bourns® products manufactured by or on behalf of Bourns, Inc. and its affiliates (collectively, "Bourns").

Unless otherwise expressly indicated in writing, Bourns® products and data sheets relating thereto are subject to change without notice. Users should check for and obtain the latest relevant information and verify that such information is current and complete before placing orders for Bourns® products.

The characteristics and parameters of a Bourns® product set forth in its data sheet are based on laboratory conditions, and statements regarding the suitability of products for certain types of applications are based on Bourns' knowledge of typical requirements in generic applications. The characteristics and parameters of a Bourns® product in a user application may vary from the data sheet characteristics and parameters due to (i) the combination of the Bourns® product with other components in the user's application, or (ii) the environment of the user application itself. The characteristics and parameters of a Bourns® product also can and do vary in different applications and actual performance may vary over time. Users should always verify the actual performance of the Bourns® product in their specific devices and applications, and make their own independent judgments regarding the amount of additional test margin to design into their device or application to compensate for differences between laboratory and real world conditions.

Unless Bourns has explicitly designated an individual Bourns® product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949) or a particular qualification (e.g., UL listed or recognized), Bourns is not responsible for any failure of an individual Bourns® product to meet the requirements of such industry standard or particular qualification. Users of Bourns® products are responsible for ensuring compliance with safety-related requirements and standards applicable to their devices or applications.

Bourns® products are not recommended, authorized or intended for use in nuclear, lifesaving, life-critical or life-sustaining applications, nor in any other applications where failure or malfunction may result in personal injury, death, or severe property or environmental damage. Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any Bourns® products in such unauthorized applications might not be safe and thus is at the user's sole risk. Life-critical applications include devices identified by the U.S. Food and Drug Administration as Class III devices and generally equivalent classifications outside of the United States.

Bourns expressly identifies those Bourns® standard products that are suitable for use in automotive applications on such products' data sheets in the section entitled "Applications." Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any other Bourns® standard products in an automotive application might not be safe and thus is not recommended, authorized or intended and is at the user's sole risk. If Bourns expressly identifies a sub-category of automotive application in the data sheet for its standard products (such as infotainment or lighting), such identification means that Bourns has reviewed its standard product and has determined that if such Bourns® standard product is considered for potential use in automotive applications, it should only be used in such sub-category of automotive applications. Any reference to Bourns® standard product in the data sheet as compliant with the AEC-Q standard or "automotive grade" does not by itself mean that Bourns has approved such product for use in an automotive application.

Bourns® standard products are not tested to comply with United States Federal Aviation Administration standards generally or any other generally equivalent governmental organization standard applicable to products designed or manufactured for use in aircraft or space applications. Bourns expressly identifies Bourns® standard products that are suitable for use in aircraft or space applications on such products' data sheets in the section entitled "Applications." Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any other Bourns® standard product in an aircraft or space application might not be safe and thus is not recommended, authorized or intended and is at the user's sole risk.

The use and level of testing applicable to Bourns® custom products shall be negotiated on a case-by-case basis by Bourns and the user for which such Bourns® custom products are specially designed. Absent a written agreement between Bourns and the user regarding the use and level of such testing, the above provisions applicable to Bourns® standard products shall also apply to such Bourns® custom products.

Users shall not sell, transfer, export or re-export any Bourns® products or technology for use in activities which involve the design, development, production, use or stockpiling of nuclear, chemical or biological weapons or missiles, nor shall they use Bourns® products or technology in any facility which engages in activities relating to such devices. The foregoing restrictions apply to all uses and applications that violate national or international prohibitions, including embargos or international regulations. Further, Bourns® products and Bourns technology and technical data may not under any circumstance be exported or re-exported to countries subject to international sanctions or embargoes. Bourns® products may not, without prior authorization from Bourns and/or the U.S. Government, be resold, transferred, or re-exported to any party not eligible to receive U.S. commodities, software, and technical data.

To the maximum extent permitted by applicable law, Bourns disclaims (i) any and all liability for special, punitive, consequential, incidental or indirect damages or lost revenues or lost profits, and (ii) any and all implied warranties, including implied warranties of fitness for particular purpose, non-infringement and merchantability.

For your convenience, copies of this Legal Disclaimer Notice with German, Spanish, Japanese, Traditional Chinese and Simplified Chinese bilingual versions are available at:

Web Page: http://www.bourns.com/legal/disclaimers-terms-and-policies

PDF: http://www.bourns.com/docs/Legal/disclaimer.pdf