USER'S MANUAL

# $\mu$ PD72103A HDLC CONTROLLER

$\mu$ PD72103A

#### NOTES FOR CMOS DEVICES

# 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

#### V25+ is a trademark of NEC Corporation.

The export of this product from Japan is prohibited without governmental license. To export or re-export this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

#### **PREFACE**

Target users

This manual describes the functions of the  $\mu$ PD72103A to engineers who will use the  $\mu$ PD72103A when designing application systems.

Objective

The objective of this manual is to describe the hardware functions of the  $\mu$ PD72103A, which includes the following components.

Composition

This manual can be broadly divided into the following sections.

- General

- Bus interface

- Communication operations

- Commands

- Status

- System configuration example

- Example of  $\mu$ PD72103A's operation sequence

- · Connecting HDLC controller to a Motorola system

- Questions and answers about the μPD72103A

- Command list

- · Status list

Use

This manual assumes that the reader has a general knowledge of electricity, logic circuits, and microcontrollers.

- · Users who would like to check commands

- → Read "CHAPTER 4 COMMAND LIST".

- Users who would like to learn about the  $\mu$ PD72103A's functions

- $\rightarrow$  Read this manual in the order shown in the Table of Contents.

- Users who have questions about the  $\mu$ PD72103A's operations

- → Read "APPENDIX C Q&A".

Legend Data representation weight: High-order digits are indicated at left and low-order digits

at right.

Active low representation : xxx (pin or signal name is overlined) or xxxB ("B" is added

after signal and pin names)

Memory map address : High order at low stage and low order at high stage (address

0H)

Note : Explanation of Note in the text

Caution : Item deserving extra attention

**Remark** : Supplementary explanation to the text

Number representation : Decimal number is xxxx

Hexadecimal number is xxxxH

Appendix C uses the following abbreviations for reference documentation.

$\begin{array}{ll} \mbox{Data sheet} & \rightarrow \mbox{DS} \\ \mbox{User's manual} & \rightarrow \mbox{UM} \\ \mbox{Application note} & \rightarrow \mbox{AN} \end{array}$

#### **Related Documentation**

| Document name | Data Sheet              | User's Manual | Application Note |

|---------------|-------------------------|---------------|------------------|

| μPD72103A     | S10189J <sup>Note</sup> | This manual   | _                |

The corresponding application note for this manual is the  $\mu$ PD72103 APPLICATION NOTE (IEA-713<sup>Note</sup>). In this application note, all references to the  $\mu$ PD72103 should be understood as referring to the  $\mu$ PD72103A.

Note This document number is that of the Japanese version.

# **TABLE OF CONTENTS**

| CHAPTE | R 1 GENERAL                                                             | 1  |

|--------|-------------------------------------------------------------------------|----|

| 1.1    | Features                                                                | 1  |

| 1.2    | Block Diagram                                                           | 2  |

| 1.3    | Internal Block Functions                                                | 3  |

| 1.4    | Pin Configuration (Top View)                                            | 4  |

| 1.5    | Pin Functions                                                           | 6  |

| 1.6    | Initialization via Reset                                                | 11 |

| CHAPTE | ER 2 BUS INTERFACE                                                      | 13 |

| 2.1    | Internal Registers                                                      | 13 |

|        | 2.1.1 Control register                                                  | 14 |

|        | 2.1.2 Internal status register                                          |    |

| 2.2    | DMAC (Direct Memory Access Controller)                                  |    |

|        | 2.2.1 Block transfers                                                   | 16 |

|        | 2.2.2 Extension of active (low-level) width of MRD and MWR signals      | 17 |

|        | 2.2.3 Basic timing of DMA                                               |    |

|        | 2.2.4 Address/data multiplexing                                         |    |

| 2.3    |                                                                         |    |

|        | 2.3.1 Command issuance                                                  |    |

|        | 2.3.2 Status report                                                     |    |

|        | 2.3.3 Command chain function                                            |    |

| 2.4    | , <b>,</b>                                                              |    |

| 2.5    | ,                                                                       |    |

|        | 2.5.1 Command table                                                     |    |

|        | 2.5.2 Status table                                                      |    |

|        | 2.5.3 Receive buffer address table                                      |    |

|        | 2.5.4 Receive buffer                                                    |    |

|        | 2.5.5 Transmit buffer                                                   |    |

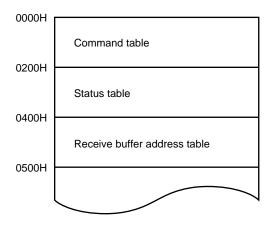

|        | 2.5.6 External memory table configuration example                       | 45 |

| CHAPTE | ER 3 COMMUNICATION OPERATIONS                                           | 47 |

| 3.1    | Initial Settings                                                        |    |

| 3.2    | Start of Communication Control Operation and Flag Synchronization Setup | 48 |

|        | 3.2.1 Transmit operation                                                | 48 |

|        | 3.2.2 Receive operation                                                 | 48 |

|        | 3.2.3 Status reporting                                                  | 48 |

| 3.3    | Data Transmission                                                       | 49 |

|        | 3.3.1 Transmission timing                                               | 49 |

|        | 3.3.2 Linkage of transmit data                                          | 49 |

|        | 3.3.3 Transmit buffer chain                                             | 50 |

|        | 3.3.4 Transmission underrun                                             | 50 |

| 3.4    | Data Reception                                                          | 51 |

|        | 3.4.1 Reception timing                                                  | 51 |

|        | 3.4.2 Separation of receive data                                        | 53 |

|        | 3.4.3  | Receive buffer chain                                                 | 53  |

|--------|--------|----------------------------------------------------------------------|-----|

|        | 3.4.4  | Address field recognition                                            | 53  |

|        | 3.4.5  | Discarding of abnormal frames                                        | 53  |

|        | 3.4.6  | Idle monitor timer                                                   | 54  |

|        | 3.4.7  | Idle reception count                                                 | 54  |

|        | 3.4.8  | Cautions regarding overrun errors                                    | 55  |

| 3.5    | Com    | pletion of Transmit/Receive Operation                                | 58  |

| 3.6    | Trans  | smit and Receive Frame Flags                                         | 58  |

|        | 3.6.1  | Transmit frame flags                                                 | 58  |

|        | 3.6.2  | Receive frame flags                                                  | 58  |

| 3.7    | Gene   | eral-purpose Input/Output Pins                                       | 58  |

|        | 3.7.1  | Detection of changes in general-purpose input pins                   | 58  |

|        | 3.7.2  | Control of general-purpose output pins                               | 58  |

|        | 3.7.3  | General-purpose input/output pin status                              | 58  |

| CHAPTE | R 4 C  | OMMANDS (LCW)                                                        | 59  |

| СНАРТЕ | R 5 S  | TATUS (LSW)                                                          | 87  |

| CHAPTE | R 6 S  | YSTEM CONFIGURATION EXAMPLES                                         | 113 |

| 6.1    | Conr   | nection with Host System                                             | 113 |

|        | 6.1.1  | Local memory type                                                    |     |

|        | 6.1.2  | Main memory type                                                     | 114 |

| 6.2    | Phys   | ical Interface Examples                                              |     |

|        | 6.2.1  | Interface example using RS-485                                       |     |

|        | 6.2.2  | Interface example using μPD98201                                     |     |

| APPEND | ΙΧΑ μ  | PD72103A OPERATION SEQUENCE EXAMPLES                                 | 117 |

| APPEND | IX B ( | CONNECTION BETWEEN HDLC CONTROLLER AND MOTOROLA SYSTEM               | 119 |

| B.1    | Diffe  | rences between NEC/Intel Buses and Motorola Buses                    | 119 |

|        | B.1.1  | Difference in allocation of physical even-numbered byte              |     |

|        |        | and odd-numbered byte in 16-bit bus                                  | 119 |

|        |        | Difference in representation order of logical 16-bit and 24-bit data |     |

| B.2    | Meth   | od for Connecting HDLC Controller with Motorola-based System         | 120 |

|        | B.2.1  | Data bus connection in hardware                                      | 120 |

|        | B.2.2  | HDLC controller's MDST command setting (operation mode setting LCW)  | 120 |

| APPEND | IX C   | QUESTIONS AND ANSWERS ABOUT THE $\mu$ PD72103A                       | 121 |

| APPEND | IX D ( | COMMAND LIST                                                         | 161 |

| ADDEND | IV F ( | STATUS LIST                                                          | 400 |

# LIST OF FIGURE

| Figure No. | Title                                                                     | Page |

|------------|---------------------------------------------------------------------------|------|

| 2-1        | Control Register                                                          | 14   |

| 2-2        | Internal Status Register                                                  | 15   |

| 2-3        | Basic Clocks in One Bus Cycle during Block Transfer                       | 16   |

| 2-4        | Example: Two Programmable Waits                                           | 17   |

| 2-5        | Memory Write Timing                                                       | 18   |

| 2-6        | Memory Read Timing                                                        | 19   |

| 2-7        | Byte Mode ( $\overline{B}/W = 0$ )                                        | 20   |

| 2-8        | Word Mode $(\overline{B}/W = 1)$                                          | 21   |

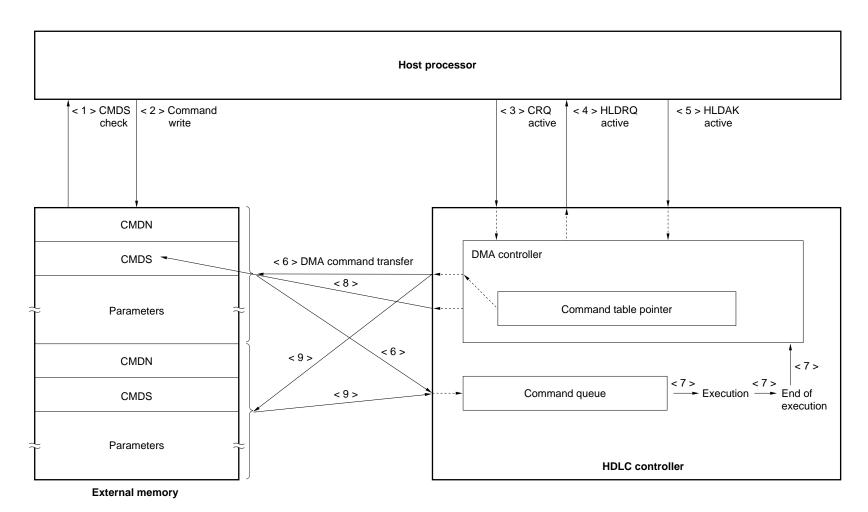

| 2-9        | Command/Status Handling between μPD72103A and Host Processor              | 22   |

| 2-10       | Flow Chart for Writing "Memory Area Setting LCW" Command to Internal FIFO | 24   |

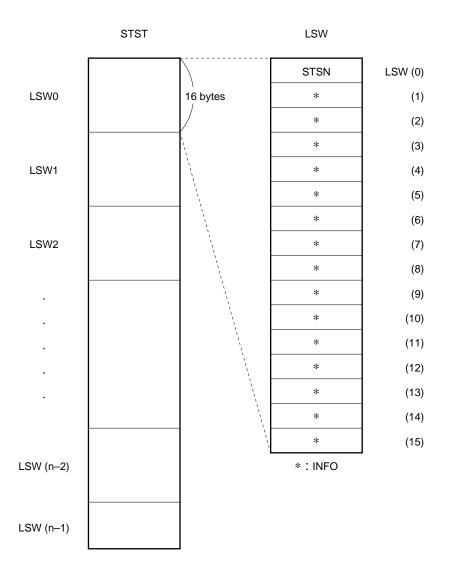

| 2-11       | Status Report (when Status Area is LSW0 to LSW2)                          | 26   |

| 2-12       | Command Table                                                             | 28   |

| 2-13       | Command Fetch Operation                                                   | 30   |

| 2-14       | Status Table                                                              | 32   |

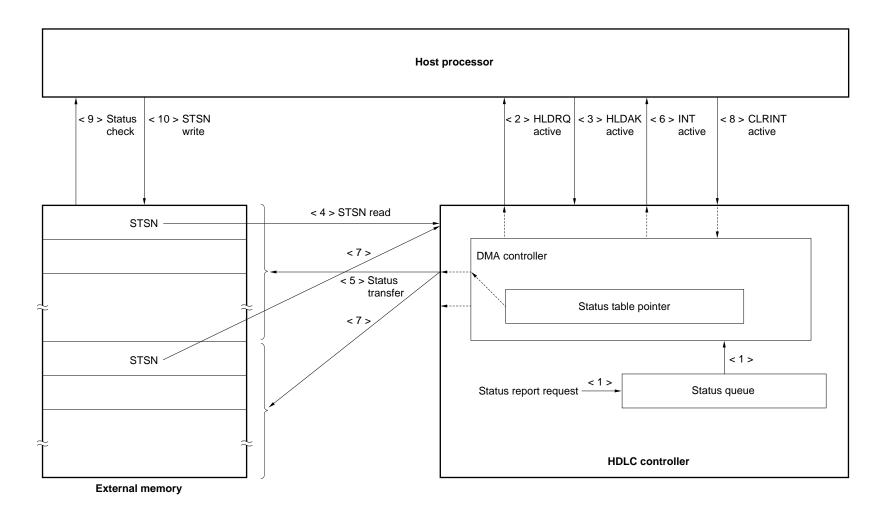

| 2-15       | Status Information Operations                                             | 34   |

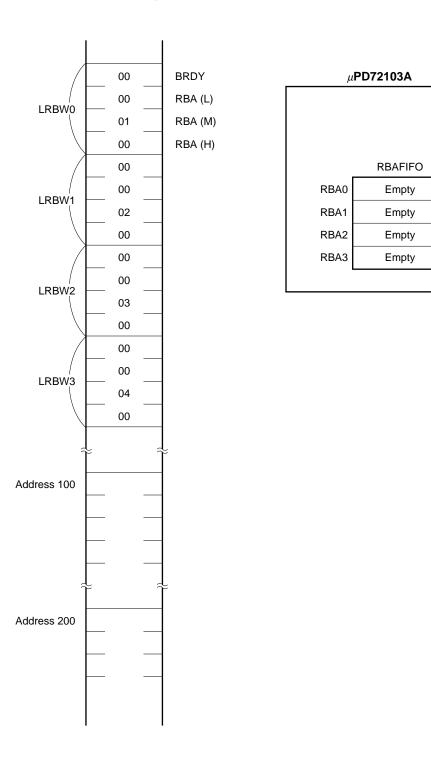

| 2-16       | Receive Buffer Address Table                                              | 36   |

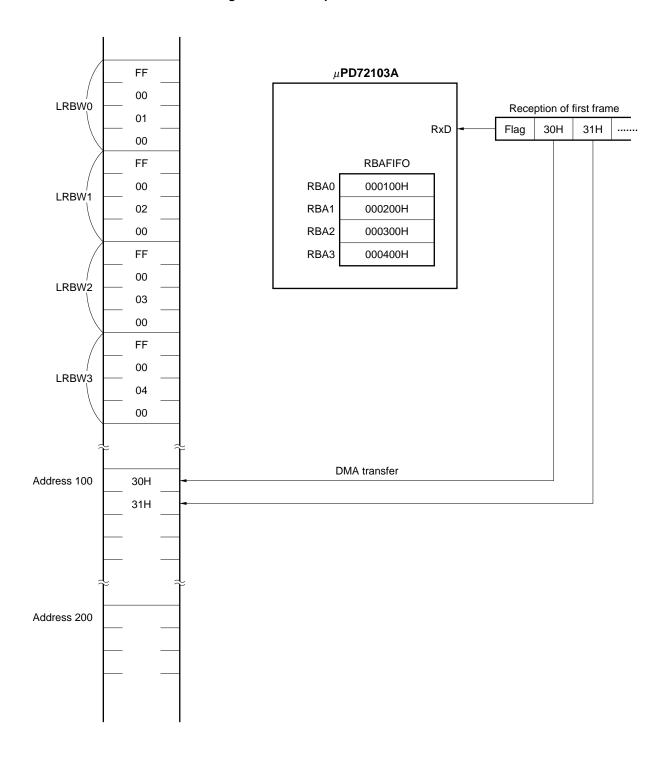

| 2-17       | Initial Status (Line Closed)                                              | 38   |

| 2-18       | After Line Open Command Is Issued                                         | 39   |

| 2-19       | RBAFIFO Full Status                                                       | 40   |

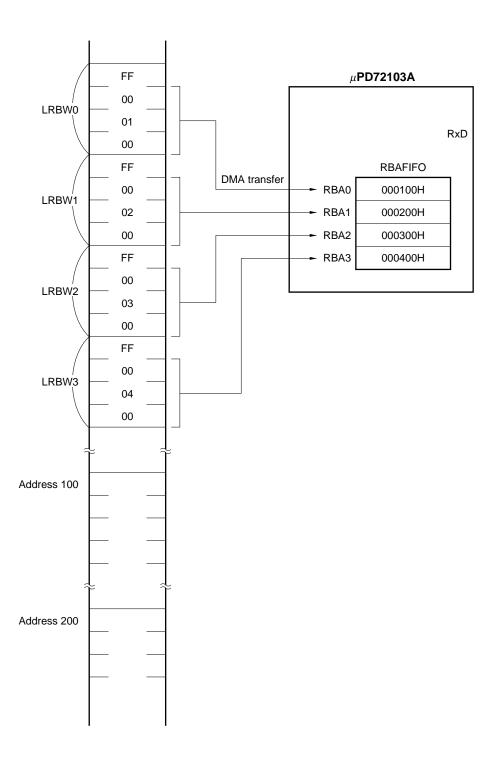

| 2-20       | Reception of First Frame                                                  | 41   |

| 2-21       | Completion of First Frame Reception (FCS Error)                           | 42   |

| 2-22       | Start of Second Frame Reception                                           | 43   |

| 2-23       | Completion of Second Frame Reception                                      | 44   |

| 2-24       | External Memory Configuration Example                                     | 45   |

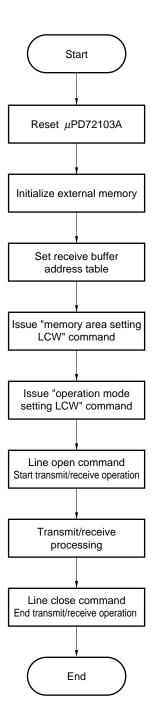

| 3-1        | Initialization Steps for μPD72103A and External Memory                    | 47   |

| 3-2        | Transmission Timing                                                       | 49   |

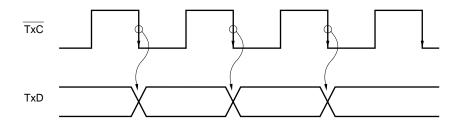

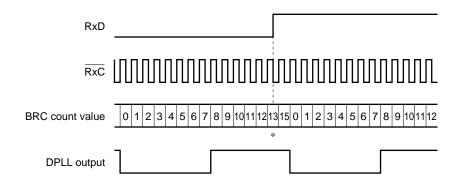

| 3-3        | Reception Timing (External Clock Mode)                                    | 51   |

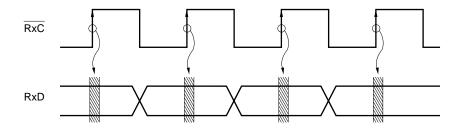

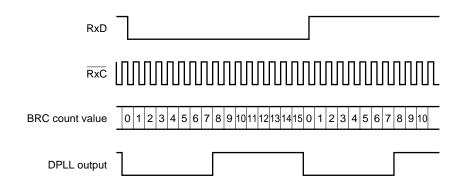

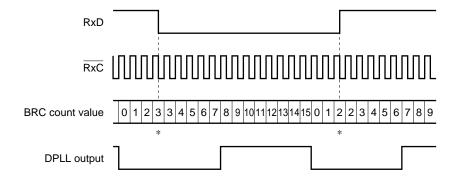

| 3-4        | Reception Timing (DPLL Mode)                                              | 52   |

| 3-5        | Idle Reception Count                                                      | 54   |

| 6-1        | $\mu$ PD72103A System Configuration Example (Local Memory Type)           | 113  |

| 6-2        | $\mu$ PD72103A System Configuration Example (Main Memory Type)            |      |

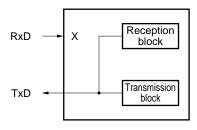

| 6-3        | Two-wire Interface Example                                                | 115  |

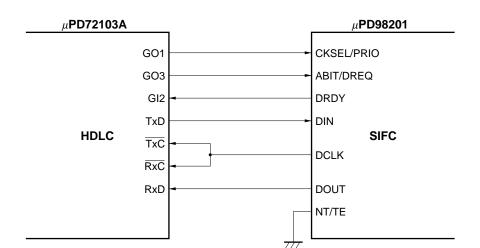

| 6-4        | Connection Example with ISDN LSI (connection with SIEC [uPD98201])        | 115  |

# LIST OF TABLE

| Table No. | Title                                                   | Page |

|-----------|---------------------------------------------------------|------|

| 1-1       | Pin Status after Reset                                  | 11   |

| 2-1       | I/O Port Map                                            | 13   |

| 2-2       | Control Register                                        |      |

| 2-3       | Internal Status Register                                | 15   |

| 2-4       | Bus Cycles in Byte Transfer Mode and Word Transfer Mode | 16   |

| 2-5       | Command Fields                                          | 29   |

| 2-6       | Status Fields                                           | 33   |

| 2-7       | Receive Buffer Address Fields                           | 37   |

| 2-8       | External Memory Table Configuration Example             | 45   |

| 3-1       | Reception Timing Mode Settings                          | 51   |

| C-1       | Question Categories                                     | 121  |

| D-1       | COMMAND LIST                                            | 161  |

| F-1       | STATUS LIST                                             | 163  |

#### **CHAPTER 1 GENERAL**

The  $\mu$ PD72103A HDLCC (High-level Data Link Control procedure Controller) is a communication control LSI that supports the HDLC standard.

Because this HDLCC includes a DMA (Direct Memory Access) function, the host machine can use commands and data previously stored in memory to perform serial communication using HDLC frames.

#### 1.1 Features

- · HDLC frame control

- Address field recognition function: 1 byte/2 bytes

- Full-duplex communication via one channel

- Baud rate: 8 Mbps max. (2 Mbps max. when using DPLL) Note

- Maximum transmit/receive data length: 16 Kbytes

- Can be divided in external memory as level-two header and 1 field or level-two, level-three header and user

- · Various statistical data

- DPLL (Digital Phase-Locked Loop) function

- On-chip DMA controller: 8/16-bit data, 24-bit address

- General-purpose input/output pins: Input pin x 2

Output pin x 2

- On-chip transmission control function (LAP-D mode)

- Data format: NRZ and NRZI decoding/encoding

- · Command chain function

- FCS (Frame Check Sequence) generation/detection: 16/32 bits

- System clock: 1 to 16 MHz

- CMOS

- 5-V single power supply

**Note** Transfer speed is restricted by the system clock's frequency and operation conditions. For details, see the caution points described in "3.4.8 Cautions regarding overrun errors".

#### ORDERING INFORMATION

| Part No.         | Package                            |

|------------------|------------------------------------|

| μPD72103AGC-3B9  | 80-pin plastic QFP (14 x 14 mm)    |

| $\mu$ PD72103ALP | 68-pin plastic QFJ (950 x 950 mil) |

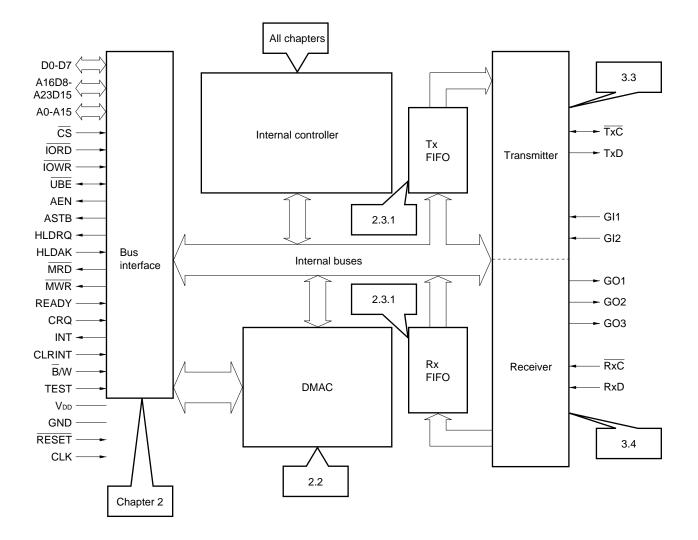

# 1.2 Block Diagram

Corresponding sections of this manual are indicated in the bubbles.

# 1.3 Internal Block Functions

| Name                                         | Function                                                                                                                                                                        |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus interface                                | Interface between the $\mu\text{PD72103A}$ and external memory or external host processor                                                                                       |

| Internal controller                          | HDLC framing including the DMAC, transmitter, and receiver block control                                                                                                        |

| DMAC<br>(Direct Memory<br>Access Controller) | Controls transfer of data in external memory to the internal controller or transmitter, or controls writing of data to external memory from the internal controller or receiver |

| Tx FIFO                                      | A 32-byte buffer for transmitting transmit data from the DMAC to the transmitter                                                                                                |

| Rx FIFO                                      | A 128-byte buffer for transmitting receive data from the receiver to the DMAC                                                                                                   |

| Transmitter                                  | Converts contents of TX FIFO to HDLC frames that are sent as serial data                                                                                                        |

| Receiver                                     | Writes data received in HDLC frames to RX FIFO                                                                                                                                  |

| Internal buses                               | These buses, which include a 24-bit address bus and 8/16-bit data buses, connect the internal controller, DMAC, FIFOs, serial block, and bus interface block                    |

4

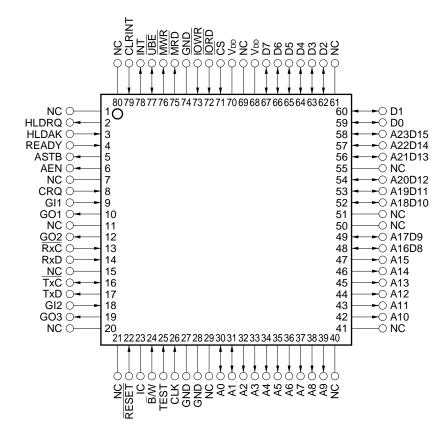

#### 1.4 Pin Configuration (Top View)

#### 80-pin plastic QFP (14 x 14 mm)

μPD72103AGC-3B9

#### 68-pin plastic QFJ (950 x 950 mil)

$\mu$ PD72103ALP

# 1.5 Pin Functions

| Р             | in No.        | Pin name                  | I/O | Active | Function                                                                                                                                                                           |

|---------------|---------------|---------------------------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80-pin<br>QFP | 68-pin<br>QFJ |                           |     | level  |                                                                                                                                                                                    |

| 12            | 2             | GO2                       | 0   | _      | This is a general-purpose output pin. The output level of this pin is changed when "general-purpose output pin write LCW" is executed.                                             |

| 13            | 3             | RxC<br>(Receive Clock)    | I   | _      | When in on-chip DPLL mode: This is the transmit/receive clock input for the $\mu$ PD72103A's on-chip DPLL. (Enables input up to 32 MHz)                                            |

|               |               |                           |     |        | When in external DPLL mode:  This is a receive clock input pin.                                                                                                                    |

| 14            | 4             | RxD<br>(Receive Data)     | I   | -      | This is a serial receive data input pin.                                                                                                                                           |

| 15            | 5             | NC<br>(No Connection)     | -   | _      | Leave this pin unconnected.                                                                                                                                                        |

| 16            | 6             | TxC<br>(Transmit Clock)   | I/O | -      | When in on-chip DPLL mode:  The $\overline{\text{RxC}}$ pin's input signal that was generated in the $\mu$ PD72103A is divided by 16 and output via this pin as a clock signal.    |

|               |               |                           |     |        | When in external DPLL mode:  A transmit clock is input via this pin from an external source.                                                                                       |

| 17            | 7             | TxD<br>(Transmit Data)    | 0   | -      | This is the serial transmit data output pin.                                                                                                                                       |

| 18            | 8             | GI2                       | I   | L      | When not in LAP-D mode: This is a general-purpose input pin. "General-purpose input pin status change detection 1 LSW" is reported when a change in the input level is detected.   |

|               |               |                           |     |        | When in LAP-D mode: This pin is used for externally applied frame transmit enable signals.                                                                                         |

| 19            | 9             | GO3                       | 0   | L      | When not in LAP-D mode: This pin has no function. Leave this pin unconnected.                                                                                                      |

|               |               |                           |     |        | When in LAP-D mode:  This pin is used for externally output frame transmit request signals.                                                                                        |

| 20            | -             | NC<br>(No Connection)     | -   | -      | Leave this pin unconnected.                                                                                                                                                        |

| 21            | -             | NC<br>(No Connection)     | _   | -      | Leave this pin unconnected.                                                                                                                                                        |

| 22            | 10            | RESET<br>(Reset)          | I   | L      | This pin is used to initialize (reset) the $\mu$ PD72103A's internal circuits. This requires at least seven clock cycles of the CLK signal. Bus slave mode is entered after reset. |

| -             | _             | NC<br>(No Connection)     | ı   | _      | Leave this pin unconnected.                                                                                                                                                        |

| 23            | 11            | IC (Internally Connected) | _   | -      | Do not connect anything to this pin.                                                                                                                                               |

| P             | in No.        | Pin name              | I/O      | Active | Function                                                                                                                                                                                                                                                                                                                              |  |

|---------------|---------------|-----------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 80-pin<br>QFP | 68-pin<br>QFJ |                       |          | level  |                                                                                                                                                                                                                                                                                                                                       |  |

| 24            | 12            | B/W<br>(Byte/Word)    | ı        | L/H    | During bus master mode, this indicates the data bus used to access external memory.  When B/W = 0: byte unit (8 bits)  When B/W = 1: word unit (16 bits)  The status of the B/W pin should be fixed after power-on.  When accessing in word units, the low-order bits in the data bus are the data contents of even-number addresses. |  |

| 25            | 13            | TEST<br>(Text)        | I        | -      | When using this pin, it should be pulled up to high level.                                                                                                                                                                                                                                                                            |  |

| 26            | 14            | CLK<br>(Clock)        | I        | _      | System clock input Input a 1-MHz to 16-MHz clock to this pin. Note                                                                                                                                                                                                                                                                    |  |

| 27            | 15            | GND                   | -        | _      | Ground pins  Make sure that there are several ground pins.                                                                                                                                                                                                                                                                            |  |

| 28            | 16            | GND                   | -        | _      | Ground pins  Make sure that there are several ground pins.                                                                                                                                                                                                                                                                            |  |

| 29            | _             | NC<br>(No Connection) | -        | _      | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                           |  |

| 30 and 31     | 17 and 18     | A0 and A1             | I/O<br>* | -      | Bi-directional 3-state Indicates the low-order two bits of the memory address line access address.                                                                                                                                                                                                                                    |  |

|               |               |                       |          |        | During bus slave mode: (input)  These pins are used to input addresses during I/O access to the $\mu$ PD72103A by an external host.                                                                                                                                                                                                   |  |

| 32 to 39      | 19 to 26      | A2 to A9              | O<br>*   | -      | During bus master mode: Outputs memory addresses from 2 bits to 15 bits.                                                                                                                                                                                                                                                              |  |

|               |               |                       |          |        | During bus slave mode: Changes to high impedance.                                                                                                                                                                                                                                                                                     |  |

| 40            | -             | NC<br>(No Connection) | -        | -      | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                           |  |

| 41            | -             | NC<br>(No Connection) |          | -      | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                           |  |

| 42 to 47      | 27 to 32      | A10 to A15            | O<br>*   | -      | See "A2 to A9" above.                                                                                                                                                                                                                                                                                                                 |  |

| 48 and 49     | 33 and 34     | A16D8 and A17D9       | I/O<br>* | -      | These pins are for the bi-directional 3-state/data bus. They are multiplex pins for high-order 8 bits starting from bits 16 to 23 of an address and for high-order 8 bits starting from bits 8 to 15 of the data.                                                                                                                     |  |

| 50            | 35            | NC<br>(No Connection) | -        | -      | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                           |  |

| 51            | -             | NC<br>(No Connection) | -        | -      | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                           |  |

| 52 to 54      | 36 to 38      | A18D10 to A20D12      | I/O<br>* | _      | See "A16D8 and A17D9" above.                                                                                                                                                                                                                                                                                                          |  |

Note See the caution points described in "3.4.8 Cautions regarding overrun errors".

Remark "\*" indicates 3-state.

| Р             | in No.        | Pin name              | I/O      | Active |                                                                                                                                                                                   | Function                                                                                                                                                                                  |

|---------------|---------------|-----------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80-pin<br>QFP | 68-pin<br>QFJ |                       |          | level  |                                                                                                                                                                                   |                                                                                                                                                                                           |

| 55            | -             | NC<br>(No Connection) | -        | _      | Leave this pin                                                                                                                                                                    | unconnected.                                                                                                                                                                              |

| 56 to 58      | 39 to 41      | A21D13 to A23D15      | I/O<br>* | _      | See "A16D8 a                                                                                                                                                                      | nd A17D9" above.                                                                                                                                                                          |

| 59 and 60     | 42 and 43     | D0 and D1             | I/O<br>* | -      | Bi-directional<br>3-state<br>address line                                                                                                                                         | During bus master mode:  This pin is an output pin during write to external memory and is an input pin during read from external memory.                                                  |

|               |               |                       |          |        |                                                                                                                                                                                   | During bus slave mode: This pin is normally set to high impedance. It is used to output internal register data when an external host processor executes I/O read from the $\mu$ PD72103A. |

| 61            | -             | NC<br>(No Connection) | -        | _      | Leave this pin                                                                                                                                                                    | unconnected.                                                                                                                                                                              |

| 62 to 67      | 44 to 49      | D2 to D7              | I/O<br>* | -      | See D0 and D                                                                                                                                                                      | 1                                                                                                                                                                                         |

| 68            | 50            | V <sub>DD</sub>       | -        | -      | +5-V power su                                                                                                                                                                     | pply pin                                                                                                                                                                                  |

| 69            | -             | NC<br>(No Connection) | -        | -      | Leave this pin                                                                                                                                                                    | unconnected.                                                                                                                                                                              |

| 70            | 51            | V <sub>DD</sub>       | _        | -      | +5-V power su                                                                                                                                                                     | pply pin                                                                                                                                                                                  |

| 71            | 52            | CS<br>(Chip Select)   | I        | L      | During bus ma<br>Disable this                                                                                                                                                     |                                                                                                                                                                                           |

|               |               |                       |          |        | During bus sla<br>Read/write o<br>is low.                                                                                                                                         | ve mode:<br>operation from host processor is enabled when this pin                                                                                                                        |

| 72            | 53            | IORD<br>(I/O Read)    | I        | L      | μPD72103A's i                                                                                                                                                                     | st processor uses this pin to read the contents of the internal registers. uster mode: n (by inputting a high-level signal).                                                              |

| 73            | 54            | IOWR<br>(I/O Write)   | I        | L      | An external host processor uses this pin to write data to the $\mu$ PD72103A's internal registers.  During bus master mode:  Disable this pin (by inputting a high-level signal). |                                                                                                                                                                                           |

| 74            | 55            | GND                   | -        | -      | Ground pins<br>Make sure that                                                                                                                                                     | t there are several ground pins.                                                                                                                                                          |

| 75            | 56            | MRD<br>(Memory Read)  | O<br>*   | L      | During bus ma<br>Data is read                                                                                                                                                     | ster mode:<br>I from external memory when this pin is low.                                                                                                                                |

|               |               |                       |          |        | During bus sla<br>This pin goe                                                                                                                                                    | ve mode:<br>es to high impedance.                                                                                                                                                         |

| 76            | 57            | MWR<br>(Memory Write) | O<br>*   | L      | During bus ma<br>Data is writte                                                                                                                                                   | ster mode:<br>en to external memory when this pin is low.                                                                                                                                 |

|               |               |                       |          |        | During bus sla<br>This pin goe                                                                                                                                                    | ve mode:<br>es to high impedance.                                                                                                                                                         |

Remark "\*" indicates 3-state.

| Р             | in No.        | Pin name                    | I/O      | Active | Function                                                                                                                                                                                                                                                                                            |

|---------------|---------------|-----------------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80-pin<br>QFP | 68-pin<br>QFJ |                             |          | level  |                                                                                                                                                                                                                                                                                                     |

| 77            | 58            | UBE<br>(Upper Byte Enable)  | I/O<br>* | L/H    | During bus master mode: The signal that is output from this pin varies depending on the input value of the B/W pin.  Byte transfer mode (B/W = 0) UBE is always high impedance.  Word transfer mode (B/W = 1) Indicates whether valid data is present at pins D0 to D7 and/or pins A16D8 to A23D15. |

|               |               |                             |          |        | UBE         A0         D0-D7         A16D8-A23D15                                                                                                                                                                                                                                                   |

|               |               |                             |          |        | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                             |

|               |               |                             |          |        | During bus slave mode:  The UBE pin is used for input and indicates whether valid data is present at pins D0 to D7 and/or pins A16D8 to A23D15.                                                                                                                                                     |

|               |               |                             |          |        | UBE         A0         D0-D7         A16D8-A23D15           0         0         √         —           0         0         1         √                                                                                                                                                               |

|               |               |                             |          |        | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                             |

| 78            | 59            | INT<br>(Interrupt)          | 0        | Н      | Interrupt signal from the $\mu$ PD72103A to an external host processor.                                                                                                                                                                                                                             |

| 79            | 60            | CLRINT<br>(Clear Interrupt) | I        | Н      | This pin's signal sets as inactive the INT signal that is output by the $\mu$ PD72103A. In the $\mu$ PD72103A, the INT signal goes low at this signal's rising edge.                                                                                                                                |

| 80            | _             | NC<br>(No Connection)       | -        | _      | Leave this pin unconnected.                                                                                                                                                                                                                                                                         |

| 1             | -             | NC<br>(No Connection)       | _        | _      | Leave this pin unconnected.                                                                                                                                                                                                                                                                         |

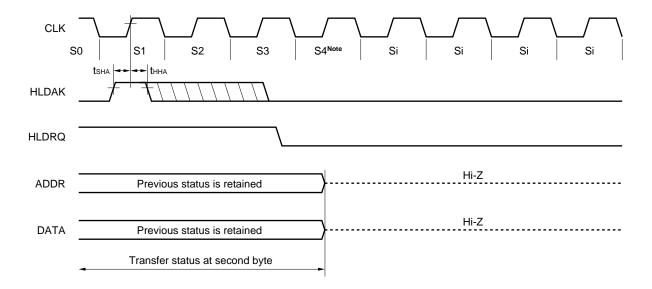

| 2             | 61            | HLDRQ<br>(Hold Request)     | 0        | Н      | This pin is for the hold request signal, which is issued to an external host processor. During a DMA operation in the $\mu$ PD72103A, this signal is active in order to switch from bus slave mode to bus master mode.                                                                              |

| 3             | 62            | HLDAK<br>(Hold Acknowledge) | I        | Н      | This pin is for the hold acknowledge signal, which is received from an external host processor. When the $\mu$ PD72103A detects that this signal is active, it begins the DMA operation after switching from bus slave mode to bus master mode.                                                     |

Remark "\*" indicates 3-state.

| Pir           | n No.         | Pin name                 | I/O | Active | Function                                                                                                                                                                                                                                                |

|---------------|---------------|--------------------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80-pin<br>QFP | 68-pin<br>QFJ |                          |     | level  |                                                                                                                                                                                                                                                         |

| 4             | 63            | READY<br>(Ready)         | 1   | Н      | This is an input pin for the signal that is used to extend the width of the MRD and MWR signals.  When the READY signal is low, the MRD and MWR signals are held at active low level.  Change the READY signal to conform to the rated setup/hold time. |

| 5             | 64            | ASTB<br>(Address Strobe) | 0   | Н      | This pin is used to externally latch addresses output by the $\mu$ PD72103A.                                                                                                                                                                            |

| 6             | 65            | AEN<br>(Address Enable)  | 0   | Н      | During bus master mode, this pin's signal enables latched high-order addresses, which are output via the system address bus.  This signal is also used to inhibit other system bus drivers.                                                             |

| 7             | _             | NC<br>(No Connection)    | -   | _      | Leave this pin unconnected.                                                                                                                                                                                                                             |

| 8             | 66            | CRQ<br>(Command Request) | I   | Н      | This pin's signal is used to request command execution from an external host processor to the $\mu$ PD72103A. The $\mu$ PD72103A fetches the command from external memory at the rising edge of this signal.                                            |

| 9             | 67            | GI1                      | I   | L      | This is a general-purpose input pin. The "general-purpose input pin change detection 1 LSW" is reported when a change in the input level is detected.                                                                                                   |

| 10            | 68            | GO1                      | 0   | L      | This is a general-purpose output pin. The output level of this pin is changed when the "general-purpose output pin write LCW" command is executed.                                                                                                      |

| 11            | 1             | NC<br>(No Connection)    | -   | _      | Leave this pin unconnected.                                                                                                                                                                                                                             |

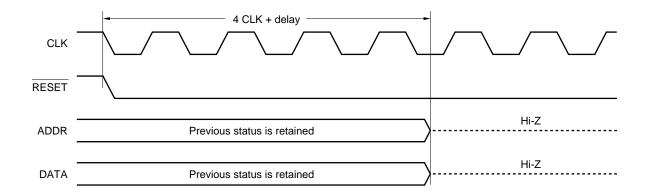

#### 1.6 Initialization via Reset

The  $\mu$ PD72103A is initialized when a negative potential pulse that is longer than the pulse input to the CLK pin (which is seven clocks in length as set by system clock conversion) is input to the  $\overline{\text{RESET}}$  pin, or when a "1" is written to the CRST bit in the control register.

Table 1-1 lists the status of output pins and input/output pins when the  $\mu$ PD72103A is reset.

Since the RESET signal is latched by the CLK signal, four clocks of the CLK signal are required before the reset status becomes as shown in Table 1-1.

Table 1-1. Pin Status after Reset

| Pin No.                    |                  | Pin name     | I/O            | During reset              |

|----------------------------|------------------|--------------|----------------|---------------------------|

| 80-pin QFP                 | 68-pin QFJ       |              |                | (same status after reset) |

| 12                         | 2                | GO2          | 0              | Н                         |

| 16                         | 6                | TxC          | I/O            | Hi-Z                      |

| 17                         | 7                | TxD          | 0              | Н                         |

| 19                         | 9                | GO3          | 0              | н                         |

| 30, 31                     | 17, 18           | A0, A1       | I/O<br>3-state | Hi-Z                      |

| 32-39,<br>42-47            | 19-26,<br>27-32  | A2-A15       | O<br>3-state   | Hi-Z                      |

| 48, 49,<br>52-54,<br>56-58 | 33, 34,<br>36-41 | A16D8-A23D15 | I/O<br>3-state | Hi-Z                      |

| 59, 60,<br>62-67           | 42-49            | D0-D7        | I/O<br>3-state | Hi-Z                      |

| 75                         | 56               | MRD          | O<br>3-state   | Hi-Z                      |

| 76                         | 57               | MWR          | O<br>3-state   | Hi-Z                      |

| 77                         | 58               | ÜBE          | I/O<br>3-state | Hi-Z                      |

| 78                         | 59               | INT          | 0              | L                         |

| 2                          | 61               | HLDRQ        | 0              | L                         |

| 5                          | 64               | ASTB         | 0              | L                         |

| 6                          | 65               | AEN          | 0              | L                         |

| 10                         | 68               | GO1          | 0              | Н                         |

[MEMO]

#### **CHAPTER 2 BUS INTERFACE**

# 2.1 Internal Registers

The  $\mu$ PD72103A includes four internal registers. These registers are controlled via six pins:  $\overline{\text{IORD}}$ ,  $\overline{\text{IOWR}}$ , A0, A1,  $\overline{\text{UBE}}$ , and  $\overline{\text{CS}}$ . The host processor can only have I/O access to the  $\mu$ PD72103A when the  $\mu$ PD72103A is in bus slave mode.

Table 2-1 shows an I/O port map (for details of the UBE pin, see UBE column in "1.5 Pin Functions").

Table 2-1. I/O Port Map

| CS | IORD | IOWR | A1 | A0 | Internal register             | Function                                                                                     |

|----|------|------|----|----|-------------------------------|----------------------------------------------------------------------------------------------|

| 1  | Х    | Х    | Х  | Х  | _                             | No function                                                                                  |

| 0  | 1    | 0    | 0  | 0  | Control register              | Write                                                                                        |

| 0  | 0    | 1    | 0  | 0  | Internal status register      | Read                                                                                         |

| 0  | 1    | 0    | 0  | 1  | Internal FIFO active register | When "5" is written to this register, the MSET command is written to the internal FIFO. Note |

| 0  | 1    | 0    | 1  | 0  | _                             | Setting inhibited (internal test mode)                                                       |

| 0  | 1    | 0    | 1  | 1  | Internal FIFO register        | The MSET command is written to the internal FIFO.                                            |

| 0  | 0    | 1    | 1  | 1  | -                             | Setting inhibited                                                                            |

Note See "CHAPTER 4 COMMANDS (LCW)"

Remark X: Don't care

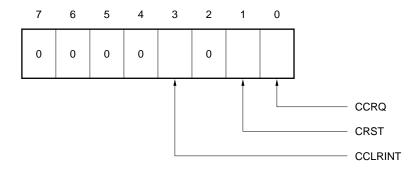

# 2.1.1 Control register

The control register is used when the host processor accesses the  $\mu PD72103A$ .

Figure 2-1. Control Register

Caution Be sure to write "0" to bits 2, 4, 5, 6, and 7.

Table 2-2. Control Register

| Bit name | Meaning                       | Function                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCRQ     | Control<br>Command<br>Request | A command is executed when "1" is written to this bit. The command execution method for this operation is the same as for the CRQ pin. Either method can be selected by host processor. Since this bit is automatically cleared to zero internally, there is no need to write a "0" after the host processor has written a "1" to this bit.                         |

| CRST     | Control<br>Reset              | The $\mu$ PD72103A's internal circuits are automatically reset when a "1" is written to this bit. This reset operation is the same as that controlled via the $\overline{RESET}$ pin. Since this bit is automatically cleared to zero internally, there is no need to write a "0" after the host processor has written a "1" to this bit.                           |

| CCLRINT  | Control<br>Clear<br>INT       | The INT pin is automatically reset when a "1" is written to this bit. This function is the same as when the INT pin is reset by the CLRINT pin. It does not matter which pin is selected by the host processor. Since this bit is automatically cleared to zero internally, there is no need to write a "0" after the host processor has written a "1" to this bit. |

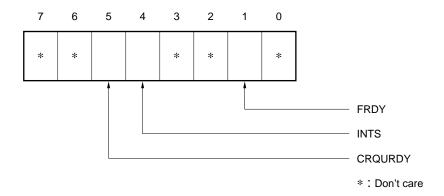

# 2.1.2 Internal status register

The internal status register is used to indicate the internal status of the  $\mu$ PD72103A. Its value immediately after reset is 0CH.

Figure 2-2. Internal Status Register

Table 2-3. Internal Status Register

| Bit name | Meaning                       | Function                                                                                                                                                                                                                                                                         |  |

|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FRDY     | FIFO<br>Ready                 | This bit is accessed when the "memory area setting LCWNote" command is written to the internal FIFO. Write is enabled when this bit's value is "0". If this bit's value is "1", wait until it becomes "0" before writing to the FIFO.  The value of this bit after reset is "0". |  |

| INTS     | INT<br>Status                 | This is the same signal as for the INT pin. The host processor can be informed of the status report timing from the $\mu$ PD72103A not only by interrupts via the INT pin but also by polling this bit. The value of this bit after reset is "0".                                |  |

| CRQURDY  | Command<br>Request<br>Unready | After the "memory area setting LCW" command is issued, this bit value becomes zero and a 10-ms wait period (when system clock = 8 MHz) is required before the next command can be issued.  The value of this bit after reset is "0".                                             |  |

Note LCW: Link Command Word

#### 2.2 DMAC (Direct Memory Access Controller)

During bus master mode, the  $\mu$ PD72103A uses the on-chip DMAC to read certain commands or transmit data that is stored in external memory or to write internal status contents or receive data to external memory.

Addresses used for DMA are 24 bits long, and the data length is selectable via the  $\overline{B}/W$  pin to support either 8-bit or 16-bit memory.

#### 2.2.1 Block transfers

The  $\mu$ PD72103A uses DMA transfers to transfer long data segments. In the  $\mu$ PD72103A, DMA sets the HLDRQ signal as active (high) after each block is transferred.

DMA transfers can be executed in either 4-byte or 8-byte blocks as set by DMAB<sup>Note</sup>, and one bus cycle (four clocks) transfers either one byte (8 bits: byte unit) or two bytes (16 bits: word unit) of data. Accordingly, the number of bus cycles is determined by the transfer mode and the number of bytes to be transferred in data blocks, as listed in Table 2-4.

**Note** DMAB is a parameter of the "operation mode setting LCW" command.

Table 2-4. Bus Cycles in Byte Transfer Mode and Word Transfer Mode

| Bytes per block | Byte transfer mode | Word transfer mode                             |

|-----------------|--------------------|------------------------------------------------|

| 4 bytes/block   | 4 bus cycles       | 2 bus cycles (when starting from even address) |

| (DMAB = 0)      |                    | 3 bus cycles (when starting from odd address)  |

| 8 bytes/block   | 8 bus cycles       | 4 bus cycles (when starting from even address) |

| (DMAB = 1)      |                    | 5 bus cycles (when starting from odd address)  |

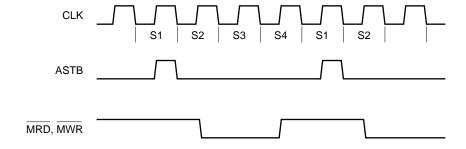

Figure 2-3. Basic Clocks in One Bus Cycle during Block Transfer

#### 2.2.2 Extension of active (low-level) width of MRD and MWR signals

The basic number of clocks per bus cycle in the  $\mu$ PD72103A's DMA is four clocks. During DMA transfer, the active (low-level) width of the  $\overline{\text{MRD}}$  and  $\overline{\text{MWR}}$  signals is two clocks. Either of the following methods can be used when there is not enough memory for a two-clock width.

#### (1) Programmable wait function

This function causes the  $\mu$ PD72103A to internally and automatically insert wait cycles to extend the active (low-level) width of  $\overline{\text{MRD}}$  and  $\overline{\text{MWR}}$ . The programmable wait value can also be set via a parameter (DMAW) in the "operation mode setting LCW" command.

Figure 2-4 shows an example in which the programmable wait value is "2".

#### (2) Control via READY signal

This method sets the externally applied READY signal to low level to extend the active (low-level) width of  $\overline{\text{MRD}}$  and  $\overline{\text{MWR}}$ . This method is valid when the value set to DMAW is exceeded.

Figure 2-4. Example: Two Programmable Waits

#### 2.2.3 Basic timing of DMA

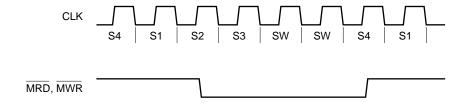

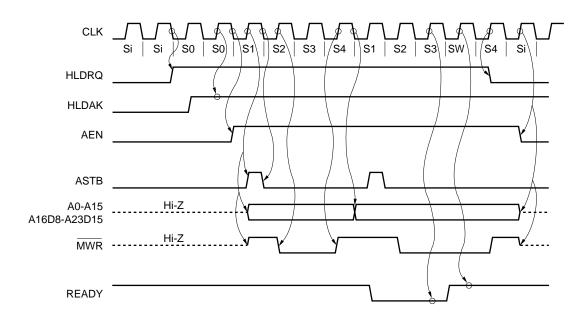

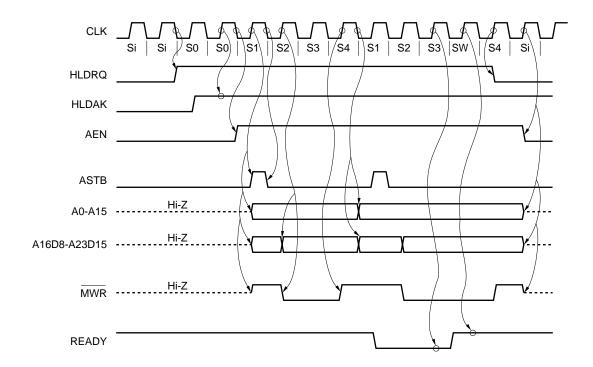

Figure 2-5. Memory Write Timing

# (a) $\overline{B}/W = 0$

# (b) $\overline{B}/W = 1$

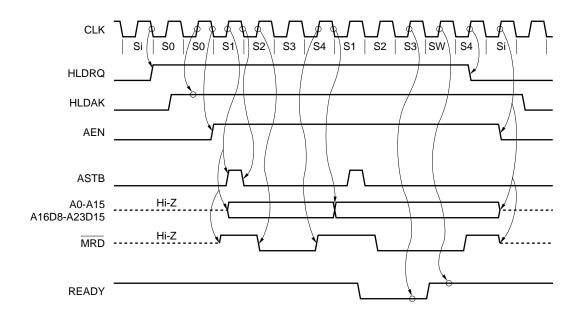

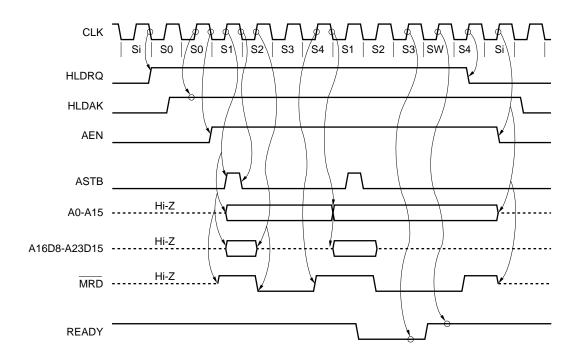

Figure 2-6. Memory Read Timing

# (a) $\overline{B}/W = 0$

# (b) $\overline{B}/W = 1$

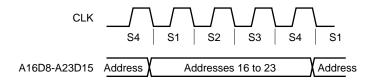

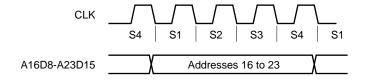

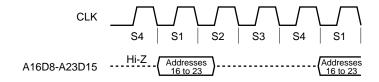

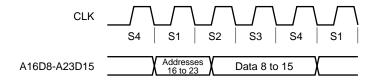

#### 2.2.4 Address/data multiplexing

Addresses and data are multiplexed as shown below.

| Pin             | Address  | Data    |

|-----------------|----------|---------|

| A0 to A15       | 0 to 15  | _       |

| A16D8 to A23D15 | 16 to 23 | 8 to 15 |

| D0 to D7        | -        | 0 to 7  |

This multiplexing method is used to reduce the external address latch.

Therefore, the operation of the pins (A16D8 to A23D15) used for address/data multiplexing varies depending on the value input to the  $\overline{B}/W$  pin.

When external memory is configured using byte mode  $(\overline{B}/W = 0)$ , an external address latch is not required, as is shown in Figure 2-7. When external memory is configured using word mode  $(\overline{B}/W = 1)$ , an external address latch is not required as along as the memory contents do not exceed 64 Kbytes (requiring no more than 16 address pins), as shown in Figure 2-8. When the memory contents exceed 64 Kbytes, an external address latch is required for pins A16D8 to A23D15.

Figure 2-7. Byte Mode  $(\overline{B}/W = 0)$

#### (a) Memory read

#### (b) Memory write

Figure 2-8. Word Mode  $(\overline{B}/W = 1)$

# (a) Memory read

# (b) Memory write

#### 2.3 Interface between $\mu$ PD72103A and Host Processor

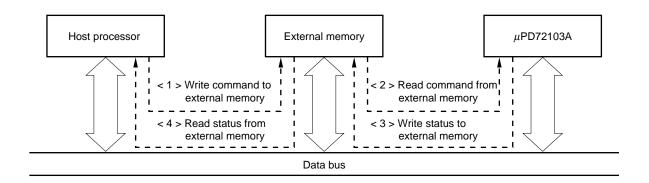

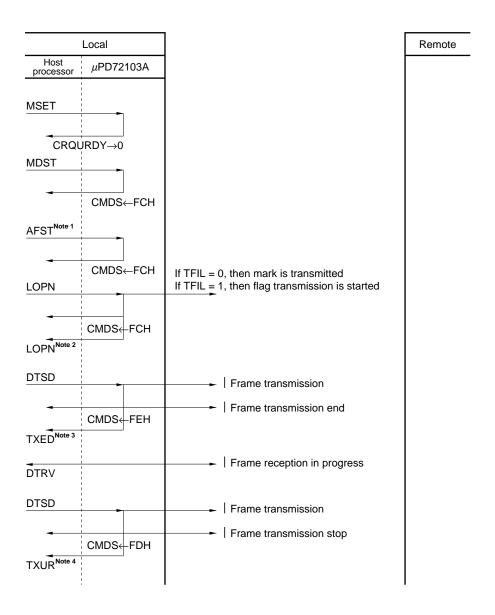

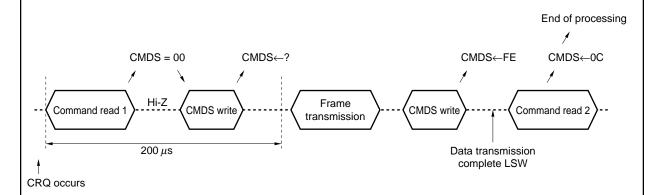

Figure 2-9. Command/Status Handling between  $\mu$ PD72103A and Host Processor

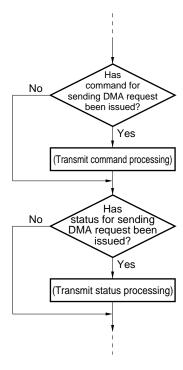

As shown in Figure 2-9 above, command/status handling between the  $\mu$ PD72103A and the host processor is performed via DMA transfers to and from external memory.

The transmit data is written from the host processor to external memory. The  $\mu$ PD72103A then reads the transmit data from external memory and converts it to serial data.

For the receive data, the  $\mu$ PD72103A converts them from serial data to parallel data, which is then written to external memory, where it is read by the host processor.

There are two basic methods for synchronizing these operations: (1) a method that uses the CRQ pin, INT pin, and CLRINT pin and (2) a method that uses the CCRQ bit and CCLRINT bit in the control register and the INT bit in the internal status register. It is also possible to combine these two methods.

#### Note See "2.1.1 Control register".

# (1) Method using the CRQ pin, INT pin, and CLRINT pin

- <1> When the host processor issues a command to the  $\mu$ PD72103A, the command is written to a command table in external memory<sup>Note</sup> and the CRQ pin becomes active (high level). When this operation is completed, the  $\mu$ PD72103A begins reading the command.

- <2> When it is necessary for the  $\mu$ PD72103A to report to the host processor, the host processor sets the INT pin as inactive (low level) by setting the CLRINT pin as active (high level).

- <3> Next, the  $\mu$ PD72103A writes a status report to external memory and sets INT pin as active (high level). The host processor uses this signal as an interrupt to detect the timing of the status report from the  $\mu$ PD72103A.

Note See "2.3.1 B. Method using write to external memory".

# (2) Method using the CCRQ bit and CCLRINT bit in the control register and the INTS bit in the internal status register

- <1> When the host processor issues a command to the  $\mu$ PD72103A, the command is written to external memory as was done via method (1) above<sup>Note 1</sup>. After that, "1" is written to the CCRQ bit.

- <2> When it is necessary for the  $\mu$ PD72103A to report to the host processor, the host processor writes a "1" to the CCLRINT bit in the  $\mu$ PD72103A's control register, which sets a "0" to the INTS bit.

- <3> After the  $\mu$ PD72103A writes the status information to external memory, it sets "1" to the INTS bit. Since the INTS bit and the INT pin correspond to the same signal, the host processor is able to detect the status report timing simply by polling the INTS bit, and without using an interrupt for the INT pin<sup>Note 2</sup>.

- Notes 1. See "2.3.1 B. Method using write to external memory".

- 2. See "2.1.2 Internal status register".

#### 2.3.1 Command issuance

Commands can be issued via the following two methods.

- Method using write to internal FIFO

This method is used to initiate the "memory area setting LCW" command.

- Method using write to external memory

This method can be used to initiate the "memory area setting LCW" command or to initiate commands other than the "memory area setting LCW" command.

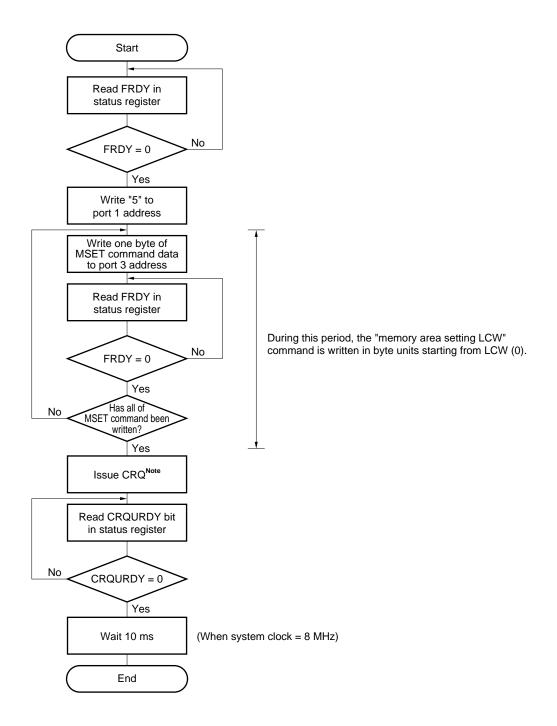

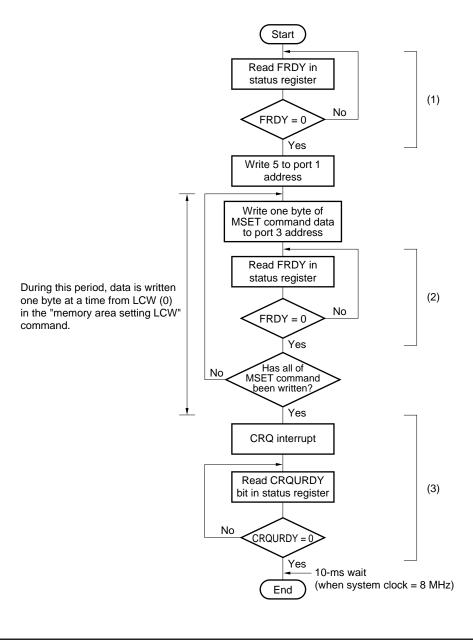

#### A. Method using internal FIFO write

Immediately after the FIFO in the  $\mu$ PD72103A has been reset, this method writes only the "memory area setting LCW" command. This method can only be used once when setting a start address of the system area immediately after a reset. The flow to be followed when writing to the internal FIFO is shown below.

Figure 2-10. Flow Chart for Writing "Memory Area Setting LCW" Command to Internal FIFO

**Note** This is done via a pulse input to the CRQ pin or by setting "1" to the CCRQ bit in the command register.

#### B. Method using write to external memory

Actually, there are two methods that use a write to external memory.

The first method writes the "memory area setting LCW" command in byte units immediately after a reset, starting from address 0.

After the command is executed (and the CRQ pin and CCRQ bit of the control register are active), this method is the same as when writing the "memory area setting LCW" command to the internal FIFO.

The other method writes a command to a command table. This method is used when issuing a command other than the "memory area setting LCW" command. Use the following steps to write the command.

- (1) Check that the CMDS field in the LCW where a command is written is "FCH/FDH/FEH". If the CMDS field is something else, LCW cannot be used, so wait until it becomes "FCH/FDH/FEH".

- (2) After writing the command number to LCW (0) and the command information to LCW (2) to (15), write "00H" to LCW (1). Make sure that writing to LCW (1) is the last operation in this sequence.

- (3) Issue the command after the CRQ pin or CCRQ bit of the control register becomes active.

After the issued command has been executed, command execution can be confirmed by inserting "FCH/FDH/FEH" into the command area's CMDS field or by writing a command end status to the status table.

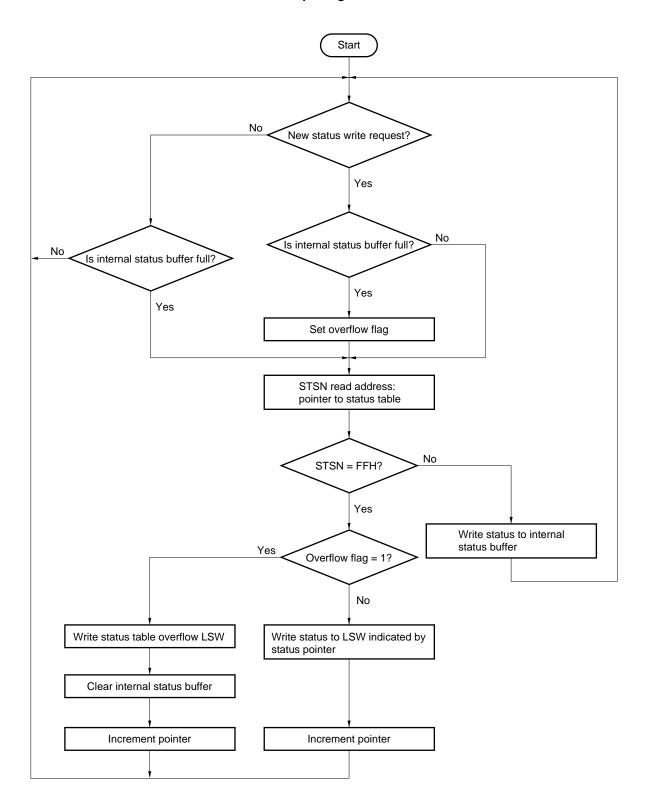

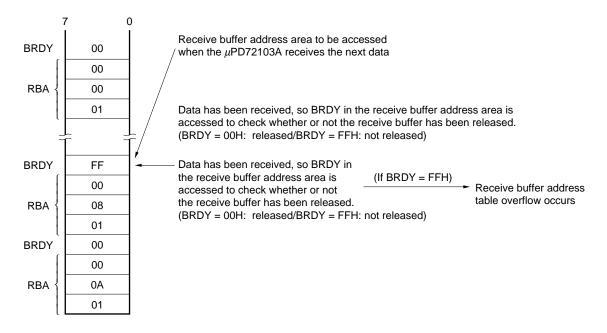

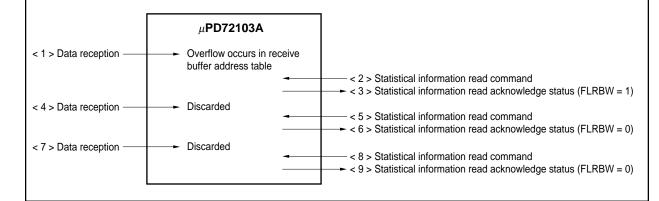

#### 2.3.2 Status report

After a command has been executed or data has been received, the  $\mu$ PD72103A writes information to the status table, then sets the INT pin or the INTS bit as active.

Meanwhile, the host processor detects the active state of the INT pin or INTS bit, after which the status table should be checked. Use the following steps to check the status table.

- (1) Set the CLRINT pin or CCLRINT bit as active and the INT pin or INTS bit as inactive.

- (2) Check the status table and process all of the reported status settings. Note that several status settings may be reported for a single interrupt.

- (3) After completing this processing, write FFH to LSW (0) in the status table and then release the status table.

However, in some cases when the above processing steps are used, a status check by the host processor shows that there are no status reports. This occurs when all processing has been completed during the previous round of status processing, such as is shown in Figure 2-11. Therefore, such cases do not indicate a fault or abnormality.

Host processor system (CPU + memory)

α 1 > Write status to LSW(0) in LSW0 of status table

α 2 > Set INT as active

α 3 > Write status to LSW1 of status table

α 4 > Interrupt (check) by host processor

α 5 > Issue CLRINT (active)

α 8 > Process LSW0 to LSW2

Write FFH to STSN (LSW(0))

Figure 2-11. Status Report (when Status Area is LSW0 to LSW2)

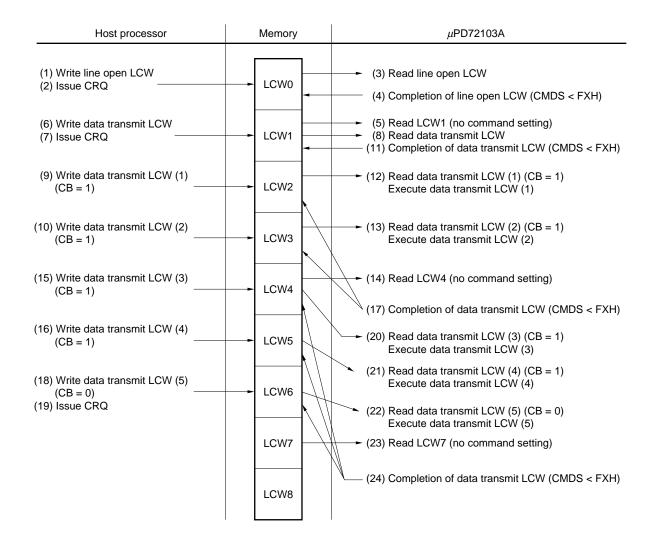

#### 2.3.3 Command chain function

< 9 > Interrupt (check) by host processor

No status to be processed

The command chain function enables the  $\mu$ PD72103A to sequentially execute several commands allocated successively in memory by issuing only one command request (which is executed by setting the CRQ pin or CCRQ bit as active). This function operates via the following sequence.

- (1) The host processor sets all of the commands to be executed to external memory in advance. "FFH" is then set to LCW(1) in the command table following the last command to be executed.

- (2) After the commands are set to external memory, the CRQ pin or CCRQ bit is set as active.

The  $\mu$ PD72103A then executes all of the commands in external memory up to where "FFH" has been set to LCW(1) in the command table.

#### 2.4 Initialization of External Memory

After the  $\mu$ PD72103A has been reset, the host processor writes FFH to initialize the external memory before issuing the "memory area setting LCW" command. This empties the command table and status table.

#### 2.5 Methods for Using External Memory

From the perspective of the  $\mu$ PD72103A, external memory is memory that exists externally and is used for the host interface. Set the following five areas in external memory using the methods described in sections **2.5.1** to **2.5.5** below.

- (1) Command table

- (2) Status table

- (3) Receive buffer address table

- (4) Receive buffer

- (5) Transmit buffer

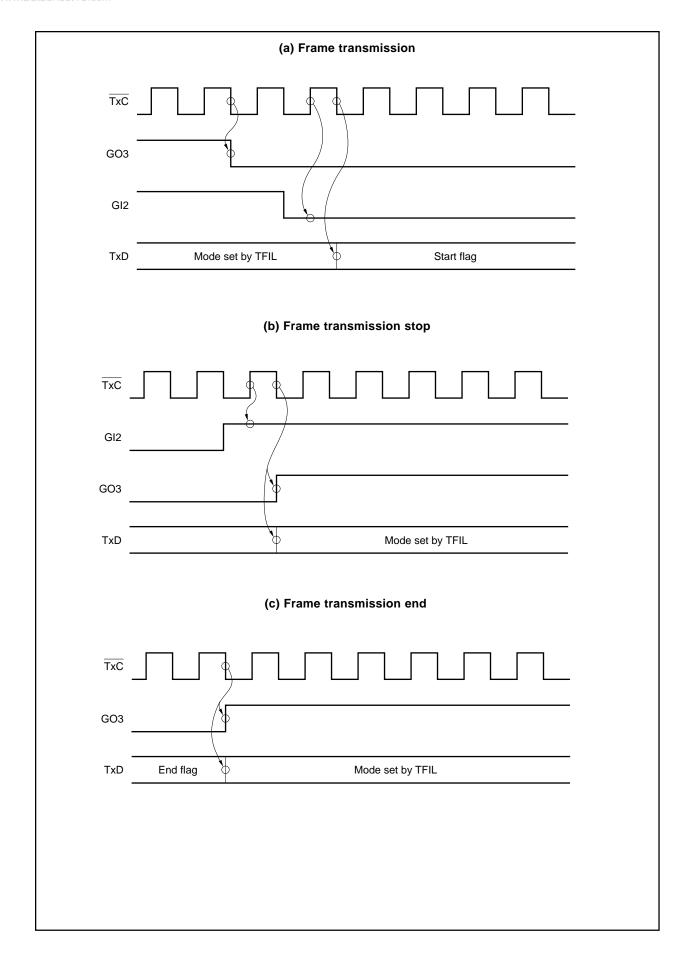

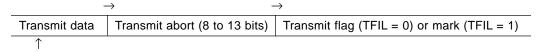

#### 2.5.1 Command table