# **AK8432**

6CH リニアセンサー対応 10bit 40MSPS×3 アナログプリプロセッサ

### 特長

□ 最大処理速度

CDS モード, クランプモード時

1CH, 2CH, 3CH モード: チャネル当たり 40M sample/sec 4CH,6CH モード: チャネル当たり 20M sample/sec

DC 直結モード時

1CH, 2CH, 3CH モード: チャネル当たり 10M sample/sec 4CH, 6CH モード: チャネル当たり 8.3M sample/sec

□ 最大入力信号レベル: 1.35Vpp(typ.)@CDS モード, DC 直結モード

1.29Vpp(typ.)@クランプモード

□ CCD,CIS 両方の信号極性に対応

□ 6CH 同時サンプリング CDS 回路(Correlated Double Sampling:相関二重サンプル)

□ オフセット DAC: レンジ±200mV(typ.), 8bit, 6 チャネル独立

□ PGA: ゲイン調整範囲 0dB~18dB(typ.), 8bit, 6 チャネル独立

□ リニアリティ: DNL= -1LSB(min.), +1.5LSB(max.) コード欠けなし保証

□ 5bit 出力バス: 10bit データを 5bit×2 サイクルで出力

□ 4線式シリアルインターフェイス

□ 電源: 3.3V±0.3V

□ 消費電力: 530mW(typ.)@6ch モード, チャネル当たり 20M sample/sec

□ パッケージ: 64pin LQFP, ピンピッチ 0.5mm, モールド 10mm×10mm

<MS0282-J-01> 2004/09

www.DataSlassAHI RASEI [AK8432]

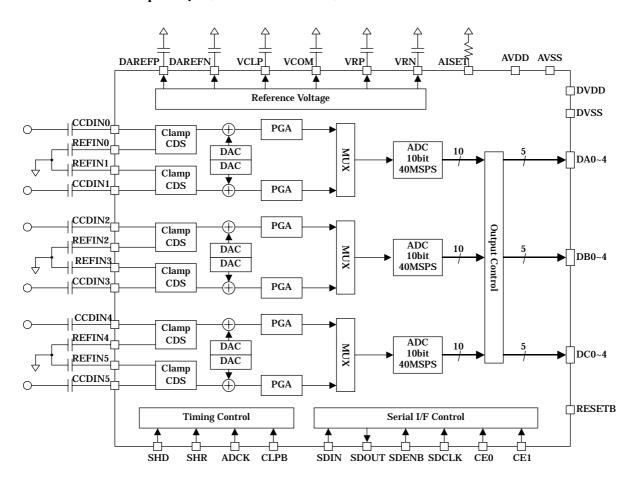

# 各ブロックの機能

□ Clamp/CDS センサーインターフェース回路

センサ出力の画信号レベルをサンプリングする回路です。サンプリングの方法として、CDS モードとクランプモード、DC 直結モードの 3 種類のモードを持っています。チャネル数モードは 1、2、3、4、6 チャネルがあり、チャネル数モードによって使われるチャネルが決まっています。使用しないチャネルの CDS 回路、DAC、PGA および ADC は自動的にパワーダウンします。

ロ DAC オフセット加算用 D/A コンバータ

センサーインターフェース部でサンプリングした信号レベルに加算するオフセット電圧を生成する D/A コンバータです。 DAC のレンジは $\pm 200$  mV(typ.) で分解能は 8 bit です。チャネル毎に異なるオフセット電圧をレジスタで設定できます。

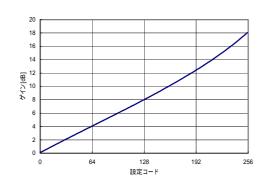

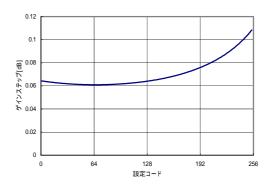

☐ PGA (Programmable Gain Amplifier)

各チャネルの信号振幅を調整するためのプログラマブルゲインアンプです。ゲインの設定範囲は 0dB から 18dB(typ.)、分解能は 8bit です。チャネル毎に異なるゲインをレジスタで設定できます。

□ MUX チャネルマルチプレクサ

4 チャネルモードおよび 6 チャネルモードのとき、同時にサンプリングした 2 つのチャネルの信号を時分割で ADC へ入力するためのアナログスイッチです。4 チャネルモードおよび 6 チャネルモードのとき、10bit ADC は時分割で 2 つのチャネルを処理します。

□ ADC A/D コンバータ

オフセット調整およびゲイン調整後の画信号レベルをデジタルデータに変換する 10bit,40MSPS の A/D コンバータです。 ADC は 3 個あり、 それぞれに MUX を介して 2 つのチャネルが接続されています。

□ Output Control ADC 出力データコントロール

ADC データの出力フォーマットを制御するデジタル回路です。ADC データはレジスタの設定により 5bit 幅もしくは 10bit 幅で出力されます。5bit 幅のときは ACDK の立上がりで上位 5bit、ADCK の立ち下がりで下位 5bit の ADC データが出力されます。10bit 幅のときは立上がりと立ち下がりで別のチャネルの ADC データが出力されます。また、10bit 幅を選択したときはレジスタの設定により、ADCK の立ち下がりのみで ADC データを出力させることもできます。

□ Reference Voltage 基準電圧生成回路

内部のクランプレベル VCLP、アナログコモンレベル VCOM、ADC 基準電圧 VRP,VRN、DAC 基準電圧 DAREFP,DAREFN を生成する回路です。

□ Timing Control タイミング発生回路

入力クロック ADCK,SHR,SHD,CLPB から、内部のタイミングパルスを発生するデジタル回路です。 ADCK は ADC の動作と ADC 出力データコントロール部の動作に使われるクロックです。 SHR はセンサ信号のリファレンスレベルをサンプリングするタイミングパルスです。 SHD はセンサ信号のデータレベルをサンプリングするタイミングパルスです。 CLPB はクランプ区間を示すタイミングパルスです。

www.DataSASAH/ KASEI

□ Serial I/F Control シリアルレジスタ・インターフェース回路 コントロールレジスタに値を設定するための 4 線式シリアルインターフェースです。コントロールレジスタは 読み出しも可能です。チップイネーブルピン CEO,CE1 でチップのアドレスを指定することにより、同一の 4 線に 4 個までの AK8432 を接続することができます。

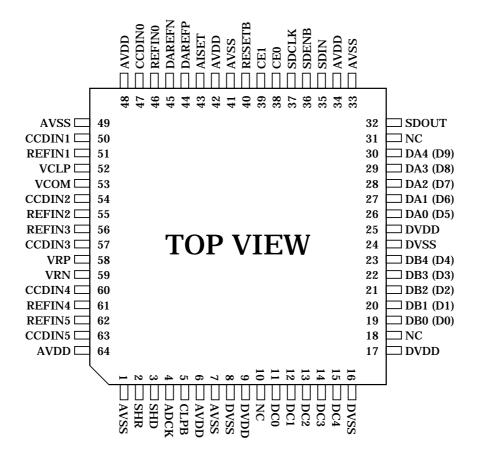

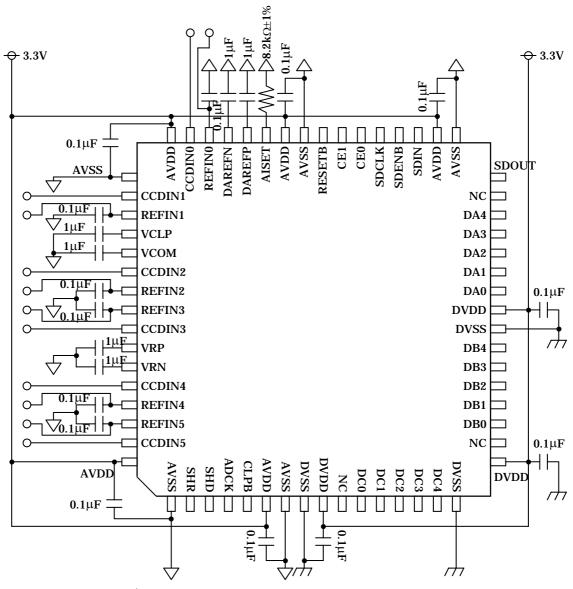

# ピン配置

図 1 ピン配置

<MS0282-J-01> 2004/09

www.DataSlasafili Kasei

# ピン機能

| No. | Name     | Type | Description                                        |

|-----|----------|------|----------------------------------------------------|

| 1   | AVSS     | PWR  | アナロググランド                                           |

| 2   | SHR      | I    | リファレンスレベル サンプリングパルス入力                              |

| 3   | SHD      | I    | データレベル サンプリングパルス入力                                 |

| 4   | ADCK     | I    | ADC サンプリングクロック入力                                   |

| 5   | CLPB     | I    | クランプ制御入力、 Low:クランプ動作 ON、High:クランプ動作 OFF            |

|     |          |      | CDS モードの時は Low に固定してください。                          |

| 6   | AVDD     | PWR  | アナログ電源                                             |

| 7   | AVSS     | PWR  | アナロググランド                                           |

| 8   | DVSS     | PWR  | デジタルグランド                                           |

| 9   | DVDD     | PWR  | デジタル電源                                             |

| 10  | NC       |      | オープンまたは AVSS 接続にしてください。                            |

| 11  | DC0      | 0    | ADC 出力、 ストレートバイナリコード、(DC0:LSB 側、DC4:MSB 側)         |

| 12  | DC1      | 0    | 3CH、6CH モードで 5bit 幅出力のときに CCDIN4,CCDIN5 に対応。       |

| 13  | DC2      | 0    | 10bit 幅出力のとき、および 1CH,2CH,4CH モード 5bit 幅出力のときは使     |

| 14  | DC3      | 0    | 用しません。これらのモードのときは次の状態になります。                        |

| 15  | DC4      | 0    | 通常動作時: Low レベルを出力                                  |

|     |          |      | パワーダウン時: レジスタ設定により Low レベルまたは High-Z 出力            |

| 16  | DVSS     | PWR  | デジタルグランド                                           |

| 17  | DVDD     | PWR  | デジタル電源                                             |

| 18  | NC       |      | オープンまたは AVSS 接続にしてください。                            |

| 19  | DB0 (D0) | 0    | ADC 出力、 ストレートバイナリコード、 括弧内は 10bit 幅出力時の呼び名          |

| 20  | DB1 (D1) | 0    | (5bit 幅出力時 DB0:LSB 側、DB4:MSB 側 10bit 幅出力時 D0: LSB) |

| 21  | DB2 (D2) | 0    | 1CH モード 5bit 幅出力のときは使用しません。このときは次の状態になりま           |

| 22  | DB3 (D3) | 0    | す。                                                 |

| 23  | DB4 (D4) | 0    | 通常動作時: Low レベルを出力                                  |

|     |          |      | パワーダウン時: レジスタ設定により Low レベルまたは High-Z 出力            |

| 24  | DVSS     | PWR  | デジタルグランド                                           |

| 25  | DVDD     | PWR  | デジタル電源                                             |

| 26  | DA0 (D5) | 0    | ADC 出力、 ストレートバイナリコード、 括弧内は 10bit 幅出力時の呼び名          |

| 27  | DA1 (D6) | О    | (5bit 幅出力時 DA0:LSB 側、DA4:MSB 側 10bit 幅出力時 D9: MSB) |

| 28  | DA2 (D7) | О    |                                                    |

| 29  | DA3 (D8) | 0    |                                                    |

| 30  | DA4 (D9) | 0    |                                                    |

| 31  | NC       |      | オープンまたは AVSS 接続にしてください。                            |

| 32  | SDOUT    | 0    | シリアル I/F データ出力                                     |

| 33  | AVSS     | PWR  | アナロググランド                                           |

| 34  | AVDD     | PWR  | アナログ電源                                             |

| No. | Name   | Туре | Description                              |

|-----|--------|------|------------------------------------------|

| 35  | SDIN   | I    | シリアル I/F データ入力                           |

| 36  | SDENB  | I    | シリアル I/F データイネーブル                        |

| 37  | SDCLK  | I    | シリアル I/F クロック                            |

| 38  | CE0    | I    | チップイネーブル                                 |

| 39  | CE1    | I    |                                          |

| 40  | RESETB | Ι    | リセット                                     |

| 41  | AVSS   | PWR  | アナロググランド                                 |

| 42  | AVDD   | PWR  | アナログ電源                                   |

| 43  | AISET  | I    | 内部バイアス電流、AVSS との間に抵抗 8.2kΩを接続            |

| 44  | DAREFP | 0    | DAC 基準電圧正側、AVSS との間に安定化用コンデンサを接続         |

| 45  | DAREFN | 0    | DAC 基準電圧負側、AVSS との間に安定化用コンデンサを接続         |

| 46  | REFIN0 | I    | リファレンス入力、AVSS との間に CCDINO の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 47  | CCDIN0 | I    | センサ信号入力                                  |

| 48  | AVDD   | PWR  | アナログ電源                                   |

| 49  | AVSS   | PWR  | アナロググランド                                 |

| 50  | CCDIN1 | I    | センサ信号入力                                  |

| 51  | REFIN1 | I    | リファレンス入力、AVSS との間に CCDIN1 の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 52  | VCLP   | 0    | クランプレベル出力、AVSS との間に安定化用コンデンサを接続          |

| 53  | VCOM   | 0    | 内部基準電圧、AVSS との間に安定化用コンデンサを接続             |

| 54  | CCDIN2 | I    | センサ信号入力                                  |

| 55  | REFIN2 | I    | リファレンス入力、AVSS との間に CCDIN2 の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 56  | REFIN3 | I    | リファレンス入力、AVSS との間に CCDIN3 の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 57  | CCDIN3 | I    | センサ信号入力                                  |

| 58  | VRP    | 0    | ADC 基準電圧正側、AVSS との間に安定化用コンデンサを接続         |

| 59  | VRN    | 0    | ADC 基準電圧負側、AVSS との間に安定化用コンデンサを接続         |

| 60  | CCDIN4 | I    | センサ信号入力                                  |

| 61  | REFIN4 | I    | リファレンス入力、AVSS との間に CCDIN4 の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 62  | REFIN5 | I    | リファレンス入力、AVSS との間に CCDIN5 の入力コンデンサと同容量のコ |

|     |        |      | ンデンサを接続。DC 直結モード時は信号の基準レベルを入力。           |

| 63  | CCDIN5 | I    | センサ信号入力                                  |

| 64  | AVDD   | PWR  | アナログ電源                                   |

Type I: 入力ピン O: 出力ピン PWR: 電源ピン

注) AVDD はアナログ部およびロジック部の電源、DVDD はデジタル出力バッファの電源です。

www.DataSlasAHI KASEI [AK8432]

# 絶対最大定格

AVSS= DVSS=0V、全ての電圧はグランドに対する値です。

| 項目             | 記号   | Min. | Max.     | 単位 | 備考              |

|----------------|------|------|----------|----|-----------------|

| 電源電圧           | AVDD | -0.3 | 4.5      | V  |                 |

|                | DVDD | -0.3 | 4.5      | V  |                 |

| 入力電流           | IIN  | -10  | 10       | mA | 電源ピンを除く         |

| アナログ入力電圧       | VINA | -0.3 | AVDD+0.3 | V  |                 |

| デジタル入力電圧(入力ピン) | VINL | -0.3 | AVDD+0.3 | V  |                 |

| デジタル入力電圧(出力ピン) | VONL | -0.3 | DVDD+0.3 | V  | 外部過入力に対する<br>制約 |

| 動作周囲温度         | Ta   | 0    | 70       | °C |                 |

| 保存温度           | Tstg | -65  | 150      | °C |                 |

これらの限界以上での動作は素子の永久破壊を引き起こす可能性があります。

### 推奨動作条件

AVSS= DVSS=0V、全ての電圧はグランドに対する値です。

| , <u> </u>          |        |      |      |      |              |      |  |  |  |  |  |

|---------------------|--------|------|------|------|--------------|------|--|--|--|--|--|

| 項目                  | 記号     | Min. | Typ. | Max. | 単位           | 備考   |  |  |  |  |  |

| 電源電圧                |        |      |      |      |              |      |  |  |  |  |  |

| アナログ                | AVDD   | 3.0  | 3.3  | 3.6  | $\mathbf{V}$ |      |  |  |  |  |  |

| 出力バッファ              | DVDD   | 3.0  | 3.3  | 3.6  | $\mathbf{V}$ |      |  |  |  |  |  |

| REFINn(n=0~5) DC 直結 | VREFIN | 0    |      | AVDD | V            | 正極性時 |  |  |  |  |  |

| モード時入力電圧            |        |      |      | -1.3 |              |      |  |  |  |  |  |

|                     |        | 1.3  |      | AVDD | V            | 負極性時 |  |  |  |  |  |

# 電気的特性

### ■ DC 特性

$(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| 項目             | 記号    | ピン  | Min.    | Max.    | 単位             | 備考           |

|----------------|-------|-----|---------|---------|----------------|--------------|

| High レベル入力電圧   | VIH   | 注 1 | 0.7AVDD |         | V              |              |

| Low レベル入力電圧    | VIL   | 注 1 |         | 0.3AVDD | V              |              |

| High レベル出力電圧 1 | VOH1  | 注 2 | 0.7DVDD |         | V              | IOH= -1mA    |

| Low レベル出力電圧 1  | VOL1  | 注 2 |         | 0.3DVDD | V              | IOL= 1mA     |

| High レベル出力電圧 2 | VOH2  | 注 3 | 0.7DVDD |         | V              | IOH= -0.25mA |

| Low レベル出力電圧 2  | VOL2  | 注 3 |         | 0.3DVDD | V              | IOL= 0.25mA  |

| 入力リーク電流        | ILIKG | 注 1 | -10     | 10      | $\mu$ <b>A</b> |              |

| High-Zリーク電流    | IOZ   | 注 2 | -10     | 10      | $\mu$ <b>A</b> |              |

<sup>(</sup>注1) SHD, SHR, ADCK, CLPB, SDCLK, SDENB, SDIN, CE0, CE1, RESETB

(注3) SDOUT

<MS0282-J-01> 2004/09

この極限状態での通常動作は保証されません。

<sup>(</sup>注2) DA0~DA4, DB0~DB4, DC0~DC4

# ■ アナログ特性

(AVDD=3.3V, DVDD=3.3V, Ta= 25°C, 特記無き場合はADCK=40MHz)

| ·                       |                | = 3.3  V,  DVDD = 3.3  V,  1a = 2 | , 104        | 2000     |       |                    |  |  |  |  |  |

|-------------------------|----------------|-----------------------------------|--------------|----------|-------|--------------------|--|--|--|--|--|

| 項目                      | 記号             | 条件                                | min.         | typ.     | max.  | 単位                 |  |  |  |  |  |

|                         |                | 基準電圧部                             |              |          |       |                    |  |  |  |  |  |

| クランプ電圧                  | VCLP           | 正極性時                              | 1.25         | 1.4      | 1.55  | V                  |  |  |  |  |  |

|                         |                | 負極性時                              | 2.15         | 2.3      | 2.45  |                    |  |  |  |  |  |

| コモン電圧                   | VCOM           |                                   | 1.1          | 1.2      | 1.3   | V                  |  |  |  |  |  |

| ADC 正側基準電圧              | VRP            |                                   | 1.6          | 1.7      | 1.8   | V                  |  |  |  |  |  |

| ADC 負側基準電圧              |                |                                   | 0.6          | 0.7      | 0.8   |                    |  |  |  |  |  |

| DAC 正側基準電圧              |                | 正極性時                              | 1.845        | 2.245    | 2.645 | V                  |  |  |  |  |  |

|                         |                | <u></u>                           | 0.945        | 1.345    | 1.745 |                    |  |  |  |  |  |

| DAC 負側基準電圧              | DAREFN         | 正極性時                              | 1.605        | 2.005    | 2.405 | V                  |  |  |  |  |  |

|                         |                | 負極性時                              | 0.74         | 1.14     | 1.54  |                    |  |  |  |  |  |

| クランプ/CDS 部              |                |                                   |              |          |       |                    |  |  |  |  |  |

| 入力レンジ                   | VI             | PGA ゲイン=0dB 設定時                   |              |          |       | Vpp                |  |  |  |  |  |

|                         | • •            | CDS E-F                           | 1.23         | 1.35     | 1.47  | VPP                |  |  |  |  |  |

|                         |                | クランプモード                           | 1.19         | 1.29     | 1.39  |                    |  |  |  |  |  |

|                         |                | DC 直結モード                          | 1.23         | 1.35     | 1.47  |                    |  |  |  |  |  |

|                         | CIN            | CCDIN                             | 1.20         | 10       | 1.17  | pF                 |  |  |  |  |  |

| <u>ハガ母皇</u><br>入力帯域幅    | CBW            | CCDIN~ADC                         |              | 10       |       | PI.                |  |  |  |  |  |

| 八万市・玖幅<br> (注 1)        | CBW            | PGA ゲイン=0dB 設定時                   |              | 1        |       | pixel              |  |  |  |  |  |

| (/± 1)                  |                | PGA ケイフ=00B 設定時<br>オフセット調整 DAC    |              |          |       | pixei              |  |  |  |  |  |

| /\ ATI AF               | DDEG           | イフセット調整 DAC                       |              | i        |       | 1 1                |  |  |  |  |  |

| 分解能                     | DRES           | \\                                | . 105        |          | 8     | bit                |  |  |  |  |  |

| レンジ                     | DRNG           | 入力換算                              | ±165         | ±200     | ±235  | mV                 |  |  |  |  |  |

| 微分非直線性                  | DNL            | 単調性保証                             | -1.0         |          | +1.5  | LSB                |  |  |  |  |  |

|                         | •              | PGA                               | <b>.</b>     | <u> </u> | 1     |                    |  |  |  |  |  |

| 最大ゲイン                   | GMAX           | CCDIN~ADC<br>0dB 設定に対する相対値        | 17.5         | 18       | 18.5  | dB                 |  |  |  |  |  |

| ステップ幅                   | GSTA           | 単調性保証                             |              | 0.06     |       | dB                 |  |  |  |  |  |

|                         |                | 1 4/3122                          |              | ~0.11    |       |                    |  |  |  |  |  |

|                         |                | ADC                               |              |          | 1     | 1                  |  |  |  |  |  |

| 分解能                     | RES            |                                   |              |          | 10    | bit                |  |  |  |  |  |

| 微分非直線性                  | DNL            | CCDIN~ADC                         | -1.0         |          | +1.5  | LSB                |  |  |  |  |  |

|                         | DIVE           | コード欠けなし保証                         | 1.0          |          | 11.0  | Lob                |  |  |  |  |  |

|                         | 1              | <u></u>                           | ト <b>ー</b> ク |          |       | 1                  |  |  |  |  |  |

| 無入力時ノイズ                 | NI             | PGA ゲイン=0dB 設定時                   |              | 0.4      |       | LSB <sub>rms</sub> |  |  |  |  |  |

| (注 2)                   | 111            | PGA ゲイン=18dB 設定時                  |              | 0.4      |       | LODrms             |  |  |  |  |  |

| 内部オフセット(注 3)            | VOEST          | PGA ゲイン=0dB 設定時                   | -50          | 0.7      | 50    | mV/                |  |  |  |  |  |

| クロストーク                  | XTALK1         | PGA ソイノ=00B 設定時<br>(注 4)          | -30          | ±1       | 30    | mV<br>LSB          |  |  |  |  |  |

| クロストーク                  |                |                                   | -3           | ±1       | . 9   | LSB                |  |  |  |  |  |

|                         | XTALK2         | (注 5)                             | _ა           |          | +3    |                    |  |  |  |  |  |

| <b>フ</b> ナロ <i>ド</i> ☆7 | -              | 消費電流                              |              | 1        |       | 1                  |  |  |  |  |  |

| アナログ部                   | <sub>T A</sub> | 1CILE P                           |              | 4.5      | 0.5   | A                  |  |  |  |  |  |

| 通常動作時                   | IA             | 1CH モード                           |              | 45       | 65    | mA                 |  |  |  |  |  |

|                         |                | 6CH モード                           |              | 160      | 220   |                    |  |  |  |  |  |

| デジタル出力部                 | ID             | 6CH モード,フルスケール                    |              | 30       | 60    | mA                 |  |  |  |  |  |

|                         |                | -2dB 1MHz 正弦波入力,                  |              |          |       |                    |  |  |  |  |  |

|                         |                | 負荷 10pF                           |              |          |       |                    |  |  |  |  |  |

| パワーダウン時                 | IPD            | アナログ部+デジタル部                       |              |          | 0.1   | mA                 |  |  |  |  |  |

| · •                     |                |                                   |              |          | 1     |                    |  |  |  |  |  |

これらの特性は外部回路例に示した外付け部品とその定数の時のものです。

www.DataSASAH/ KASEI

(注 1) フルスケール-2dB のステップ信号を入力したときに ADC 出力が±1LSB 以内にセトリングするまでの時間。

- (注 2) 無入力時の ADC 出力コードばらつきのoとして定義。

- (注 3) 無入力時、オフセット DAC 設定 A0h(入力換算で-50mV に相当)と 60h(入力換算で 50mV に相当)の間に ADC 出力コードが000h から 001h に変化するオフセット DAC 設定値があるという定義。 オフセット調整 DAC のレンジはこの内部オフセットの調整にも使われるため、入力に対する調整レンジは内部オフセット分だけ減少します。

- (注 4) ADCK=40MHz、A/D 変換レートモード、6CH、CDS モード、被測定チャネルの PGA ゲイン =max.、他のチャネルの PGA ゲイン=min.。被測定チャネルの入力を固定し、他のチャネルにフルスケール-1dB のステップ信号を入力したときに被測定チャネルの出力コードがどれだけ振れるかという定義。

- (注 5) ADCK=10MHz、A/D 変換レートモード、全チャネル PGA ゲイン= $\min$ 。被測定チャネルの入力を固定し、他のチャネルにフルスケール-1dB のステップ信号を入力した時に被測定チャネルの出力コードがどれだけ振れるかという定義。

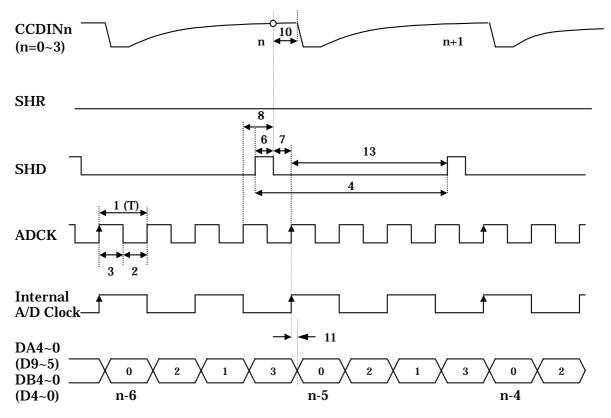

- スイッチング特性 1: ADC 変換レートモード, DC 直結モード時

- ・ タイミング図(1) 5bit 幅, 1CH,2CH,3CH モード

- ・ タイミング図(3) 5bit 幅, 4CH,6CH モード

- ・ タイミング図(5) 10bit 幅, 1CH モード

- ・ タイミング図(7) 10bit 幅, 2CH モード

- ・ タイミング図(9) 10bit 幅, 4CH モード

### $(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| No. | 項目              | 適用端子    | Min. | Тур. | Max. | 単位   | 条件            |

|-----|-----------------|---------|------|------|------|------|---------------|

| 1   | ADCK サイクル時間(T)  | ADCK    | 60   |      | 2000 | n s  | 4,6CH モード     |

|     |                 |         | 100  |      | 2000 |      | 1,2,3CH モード   |

| 2   | ADCK 低レベル幅      | ADCK    | 30   |      |      | n s  | 4,6CH モード     |

|     |                 |         | 50   |      |      |      | 1,2,3CH モード   |

| 3   | ADCK 高レベル幅      | ADCK    | 30   |      |      | n s  | 4,6CH モード     |

|     |                 |         | 50   |      |      |      | 1,2,3CH モード   |

| 4   | SHD サイクル時間      | SHD     |      | 2T   |      | n s  | 4,6CH モード     |

|     |                 |         |      | T    |      |      | 1,2,3CH モード   |

| 6   | SHD パルス幅        | SHD     | 30   |      |      | n s  |               |

| 7   | SHD セットアップ時間    | SHD     | 0    |      |      | n s  |               |

|     | (対 ADCK )       |         |      |      |      |      |               |

| 8   | SHD ディレイ時間      | SHD     | 30   |      |      | n s  |               |

|     | (対 ADCK )       |         |      |      |      |      |               |

| 10  | CCDIN0~5 ホールド時間 | CCDIN0  | 2    |      |      | n s  |               |

|     | (対 SHD )        | ~CCDIN5 |      |      |      |      |               |

| 11  | 出力データ遅延時間       | DA4~DA0 |      |      | 12   | n s  | C=10pF        |

|     | (対 ADCK )       | DB4~DB0 |      |      |      |      |               |

|     |                 | DC4~DC0 |      |      |      |      |               |

| 12  | パイプラインディレイ      | DA4~DA0 |      | 9    |      | ADCK | , , ,         |

|     |                 | DB4~DB0 |      |      |      | 換算   | および           |

|     |                 | DC4~DC0 |      |      |      | -    | 1CH 5bit 幅モード |

|     |                 |         |      | 8.5  |      |      | 1CH 10bit 幅モー |

|     |                 |         |      |      |      |      | ۲             |

| 13  | SHD="H"禁止区間     | SHD     | T+1  |      |      | n s  | 4,6ch モード     |

|     | (対 SHD 後、1発目の   |         |      |      |      |      |               |

|     | ADCK 基準)        |         |      |      |      |      |               |

www.DataSASAH KASEI [AK8432]

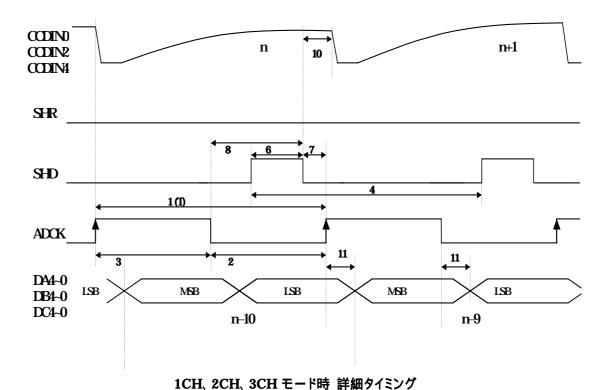

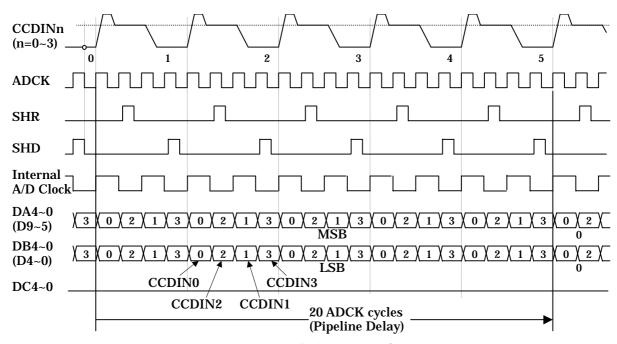

- スイッチング特性 2: ADC 変換レートモード, CDS,クランプモード時

- ・ タイミング図(2) 5bit 幅, 1CH,2CH,3CH モード

- ・ タイミング図(4) 5bit 幅, 4CH,6CH モード

- ・ タイミング図(6) 10bit 幅, 1CH モード

- ・ タイミング図(8) 10bit 幅, 2CH モード

- ・ タイミング図(10) 10bit 幅, 4CH モード

### $(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| No. | 項目                  | 適用端子     | Min. | Тур.                                  | Max. | 単位  | 条件            |

|-----|---------------------|----------|------|---------------------------------------|------|-----|---------------|

| 1   | ADCK サイクル時間(T)      | ADCK     | 25   | , , , , , , , , , , , , , , , , , , , | 2000 | n s |               |

| 2   | ADCK 低レベル幅          | ADCK     | 12.5 |                                       |      | n s |               |

| 3   | ADCK 高レベル幅          | ADCK     | 12.5 |                                       |      | n s |               |

| 4   | SHR,SHD サイクル時間      | SHR, SHD |      | 2T                                    |      | n s | 4,6ch モード     |

|     |                     |          |      | T                                     |      |     | 1,2,3ch モード   |

| 5   | SHR パルス幅            | SHR      | 8    |                                       |      | n s |               |

| 6   | SHD パルス幅            | SHD      | 8    |                                       |      | n s |               |

| 7   | SHD セットアップ時間        | SHD      | 0    |                                       |      | n s |               |

|     | (対 ADCK )           |          |      |                                       |      |     |               |

| 8   | SHD ディレイ時間          | SHD      | 11   |                                       |      | n s |               |

|     | (対 ADCK )           |          |      |                                       |      |     |               |

| 9   | CCDIN0~5 ホールド時間     | CCDIN0   | 2    |                                       |      | n s |               |

|     | (対 SHR )            | ~CCDIN5  |      |                                       |      |     |               |

| 10  | CCDIN0~5 ホールド時間     | CCDIN0   | 2    |                                       |      | n s |               |

|     | (対 SHD )            | ~CCDIN5  |      |                                       |      |     |               |

| 11  | 出力データ遅延時間           | DA4~DA0  |      |                                       | 12   | n s | C=10pF        |

|     | (対 ADCK )           | DB4~DB0  |      |                                       |      |     |               |

|     |                     | DC4~DC0  |      |                                       |      |     |               |

| 12  | パイプラインディレイ          | DA4~DA0  |      | 9                                     |      |     | 2,3,4,6ch モード |

|     |                     | DB4~DB0  |      |                                       |      | 換算  | および           |

|     |                     | DC4~DC0  |      | 0.7                                   |      |     | 1CH 5bit 幅モード |

|     |                     |          |      | 8.5                                   |      |     | 1CH 10bit 幅モー |

| 10  | CTTD "TT"++ 1 E: E: | CIID     | T. 4 |                                       |      |     | <u> </u>      |

| 13  | SHD="H"禁止区間         | SHD      | T+1  |                                       |      | n s | 4,6ch モード     |

|     | (対 SHD 後、1発目の       |          |      |                                       |      |     |               |

|     | ADCK 基準)            |          |      |                                       |      |     |               |

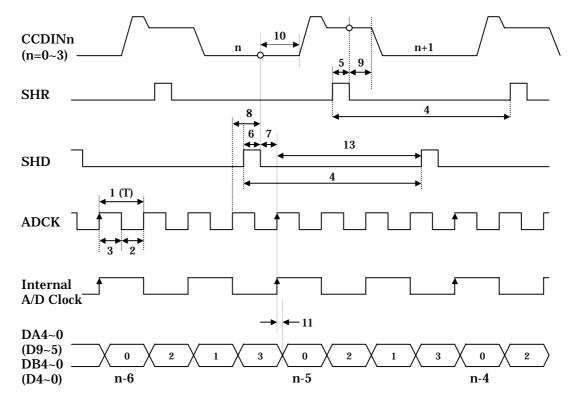

- スイッチング特性 3: 総画素レートモード, DC 直結モード時

- ・ タイミング図(11) 10bit 幅, 2CH モード

- ・ タイミング図(13) 10bit 幅, 3CH モード

- ・ タイミング図(15) 10bit 幅, 4CH モード

- ・ タイミング図(17) 10bit 幅, 6CH モード

# $(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| No. | 項目                            | 適用端子    | Min. | Тур.       | Max. | 単位  | 条件                  |

|-----|-------------------------------|---------|------|------------|------|-----|---------------------|

| 1   | ADCK サイクル時間(T)                | ADCK    | 20   |            | 333  | n s | 6ch モード             |

|     |                               |         | 30   |            | 500  |     | 4ch モード             |

|     |                               |         | 33.4 |            | 666  |     | 3ch モード             |

|     |                               |         | 50   |            | 1000 |     | 2ch モード             |

| 2   | ADCK 低レベル幅                    | ADCK    | 10   |            |      | n s | 6ch モード             |

|     |                               |         | 15   |            |      |     | 4ch モード             |

|     |                               |         | 16.7 |            |      |     | 3ch モード             |

|     |                               |         | 25   |            |      |     | 2ch モード             |

| 3   | ADCK 高レベル幅                    | ADCK    | 10   |            |      | n s | 6ch モード             |

|     |                               |         | 15   |            |      |     | 4ch モード             |

|     |                               |         | 16.7 |            |      |     | 3ch モード             |

|     |                               |         | 25   |            |      |     | 2ch モード             |

| 4   | SHD サイクル時間                    | SHD     |      | <b>6</b> T |      | n s | 6ch モード             |

|     |                               |         |      | <b>4</b> T |      |     | 4ch モード             |

|     |                               |         |      | 3T         |      |     | 3ch モード             |

|     |                               |         |      | 2T         |      |     | 2ch モード             |

| 6   | SHD パルス幅                      | SHD     | 30   |            |      | n s |                     |

| 7   | SHD セットアップ時間                  | SHD     | 0    |            | T/2  | n s |                     |

|     | (対 ADCK )                     |         |      |            |      |     |                     |

| 8   | SHD ディレイ時間                    | SHD     | 30   |            |      | n s |                     |

|     | (注 1)                         |         |      |            |      |     |                     |

| 10  | CCDIN0~5 ホールド時間               | CCDIN0  | 2    |            |      | n s |                     |

|     | (対 SHD )                      | ~CCDIN5 |      |            |      |     |                     |

| 11  | 出力データ遅延時間                     | DA4~DA0 |      |            | 12   | n s | C=10pF              |

|     | (対 ADCK )                     | DB4~DB0 |      |            |      |     |                     |

| 12  | パイプラインディレイ                    | DA4~DA0 |      | 30         |      |     | 3CH,6CH <b>モー</b> ド |

|     |                               | DB4~DB0 |      | 20         |      | 換算  | 2CH,4CH モード         |

| 13  | SHD="H"禁止区間<br>(対 SHD 後、1 発目の | SHD     | 3T+1 |            |      | n s | 6ch モード             |

|     | ADCK 基準)                      |         | 2T+1 |            |      |     | 4ch モード             |

(注 1) 内部 A/D クロックの立下リエッジを作る ADCK のエッジに対する値。2CH,4CH モード時は対 ADCK↑。3CH,6CH モード時は対 ADCK↓。

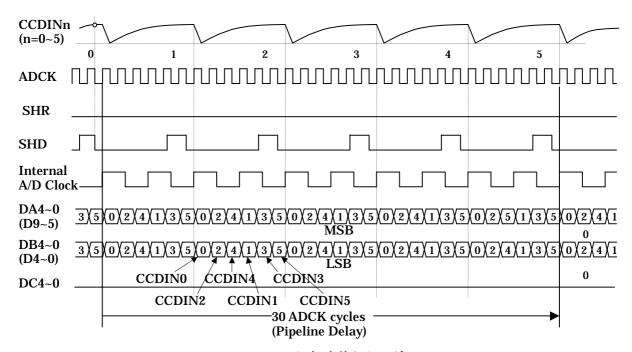

- スイッチング特性 4: 総画素レートモード, CDS,クランプモード時

- ・ タイミング図(12) 10bit 幅, 2CH モード

- ・ タイミング図(14) 10bit 幅, 3CH モード

- ・ タイミング図(16) 10bit 幅, 4CH モード

- ・ タイミング図(18) 10bit 幅, 6CH モード

$(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| No. | 項目              | 適用端子     | Min. | Тур.       | Max. | 単位  | 条件          |

|-----|-----------------|----------|------|------------|------|-----|-------------|

| 1   | ADCK サイクル時間(T)  | ADCK     | 12.5 |            | 333  | n s | 6ch モード     |

|     |                 |          | 12.5 |            | 500  |     | 4ch モード     |

|     |                 |          | 12.5 |            | 666  |     | 3ch モード     |

|     |                 |          | 12.5 |            | 1000 |     | 2ch モード     |

| 2   | ADCK 低レベル幅      | ADCK     | 6.25 |            |      | n s |             |

| 3   | ADCK 高レベル幅      | ADCK     | 6.25 |            |      | n s |             |

| 4   | SHR,SHD サイクル時間  | SHR, SHD |      | <b>6</b> T |      | n s | 6ch モード     |

|     |                 |          |      | <b>4</b> T |      |     | 4ch モード     |

|     |                 |          |      | <b>3</b> T |      |     | 3ch モード     |

|     |                 |          |      | 2T         |      |     | 2ch モード     |

| 5   | SHR パルス幅        | SHR      | 8    |            |      | n s |             |

| 6   | SHD パルス幅        | SHD      | 8    |            |      | n s |             |

| 7   | SHD セットアップ時間    | SHD      | 0    |            | T/2  | n s |             |

|     | (対 ADCK )       |          |      |            |      |     |             |

| 8   | SHD ディレイ時間      | SHD      | 12   |            |      | n s |             |

|     | (注 1)           |          |      |            |      |     |             |

| 9   | CCDIN0~5 ホールド時間 | CCDIN0   | 2    |            |      | n s |             |

|     | (対 SHR )        | ~CCDIN5  |      |            |      |     |             |

| 10  | CCDIN0~5 ホールド時間 | CCDIN0   | 2    |            |      | n s |             |

|     | (対SHD )         | ~CCDIN5  |      |            |      |     |             |

| 11  | 出力データ遅延時間       | DA4~DA0  |      |            | 12.0 | n s | C=10pF      |

|     | (対 ADCK )       | DB4~DB0  |      |            |      |     |             |

| 12  | パイプラインディレイ      | DA4~DA0  |      | 30         |      | -1  | 3CH,6CH モード |

|     |                 | DB4~DB0  |      | 20         |      | 換算  | 2CH,4CH モード |

| 13  | SHD="H"禁止区間     | SHD      | 3T+1 |            |      | n s | 6ch モード     |

|     | (対 SHD 後、1発目の   |          | 2T+1 |            |      | 1   | 4ch モード     |

|     | ADCK 基準)        |          |      |            |      |     | '           |

(注 1) 内部 A/D クロックの立下りエッジを作る ADCK のエッジに対する値。2CH,4CH モード時は対 ADCK↑。3CH,6CH モード時は対 ADCK↓。

タイミングは DC 特性で規定された各レベルを横切った時点で規定されます。

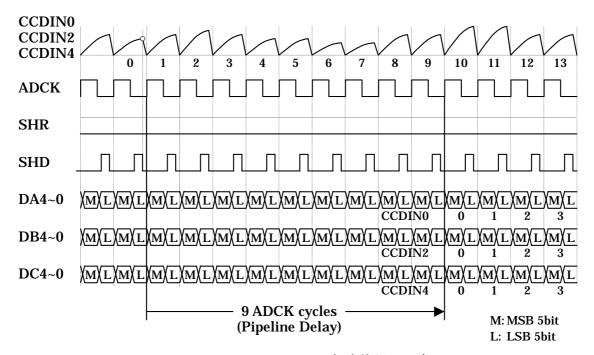

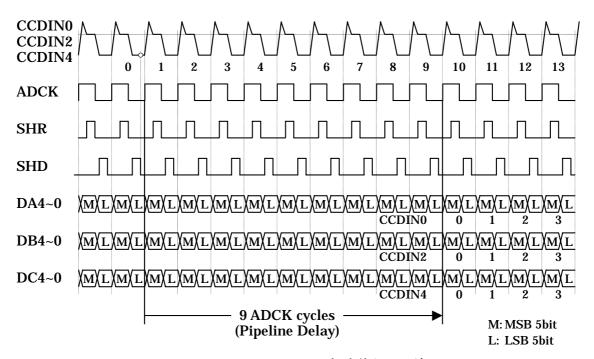

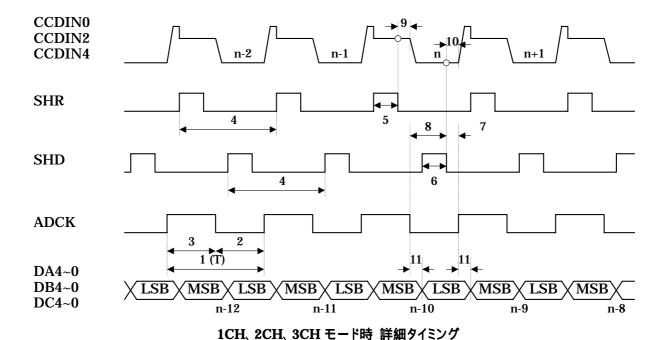

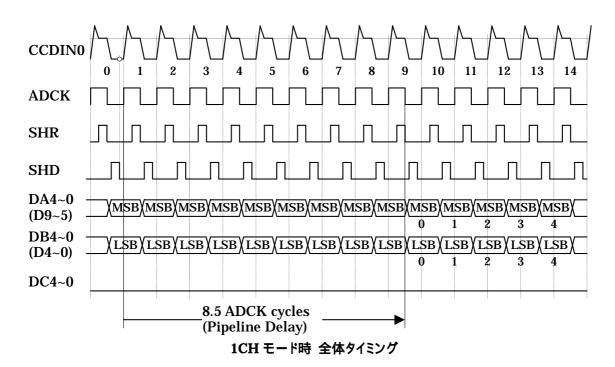

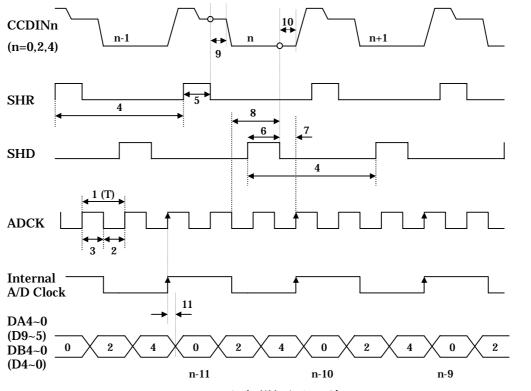

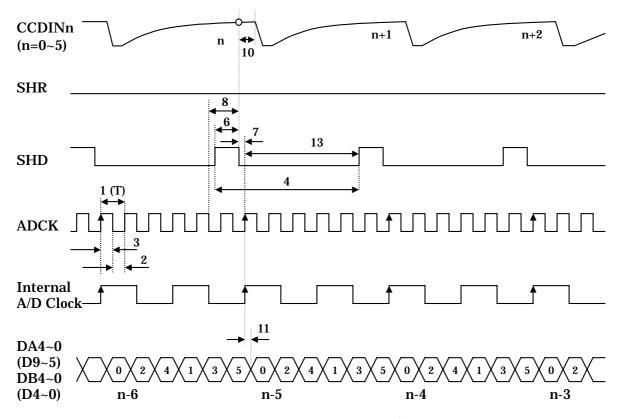

- タイミング図(1): ADCK 周波数=A/D 変換レートモード(5bit 幅出力)

- 1CH, 2CH, 3CH モード(DC 直結モード、正極性)スイッチング特性 1 の表を参照してください。

1CH、2CH、3CH モード時 全体タイミング

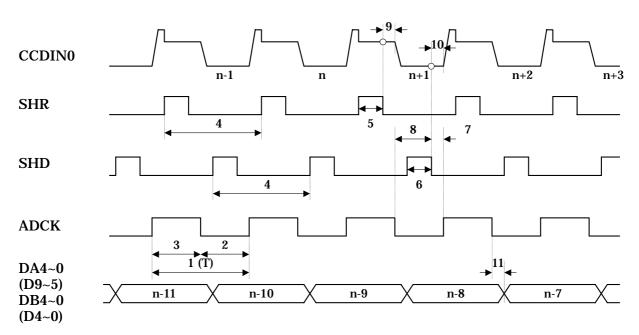

■ タイミング図(2): ADCK 周波数=A/D 変換レートモード(5bit 幅出力)

1CH, 2CH, 3CH モード(CDS モード&クランプモード、負極性)スイッチング特性 2 の表を参照してください。

1CH、2CH、3CH モード時 全体タイミング

www.DataSASAH/ KASEI

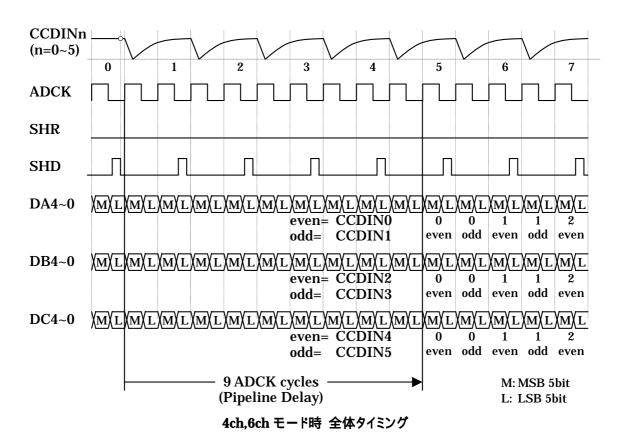

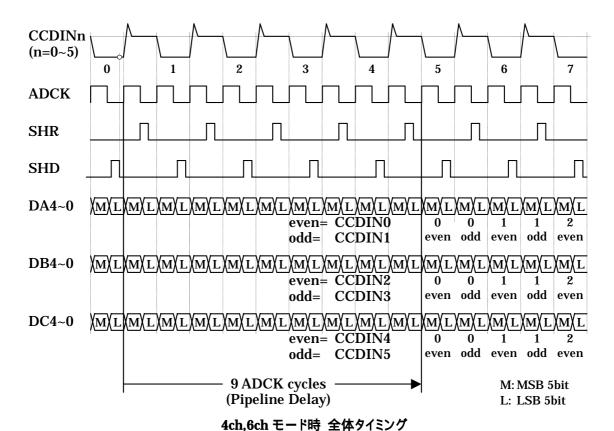

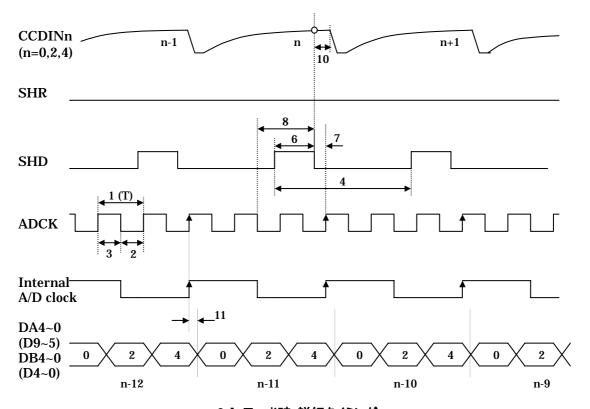

■ タイミング図(3): ADCK 周波数=A/D 変換レートモード(5bit 幅出力)

4CH, 6CH モード(DC 直結モード、正極性)スイッチング特性 1 の表を参照してください。

<MS0282-J-01> 2004/09

www.DataSlassAHI KASEI [AK8432]

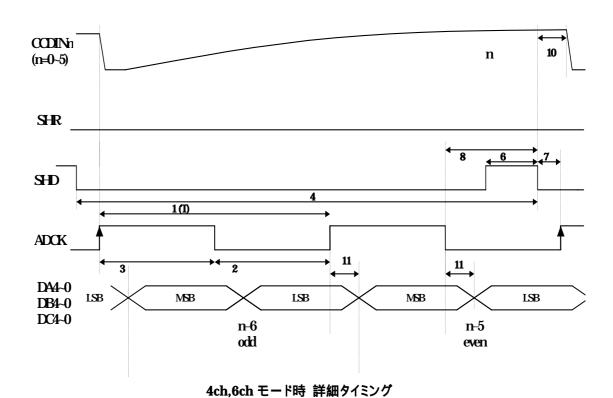

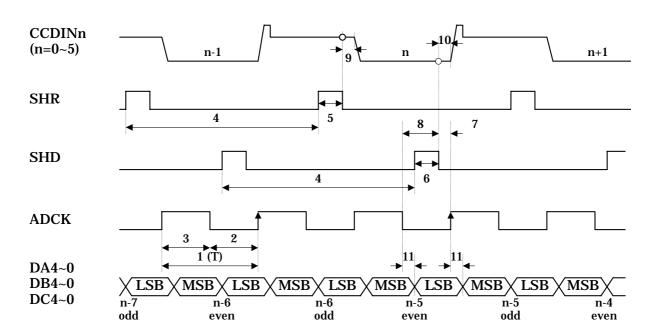

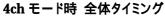

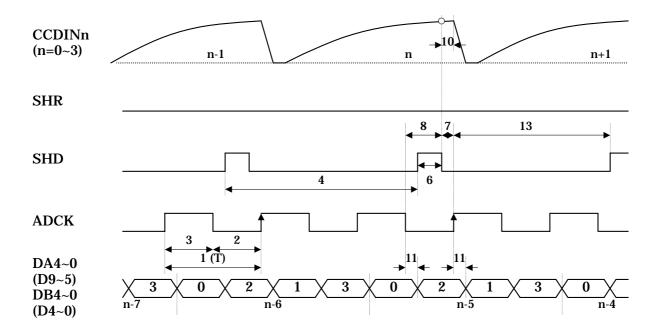

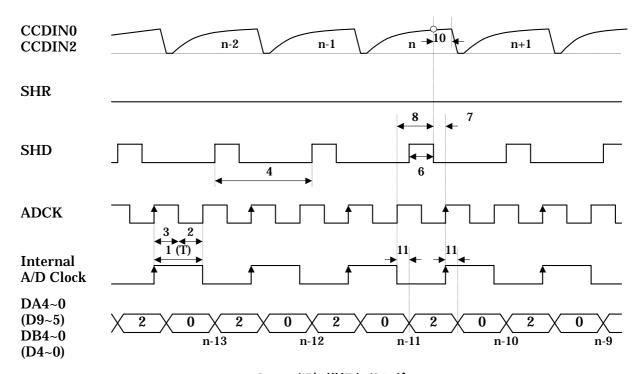

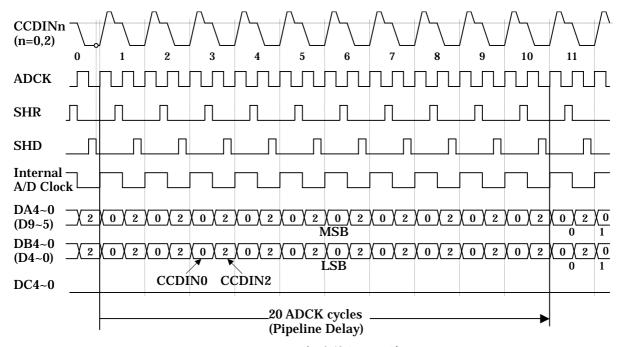

■ タイミング図(4): ADCK 周波数=A/D 変換レートモード(5bit 幅出力)

4CH, 6CH モード(CDS モード&クランプモード、負極性)スイッチング特性 2 の表を参照してください。

<MS0282-J-01> 2004/09

4ch,6ch モード時 詳細タイミング

www.DataSlasaHilliKasei

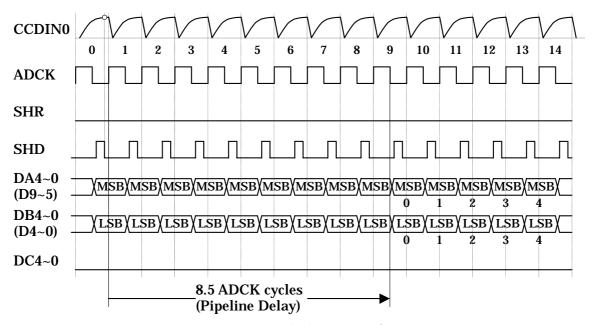

■ タイミング図(5): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

・ 1CH モード(DC 直結モード、正極性) スイッチング特性 1 の表を参照してください。

1CH モード時 全体タイミング

1CH モード時 詳細タイミング

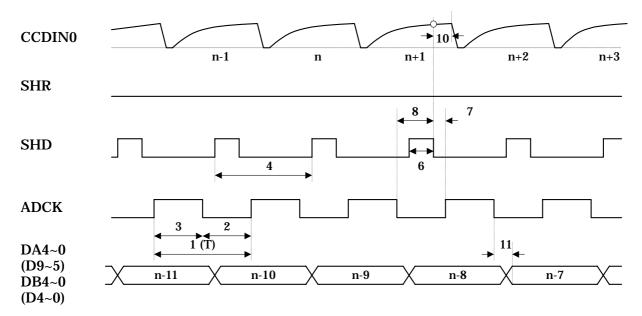

■ タイミング図(6): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

1CH モード(CDS モード&クランプモード、負極性)スイッチング特性 2 の表を参照してください。

1CH モード時 詳細タイミング

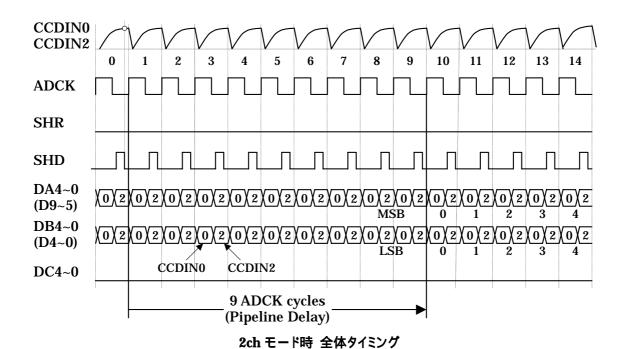

■ タイミング図(7): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

・ 2CH モード(DC 直結モード、正極性) スイッチング特性 1 の表を参照してください。

■ タイミング図(8): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

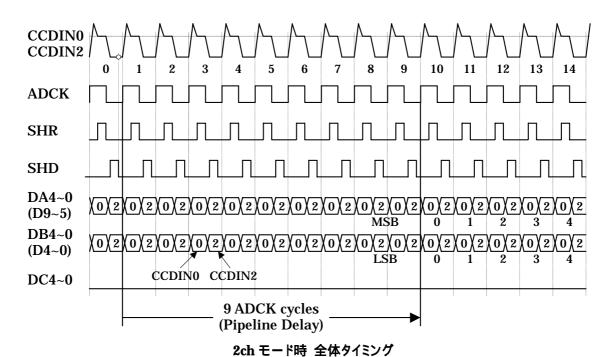

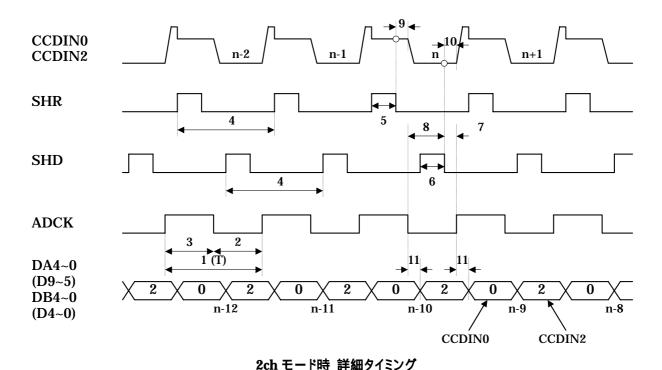

2CH モード(CDS モード&クランプモード、負極性)スイッチング特性 2 の表を参照してください。

www.DataSlasaHilliKasei

■ タイミング図(9): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

・ 4CH モード(DC 直結モード、正極性) スイッチング特性 1 の表を参照してください。

4ch モード時 詳細タイミング

www.DataSlasaHilliKasei

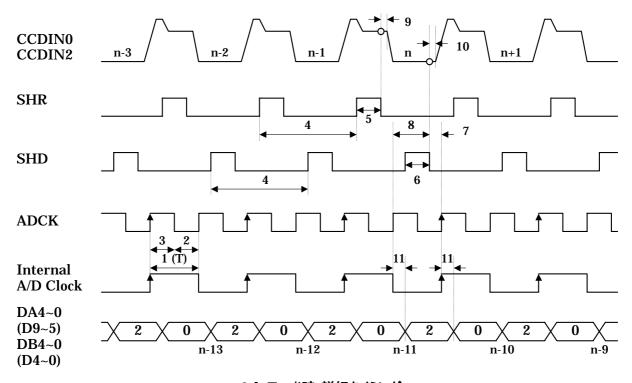

■ タイミング図(10): ADCK 周波数=A/D 変換レートモード(10bit 幅出力)

4CH モード(CDS モード&クランプモード、負極性)スイッチング特性 2 の表を参照してください。

4ch モード時 全体タイミング

4ch モード時 詳細タイミング

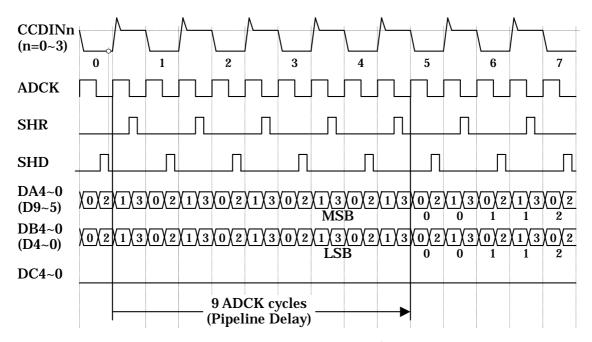

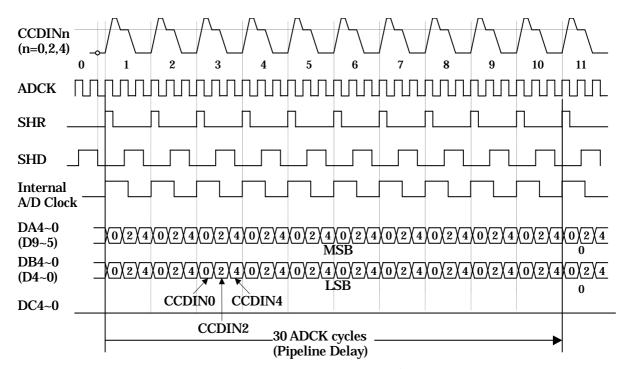

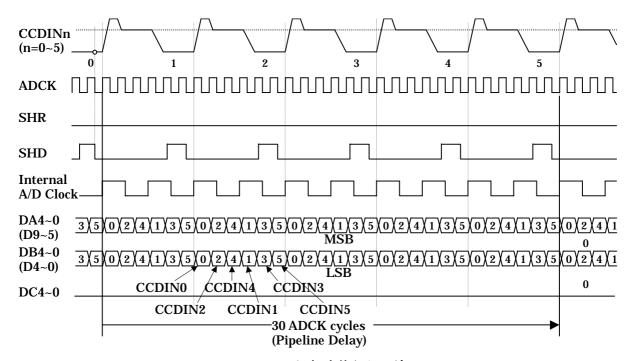

■ タイミング図(11): ADCK 周波数=総画素レートモード(10bit 幅出力)

・ 2CH モード(DC 直結モード、正極性) スイッチング特性 3 の表を参照してください。

2ch モード時 全体タイミング

2ch モード時 詳細タイミング

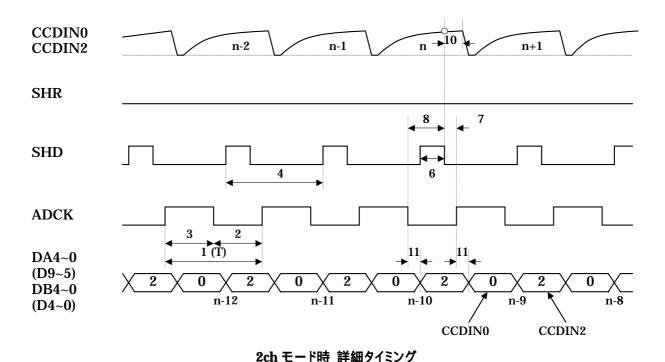

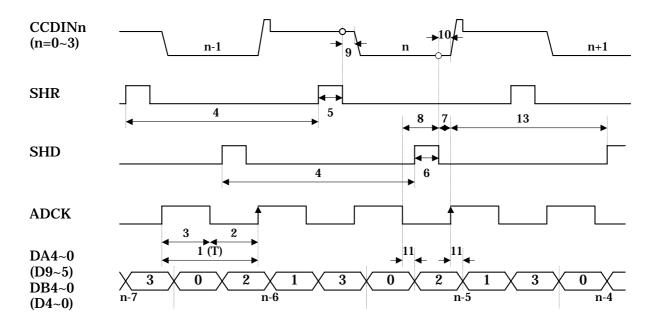

■ タイミング図(12): ADCK 周波数=総画素レートモード(10bit 幅出力)

・ 2CH モード(CDS モード & クランプモード、負極性) スイッチング特性 4 の表を参照してください。

2ch モード時 全体タイミング

2ch モード時 詳細タイミング

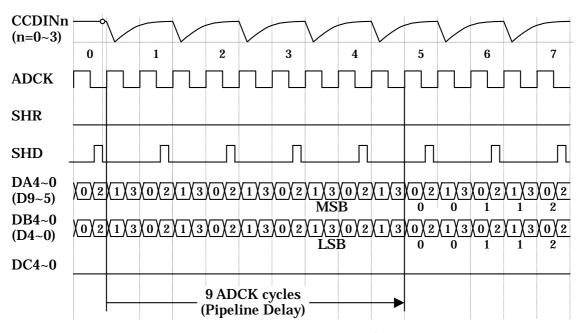

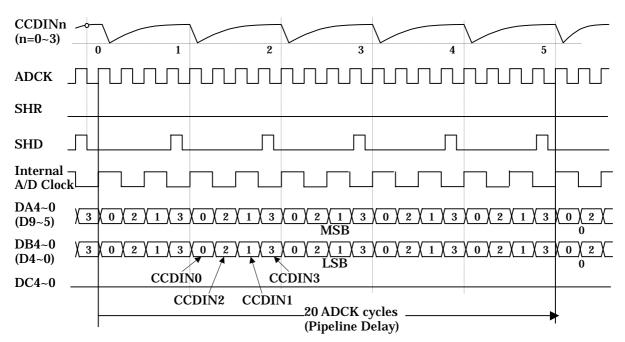

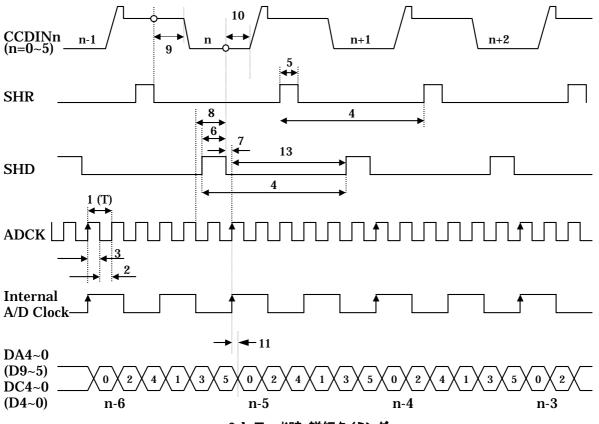

- タイミング図(13): ADCK 周波数=総画素レートモード(10bit 幅出力)

- ・ 3CH モード(DC 直結モード、正極性) スイッチング特性 3 の表を参照してください。

3ch モード時 全体タイミング

3ch モード時 詳細タイミング

■ タイミング図(14): ADCK 周波数=総画素レートモード(10bit 幅出力)

・ 3CH モード(CDS モード & クランプモード、負極性) スイッチング特性 4 の表を参照してください。

3ch モード時 全体タイミング

3ch モード時 詳細タイミング

www.DataSlasaHilliKasei

■ タイミング図(15): ADCK 周波数=総画素レートモード(10bit 幅出力)

・ 4CH モード(DC 直結モード、正極性) スイッチング特性 3 の表を参照してください。

4ch モード時 全体タイミング

4ch モード時 詳細タイミング

■ タイミング図(16): ADCK 周波数=総画素レートモード(10bit 幅出力)

4CH モード(CDS モード & クランプモード、負極性)スイッチング特性 4 の表を参照してください。

4ch モード時 全体タイミング

4ch モード時 詳細タイミング

www.DataSASAH/ KASEI

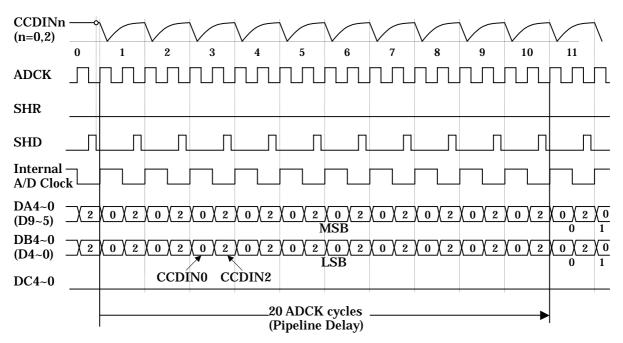

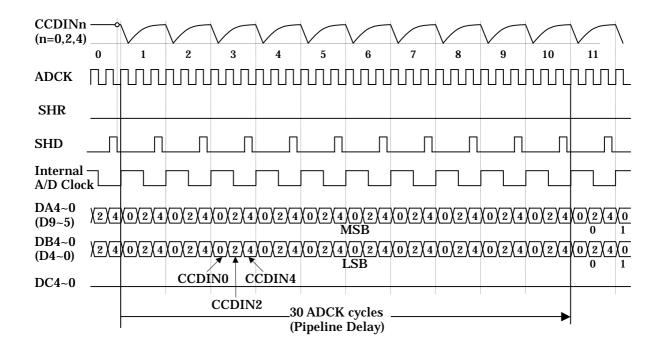

■ タイミング図(17): ADCK 周波数=総画素レートモード(10bit 幅出力)

・ 6CH モード(DC 直結モード、正極性) スイッチング特性 3 の表を参照してください。

6ch モード時 全体タイミング

6ch モード時 詳細タイミング

■ タイミング図(18): ADCK 周波数=総画素レートモード(10bit 幅出力)

6CH モード(CDS モード & クランプモード、負極性)スイッチング特性 4 の表を参照してください。

6ch モード時 全体タイミング

6ch モード時 詳細タイミング

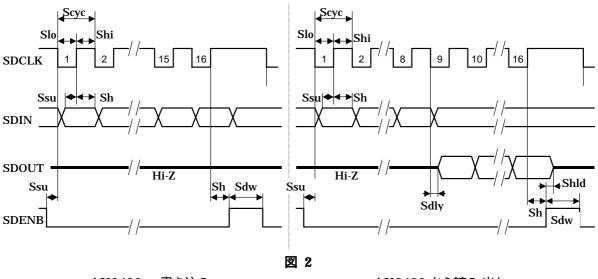

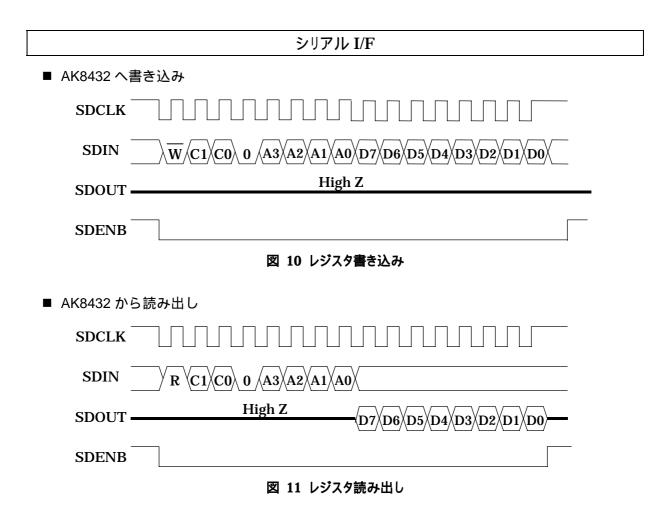

# ■ スイッチング特性: シリアル I/F

# $(AVDD=3.0V\sim3.6V, DVDD=3.0\sim3.6V, Ta=0\sim70^{\circ}C)$

| 項目                | 記号   | 適用端子  | Min. | Typ. | Max. | 単位  | 条件      |

|-------------------|------|-------|------|------|------|-----|---------|

| クロック周期            | Scyc | SDCLK |      |      | 10   | MHz |         |

| クロックパルス幅(H 区間)    | Shi  | SDCLK | 40   |      |      | ns  |         |

| クロックパルス幅(L 区間)    | Slo  | SDCLK | 40   |      |      | ns  |         |

| セットアップタイム         | Ssu  | SDIN  | 20   |      |      | ns  |         |

| (対 SDCLK)         |      | SDENB |      |      |      |     |         |

| ホールドタイム           | Sh   | SDIN  | 20   |      |      | ns  |         |

| (対 SDCLK)         |      | SDENB |      |      |      |     |         |

| SDCLK,SDENB 立ち上がり | Sr   | SDCLK |      |      | 6    | ns  | AVDD の  |

| 時間                |      | SDENB |      |      |      |     | 30% 70% |

| SDCLK,SDENB 立ち下がり | Sf   | SDCLK |      |      | 6    | ns  | AVDD の  |

| 時間                |      | SDENB |      |      |      |     | 70% 30% |

| SDENB High レベル幅   | Sdw  | SDENB | 40   |      |      | ns  |         |

| データ遅延時間           | Sdly | SDOUT |      |      | 30   | ns  |         |

| (対 SDCLK)         |      |       |      |      |      |     |         |

| データホールド時間         | Shld | SDOUT | 0    |      |      | ns  |         |

| (対 SDENB)         |      |       |      |      |      |     |         |

| シリアルデータ数          | Snum | SDCLK |      | 16   |      | 個   |         |

AK8432 へ書き込み

AK8432 から読み出し

# コントロールレジスタ

| アドレス   |        | データ    |                   |      |               |         |        |       |       |  |  |

|--------|--------|--------|-------------------|------|---------------|---------|--------|-------|-------|--|--|

| (16 進) | 初期値    | D7     | D6                | D5   | D4            | D3      | D2     | D1    | D0    |  |  |

|        | (16 進) |        |                   |      |               |         |        |       |       |  |  |

| 0      | 00     | センサ I/ | F モード             | 信号極性 |               | チャネル数   | Ţ      | ADCK  | パワー   |  |  |

|        |        |        |                   |      |               |         |        | 周波数   | ダウン   |  |  |

| 1      | 00     | SHR    | パワーダ              | 0    | 0             | 出力      | チャネル   | チャネル  | チャネル  |  |  |

|        |        | SHD    | ウン時出              |      |               | データ幅    | 0,1 処理 | 2,3 処 | 4,5 処 |  |  |

|        |        | 極性     | 力状態               |      |               |         | 順序     | 理順序   | 理順序   |  |  |

| 2      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N0     |       |       |  |  |

| 3      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N1     |       |       |  |  |

| 4      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N2     |       |       |  |  |

| 5      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N3     |       |       |  |  |

| 6      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N4     |       |       |  |  |

| 7      | 80     |        |                   | オ    | フセットデー        | -タ CCDI | N5     |       |       |  |  |

| 8      | 00     |        |                   | PGA  | <b>A</b> ゲインデ | ータ CCD  | IN0    |       |       |  |  |

| 9      | 00     |        |                   | PGA  | <b>A</b> ゲインデ | ータ CCD  | IN1    |       |       |  |  |

| Α      | 00     |        |                   | PGA  | 4 ゲインデ        | ータ CCD  | IN2    |       |       |  |  |

| В      | 00     |        |                   | PGA  | 4 ゲインデ        | ータ CCD  | IN3    |       |       |  |  |

| C      | 00     |        |                   | PGA  | <b>A</b> ゲインデ | ータ CCD  | IN4    |       |       |  |  |

| D      | 00     |        | PGA ゲインデータ CCDIN5 |      |               |         |        |       |       |  |  |

| Е      | 08     | テスト用   |                   |      |               |         |        |       |       |  |  |

| F      | 00     |        |                   |      | テス            | .卜用     |        |       |       |  |  |

初期値はリセット後の値。

電源投入後にリセットを行わない場合はテスト用レジスタ(アドレス E, F)に初期値を書き込んでください。

本データシート中で例えば R0 はアドレス 0 のレジスタを表します。R0,D0 はアドレス 0 のレジスタの D0 ビットを示します。以下で記述する各ビットはリセット後にデフォルトと表記された状態になります。

# □ R0 レジスタ

■ R0, D7-D6 センサ I/F モード

| D7 | D6 | センサ I/F モード   |  |

|----|----|---------------|--|

| 0  | 0  | DC 直結 (デフォルト) |  |

| 0  | 1  | CDS           |  |

| 1  | 0  | クランプ          |  |

www.DataSASAH/ KASEI

### ■ R0, D5 信号極性

| <b>D5</b> | 信号極性 | センサタイプ                           |  |  |

|-----------|------|----------------------------------|--|--|

| 0         | 負    | 基準レベルから低電位側に信号が振れる CCD など(デフォルト) |  |  |

| 1         | 正    | 基準レベルから高電位側に信号が振れる CIS など        |  |  |

### ■ R0, D4-D2 チャネル数

| D4 | D3 | D2 | チャネル数    | CCDIN |   |   |   |   |   |

|----|----|----|----------|-------|---|---|---|---|---|

|    |    |    |          | 0     | 1 | 2 | 3 | 4 | 5 |

| 0  | 0  | 0  | 1(デフォルト) |       | - | - | - | - | - |

| 0  | 0  | 1  | 2        |       | - |   | - | - | - |

| 0  | 1  | 0  | 3        |       | = |   | - |   | - |

| 0  | 1  | 1  | 4        |       |   |   |   | - | - |

| 1  | 0  | 0  | 6        |       |   |   |   |   |   |

: そのチャネル数モードで使われる入力チャネル

使われない CDS, DAC, PGA, ADC は自動的にパワーダウンします。

使われないチャネルの CCDINn,REFINn ピンにはコンデンサを接続する必要はありません。 使われないこれらのピンはオープンにしてください。

### ■ R0, D1 ADCK 周波数

| D1 | 入力 ADCK 周波数      | 備考                             |

|----|------------------|--------------------------------|

| 0  | A/D 変換レート(デフォルト) | 5bit 幅または 10bit 幅出力データを ADCK 立 |

|    |                  | ち上がリエッジと立下リエッジの両方で出力           |

| 1  | 総画素レート           | 10bit 幅出力データを ADCK の立ち下がリエッ    |

|    |                  | ジで出力                           |

デフォルトの A/D 変換レートモードでは ADC の変換レートと同じ周波数の ADCK を入力してください。 ADC データは ADCK の立ち上がりと立下りの両エッジで出力されます。 総画素レートモードでは有効なチャネルの画素レートの総和と同じ周波数の ADCK を入力してください。 ADC データは ADCK の立ち下がりエッジで出力されます。

### ■ R0, D0 パワーダウン

| D0 | 動作          |  |

|----|-------------|--|

| 0  | 通常動作(デフォルト) |  |

| 1  | パワーダウン      |  |

パワーダウン時はアナログ部がパワーダウンすると共にデジタル部へのクロック供給が停止します。 パワーダウン時の ADC データ出力 DA0~4, DB0~4, DC0~4 の状態はレジスタ R1,D6 で Low 固定か High Z 出力か選択できます。

www.DataSlasathi. Kasei

### □ R1 レジスタ

# ■ R1, D7 SHR, SHD 極性選択

| D7 | 極性                 |  |

|----|--------------------|--|

| 0  | アクティブ High (デフォルト) |  |

| 1  | アクティブ Low          |  |

本データシート中の図は全て SHR,SHD 極性がデフォルト設定の時のものです。

# ■ R1, D6 パワーダウン時出力状態

| D6 | 出力状態          |  |

|----|---------------|--|

| 0  | Low 固定(デフォルト) |  |

| 1  | High Z        |  |

### ■ R1, D3 出力データ幅

| D3 | 出力データ幅       |

|----|--------------|

| 0  | 5bit (デフォルト) |

| 1  | 10bit        |

ADCK 周波数の設定が総画素レートモード(R0,D1=1)のときは、出力データ幅設定に関わらず 10bit 幅になります。

### ■ R1, D2-D0 チャネル処理順序

| D2 | チャネル 0,1 処理順序                                                     |

|----|-------------------------------------------------------------------|

| 0  | CCDIN0 → CCDIN1 → CCDIN0 → CCDIN1(デフォルト)                          |

| 1  | $CCDIN1 \rightarrow CCDIN0 \rightarrow CCDIN1 \rightarrow CCDIN0$ |

| D1 | チャネル 2,3 処理順序                                                           |

|----|-------------------------------------------------------------------------|

| 0  | CCDIN2 → CCDIN3 → CCDIN2 → CCDIN3(デフォルト)                                |

| 1  | $CCDIN3 \rightarrow CCDIN2 \rightarrow CCDIN3 \rightarrow CCDIN2 \dots$ |

| D0 | チャネル 4,5 処理順序                                                     |

|----|-------------------------------------------------------------------|

| 0  | CCDIN4 → CCDIN5 → CCDIN4 → CCDIN5(デフォルト)                          |

| 1  | $CCDIN5 \rightarrow CCDIN4 \rightarrow CCDIN5 \rightarrow CCDIN4$ |

一つの ADC に対応する入力チャネルペアの処理順序を選択します。処理順序はペアごとに設定できます。このレジスタは 4 チャネルモード 5bit 幅出力または 6 チャネルモード 5bit 幅出力のとき有効です。本データシート中の図はチャネル処理順序がデフォルト設定の時のものです。

# □ R2~R7 レジスタ

# ■ D7-D0 オフセットデータ

| D7-D0          | オフセット電圧 | 負極モード時           | 正極モード時     |  |

|----------------|---------|------------------|------------|--|

| (ストレートバイナリ)    |         |                  |            |  |

| 11111111       | -200mV  | 白側へ最大シフト         | 黒側へ最大シフト   |  |

| 11111110       | :       | (ADC コード大)       | (ADC コード小) |  |

| :              | :       | <b>^</b>         |            |  |

| 10000001       | -1.6mV  |                  |            |  |

| 1000000(デフォルト) | 0mV     |                  | •          |  |

| 01111111       | 1.6mV   |                  | <b>\</b>   |  |

| :              | :       | <br>  (ADC コード小) | (ADC コード大) |  |

| 0000001        | :       | 黒側へ最大シフト         | 白側へ最大シフト   |  |

| 00000000       | 200mV   | MINJ VAX/V/ /    |            |  |

# □ R8~RD レジスタ

■ D7-D0 PGA ゲインデータ

設定コードとゲイン(理想値)の関係は次の式で表されます。

$$Gain(x) = \frac{8}{14.8} \times \frac{656 + 3x}{96 + 255 - x}$$

ここで x はレジスタ設定値、0≤ x ≤255

デフォルト x=0

図 3 PGA ゲイン曲線(理想値)

www.DataShasAHI KASEI [AK8432]

### 動作説明

### ■ センサ I/F モード

入力信号のサンプリング方法として CDS モードとクランプモード、DC 直結モードの 3 つのモードがあります。 センサ I/F モードレジスタ(R0,D7~D6)で使用するモードを選択してください。

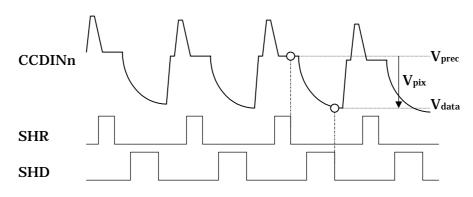

### ・ CDS モード

センサ出力信号の画素毎の基準レベル  $V_{prec}$  とデータレベル  $V_{data}$  の差  $V_{pix}$  をその画素のレベルとして処理するモードです。SHR でセンサ信号のリファレンスレベルを、SHD でセンサ信号のデータレベルをサンプリングします。サンプリングポイントは SHR,SHD とも立下りエッジです。レジスタで SHR,SHD の極性を反転した場合(R1,D7=1)は立ち上がりエッジがサンプリングポイントになります。

図 4 CDS モードタイミング概要

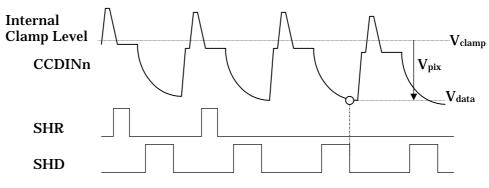

### ・クランプモード

内部で発生するクランプレベル  $V_{\text{clamp}}$  とセンサ出力信号のデータレベル  $V_{\text{data}}$  の差  $V_{\text{pix}}$  をその画素のレベルとして処理するモードです。 SHD でセンサ信号のデータレベルをサンプリングします。

図 5 クランプモードタイミング概要

#### ・ DC 直結モード

外部から REFINn ピンに入力した基準レベルとセンサ出力信号のデータレベル  $V_{data}$  の差  $V_{pix}$  をその画素のレベルとして処理するモードです。 例えばセンサ出力信号に基準となるレベルが無いときにこのモードを使います。 SHD でセンサ信号のデータレベルをサンプリングします。 SHR は使われませんので Low または High に固定してください。

<MS0282-J-01> 2004/09

www.DataSlasAHI KASEI [AK8432]

図 6 DC 直結モードタイミング概要

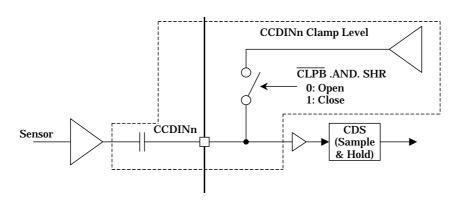

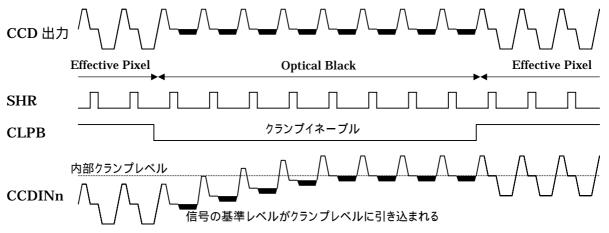

### ■ クランプ動作

CDS モードおよびクランプモードのときはセンサ信号の基準 DC レベルを LSI の内部基準レベルに合わせるためクランプを行います。クランプ動作は CLPB と SHR で制御され、CLPB=Lowかつ SHR=High(SHR,SHD 極性反転時は Low)の区間でクランプスイッチが閉じ、CCDINn(n=0~5)端子が内部のクランプレベルに引き込まれます。REFINn(n=0~5)も同様にクランプが行われます。CDS モードの時は CLPB を Low に固定して常時クランプが掛かるようにしてください。

図 7 クランプ回路概要

図 8 クランプ動作タイミング概要

www.DataSASAHI KASEI

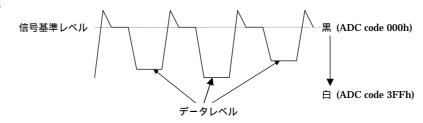

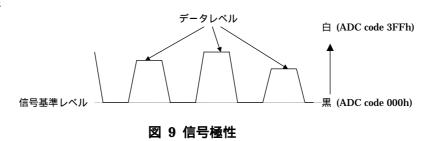

#### ■ 信号極性

正と負、両方の信号極性に対応しています。センサに合わせて信号極性レジスタ(R0,D5)で選択します。一般に CCD は負極性、CIS は正極性です。センサ I/F モードの設定とは無関係に、どちらの極性でも選択できます。

#### · 負極性

### • 正極性

### ■ 出力データコントロール

ADC 出力データはデータ幅レジスタ(R1,D3)設定により 5bit 幅もしくは 10bit 幅で出力されます。5bit 幅を選択したときは、3 つの ADC それぞれに対応する 5bit バス DA4~0,DB4~0,DC4~0 からデータが出力されます。10bit 幅を選択したとき、データは DA4(MSB)~DA0と DB4~DB0(LSB)の 10 ピンを使って出力されます。5bit 幅のときデータは ADCK の立ち上がりで上位 5bit が、ADCK の立下りで下位 5bit が出力されます。10bit 幅のときは立ち上がりと立下りで違うチャネルのデータが出力されます。また、10bit 幅のときは ADCK 周波数レジスタ(R0,D1)設定により、ADCK の立ち下りだけでデータを出力することができます。このとき ADCK は全チャネルの画素レートの総和(総画素レート)の周波数で入力する必要があります。1CHモードで5bit 幅出力のときのDB4~0,DC4~0のような使われないバスは Low を出力します。

#### ■ ADCK

A/D 変換レートモードと総画素レートモード

ADCK は ADC の変換タイミングと ADC データ出力タイミングを作ります。 ADCK の立ち上がりエッジと立ち下がりエッジでデータを出力させるか、 ADCK の立ち上がりエッジだけでデータを出力させるかを ADCK 周波数モードレジスタで選択できます。

ADCK の立ち上がりエッジと立下りエッジでデータを出力するのが A/D 変換レートモードです。 A/D 変換レートモードのときは ADC の変換レートと同じ周波数の ADCK を入力してください。 ADCK の立ち上がりエッジだけでデータを出力させるのが総画素レートモードです。 総画素レートモードでは有効なチャネルの画素レートの総和と同じ周波数の ADCK を入力してください。 例えば 3 チャネルモードで 1 チャネル当たり 20MHz のセンサ信号を処理する場合、A/D 変換

<MS0282-J-01> 2004/09

www.DataSheet4U.com

www.DataSASAH/ KASEI

レートモード時は ADCK は ADC の変換レートの 20MHz のクロックを入力します。一方、総画素レートモード時は ADCK として 20MHz×3=60MHz のクロックを入力します。

### 最大変換レート

ADC データ出力バッファ DA0~4,DB0~4,DC0~4 の最大動作速度は 80Mbps で設計されています。ADCK 周波数モードとして総画素レートモードを選択したとき、3CH モードと6CH モードでのチャネルあたりの最大サンプリングレートはこの出力バッファの速度で制限されます。たとえば 6CH モードの場合、チャネルあたりの最大変換レートは 20MSPS ではなく 80MSPS/6=13.3MSPS になります。

チャネル数と ADCK 周波数、データ幅の可能な組み合わせと、そのときのチャネル当たりの最大変換レートを次の表に示します。

|       | A/D 変換レートモード |         |          | 総画素レートモード |         |          |

|-------|--------------|---------|----------|-----------|---------|----------|

| チャネル数 | 5bit 幅       | 10bit 幅 | 最大変換     | 5bit 幅    | 10bit 幅 | 最大変換     |

|       |              |         | [SPS/CH] |           |         | [SPS/CH] |

| 1     | 可            | 可       | 40M      | -         | 可注1     | 40M      |

| 2     | 可            | 可       | 40M      | =         | 可       | 40M      |

| 3     | 可            | -       | 40M      | -         | 可       | 26.6M    |

| 4     | 可            | 可       | 20M      | =         | 可       | 20M      |

| 6     | 可            | =       | 20M      | =         | 可       | 13.3M    |

注1 1CH モード 10bit 幅出力時、A/D 変換レートモードと総画素レートモードは同じタイミング波形になります。 デフォルトの A/D 変換レートモードでお使いください。

ただし、DC 直結モード時の最大変換レートは ADCK 周波数モードによらず次のようになります。

| チャネル数 | 最大変換レート[SPS/CH] |  |  |  |

|-------|-----------------|--|--|--|

| 1     | 10M             |  |  |  |

| 2     | 10M             |  |  |  |

| 3     | 10M             |  |  |  |

| 4     | 8.3M            |  |  |  |

| 6     | 8.3M            |  |  |  |

www.DataShsAHI-KASEI [AK8432]

#### ■ シリアル I/F

コントロールレジスタへの書き込みと読み出しは4線式のシリアルインターフェースで行います。 SDENB が Low の区間の SDIN データが SDCLK の立ち上がリエッジで取り込まれます。 SDIN の先頭ビットが 0 の時はレジスタへの書き込み、1 の時はレジスタからの読み出しになります。第 2,3 ビット(C1,C0)はそれぞれ CE1,CE0 ピンと対応し、論理レベルが C1=CE1 かつ C0=CE0 のときだけ書き込みまたは読み出しが行われます。第 4 ビットは 0 でなければなりません。第 5~8 ビットはレジスタのアドレスで、第 5 ビットが MSB、第 5 ビットが LSB です。第 9~16 ビットはレジスタのデータで、第 5 ビットが MSB(=D7)、第 5 ビットが LSB(=D0)です。

#### ■ リセット

電源を立ち上げたときレジスタの値はテスト用のレジスタを含めて不定です。テスト用レジスタが通常の動作に影響するのを避けるため電源を立ち上げた直後にリセットを行ってください。 RESETB ピンを Low にするとレジスタがリセットされ各レジスタがデフォルト値になると共に、テスト用レジスタが通常動作に必要な設定値になります。 RESETB の Low 幅は 100ns 以上としてください。 リセットの後 RESETB ピンを High に戻し、 各レジスタに必要な値を書き込んでください。 電源立ち上げ後にリセットを行わない場合は、 テスト用レジスタに初期値を書き込んでください。

### ■ パワーダウン

動作モードレジスタ R0,D0 を 1 にすると AK8432 はパワーダウンモードに入ります。パワーダウンモードではアナログ部の電流が止まると共にロジック部への動作クロック供給も止まります。パワーダウン時はリファレンス電圧 VCOM も VCOM も VCOM が正常な電圧に安定するまでの待ち時間が必要です。

www.DataSlasAHI KASEI [AK8432]

<MS0282-J-01> 2004/09

www.DataSlasaHI Kasei

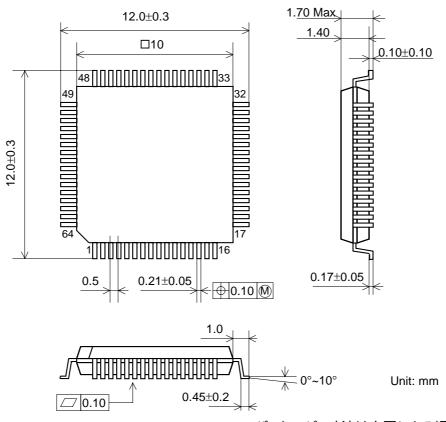

# 外形寸法図

パッケージ、寸法は変更になる場合があります。

# マーキング

- (1) 1 ピン表示 (面取りした角が 1 ピン)

- (2) 旭化成マイクロシステム ロゴ

- (3) マーケティングコード: AK8432VQ

- (4) デートコード: XXXXXXX (7桁)

上位4桁:週コード

下位3桁: 社内管理コード

www.DataSlasAHI KASEI [AK8432]

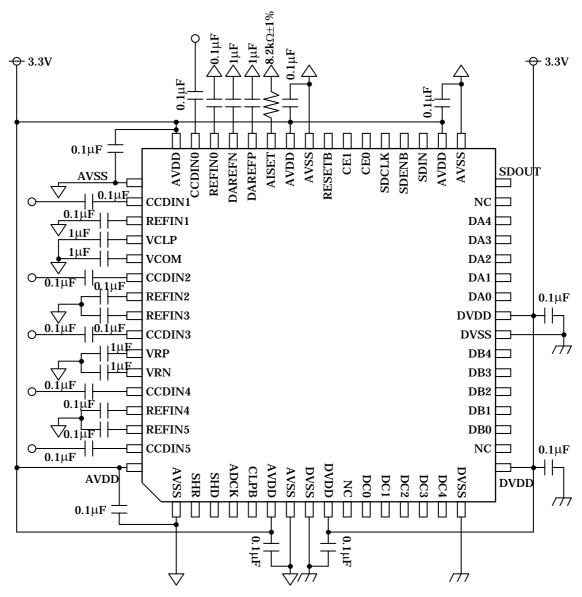

# 外部回路例

### ■ CDSモード

上記は参考例です。コンデンサの容量値はシステムに応じて最適な値を選択してください。

図 12 CDS モード

www.DataSlasathi. Kasei

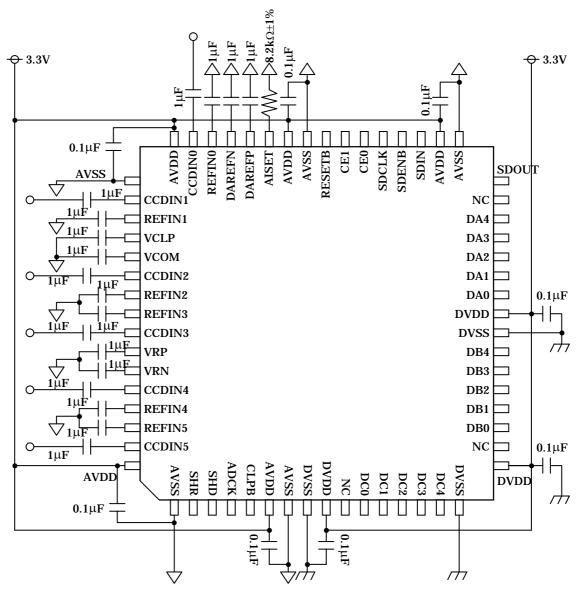

# ■ クランプモード

上記は参考例です。コンデンサの容量値はシステムに応じて最適な値を選択してください。

図 13 クランプモード

www.DataSlasaHI Kasei

# ■ DC 直結モード

上記は参考例です。コンデンサの容量値はシステムに応じて最適な値を選択してください。

図 14 DC 直結モード

www.DataShashHi Kasei [AK8432]

### 重要な注意事項 -

本書に記載された製品、および、製品の仕様につきましては、製品改善のために予告なく変更することがあります。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社特約店営業担当にご確認下さい。

本書に掲載された情報・図面の使用に起因した第三者の所有する特許権、工業所有権、その他の権利に対する侵害につきましては、当社はその責任を負うものではありませんので、ご了承下さい。

本書記載製品が、外国為替および、外国貿易管理法に定める戦略物資(役務を含む)に該当する場合、輸出する際に同法に基づく輸出許可が必要です。

医療機器、安全装置、航空宇宙用機器、原子力制御用機器など、その装置・機器の故障や動作不良が、直接または間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を要求される用途に弊社製品を使用される場合は、必ず事前に弊社代表取締役の書面による同意をお取り下さい。

この同意書を得ずにこうした用途に弊社製品を使用された場合、弊社は、その使用から生ずる損害等の責任を一切負うものではありませんのでご了承下さい。

お客様の転売等によりこの注意事項の存在を知らずに上記用途に弊社製品が使用され、その使用から損害等が生じた場合は全てお客様にてご負担または補償して頂きますのでご了承下され。