LDC1051

SNOSCY0-MARCH 2014

# LDC1051: 8-bit Rp only Inductance-to-Digital Converter with SPI

## **Features**

- Remote Sensor Placement (Decoupling The LDC From Harsh Environments)

- High Durability (By Virtue Of Contactless Operation)

- Higher Flexibility For System Design (Using Coils Or Springs As Sensors)

- Insensitive to Non-conductive Environmental Interferers (such As Dirt, Dust, Oil etc.)

- Magnet-free Operation

- Supply Voltage: 5 V, typ

- Supply Voltage, IO: 1.8V to 5.5V Stand-by Current: 250uA, typ

- Rp Resolution: 8-bit

- LC Frequency Range: 5kHz to 5MHz

## **Applications**

- **Proximity Sensing**

- Level Sensing

- Lateral Position Sensing

## 3 Description

Inductive sensing is a contactless, short-range sensing technology enabling high-resolution and lowcost position sensing of conductive targets, even in harsh environments. Using a coil or spring as a sensor, the LDC1051 inductance-to-digital converter provides system designers a way to achieve high performance and reliability at a lower system cost than other competing solutions.

The LDC1051 is pin compatible with the LDC1000 (16-bit Rp/24-bit L) and the LDC1041 (8-bit Rp/24-bit L). This family of devices offers system designers different resolution options based on their application and system requirements.

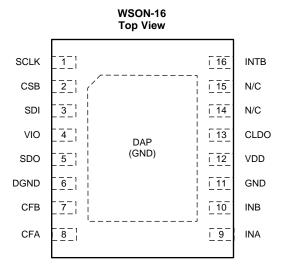

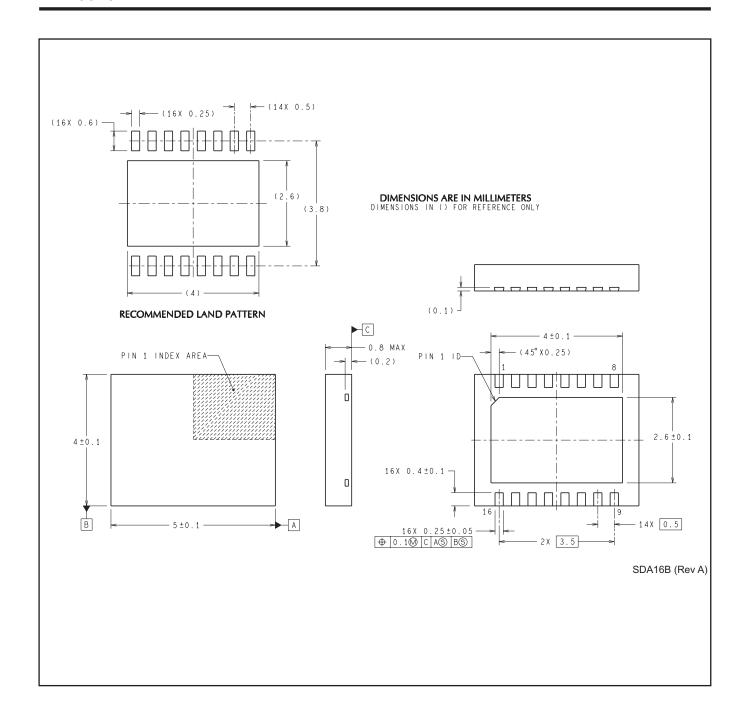

The LDC1051 is available in a 5mm x 4mm WSON-16 package. Device programming via SPI allows for easy configuration using a microcontroller.

#### **Device Information**

| ORDER NUMBER | PACKAGE   | BODY SIZE   |

|--------------|-----------|-------------|

| LDC1051NHRT  | WSON (16) | 5 mm × 4 mm |

| LDC1051NHRR  | WSON (16) | 5 mm × 4 mm |

| LDC1051NHRJ  | WSON (16) | 5 mm × 4 mm |

## **Axial Distance Sensing Application**

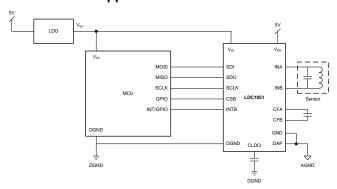

## **Application Schematic**

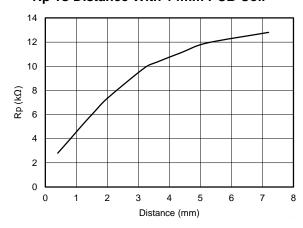

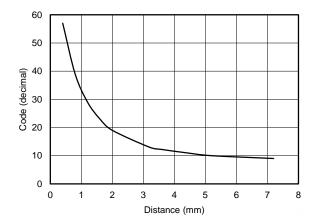

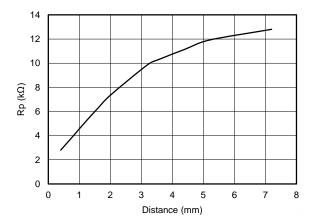

## Rp vs Distance With 14mm PCB Coil

# **Table of Contents**

| 1 | Features 1                           | 7.3 Feature Description                             |

|---|--------------------------------------|-----------------------------------------------------|

| 2 | Applications 1                       | 7.4 Device Functional Modes 1                       |

| 3 | Description 1                        | 7.5 Programming 1                                   |

| 4 | Revision History2                    | 7.6 Register Map and Description 1                  |

| 5 | Terminal Configuration and Functions | 8 Applications and Implementation 2                 |

| 6 | Specifications4                      | 8.1 Application Information 2                       |

| U | 6.1 Absolute Maximum Ratings         | 8.2 Typical Applications 2                          |

|   | 6.2 Handling Ratings                 | 9 Power Supply Recommendations 2                    |

|   | 6.3 Recommended Operating Conditions | 10 Layout2                                          |

|   | 6.4 Thermal Information              | 10.1 Layout Guidelines 2                            |

|   | 6.5 Electrical Characteristics 5     | 10.2 Layout Example 2                               |

|   | 6.6 Timing Requirements              | 11 Device and Documentation Support 2               |

|   | 6.7 Typical Characteristics          | 11.1 Trademarks 2                                   |

| 7 | Detailed Description 8               | 11.2 Electrostatic Discharge Caution 2              |

| • | 7.1 Overview 8                       | 11.3 Glossary2                                      |

|   | 7.2 Functional Block Diagram         | 12 Mechanical, Packaging, and Orderable Information |

# 4 Revision History

| DATE       | REVISION | NOTES            |  |  |

|------------|----------|------------------|--|--|

| March 2014 | *        | Initial release. |  |  |

# 5 Terminal Configuration and Functions

## **Terminal Functions**

| TERMINAL NAME | TERMINAL<br>NO. | TERMINAL<br>TYPE | DESCRIPTION                                                                                                                                                                   |  |  |  |

|---------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SCLK          | 1               | DO               | SPI clock input. SCLK is used to clock-out/clock-in the data from/into the chip                                                                                               |  |  |  |

| CSB           | 2               | DI               | SPI CSB(Chip Select Bar). Multiple devices can be connected on the same SPI bus and CSB can be used to select the device to be communicated with                              |  |  |  |

| SDI           | 3               | DI               | SPI Slave Data In (Master Out Slave In). This should be connected to the Master Out Slave In of the master                                                                    |  |  |  |

| VIO           | 4               | Р                | Digital IO Supply                                                                                                                                                             |  |  |  |

| SDO           | 5               | DO               | SPI Slave Data Out (Master In Slave Out). It is high impedance when CSB is high                                                                                               |  |  |  |

| DGND          | 6               | Р                | Digital ground                                                                                                                                                                |  |  |  |

| CFB           | 7               | Α                | LDC filter capacitor                                                                                                                                                          |  |  |  |

| CFA           | 8               | Α                | LDC filter capacitor                                                                                                                                                          |  |  |  |

| INA           | 9               | Α                | External LC Tank. Connect to external LC tank                                                                                                                                 |  |  |  |

| INB           | 10              | Α                | External LC Tank. Connect to external LC tank                                                                                                                                 |  |  |  |

| GND           | 11              | Р                | Analog ground                                                                                                                                                                 |  |  |  |

| VDD           | 12              | Р                | Analog supply                                                                                                                                                                 |  |  |  |

| CLDO          | 13              | Α                | LDO bypass capacitor. A 56nF capacitor should be connected from this Terminal to GND                                                                                          |  |  |  |

| N/C           | 14              | N/C              | No Connection                                                                                                                                                                 |  |  |  |

| N/C           | 15              | N/C              | No Connection                                                                                                                                                                 |  |  |  |

| INTB          | 16              | DO               | Configurable interrupt. This Terminal can be configured to behave in 3 different ways by programing the INT Terminal mode register. Either threshold detect, wakeup, or DRDYB |  |  |  |

| DAP           | 17              | Р                | Connect to GND                                                                                                                                                                |  |  |  |

# TEXAS INSTRUMENTS

# 6 Specifications

# 6.1 Absolute Maximum Ratings

|                                               | MIN  | MAX            | UNIT |

|-----------------------------------------------|------|----------------|------|

| Analog Supply Voltage (V <sub>DD</sub> – GND) |      | 6              | V    |

| IO Supply Voltage (V <sub>IO</sub> – GND)     |      | 6              | V    |

| Voltage on any Analog Terminal                | -0.3 | $V_{DD} + 0.3$ | V    |

| Voltage on any Digital Terminal               | -0.3 | $V_{10} + 0.3$ | V    |

| Input Current on INA and INB                  |      | 8              | mA   |

| Junction Temperature, T <sub>J</sub>          |      | 150            | °C   |

# 6.2 Handling Ratings

|                  |                                              | MIN | MAX | UNIT |

|------------------|----------------------------------------------|-----|-----|------|

| T <sub>stg</sub> | Storage Temperature range                    | -65 | 150 | °C   |

| V <sub>ESD</sub> | Human Body Model (HBM) ESD stress voltage    | 1k  | 1k  | V    |

|                  | Charge Device Model (CDM) ESD stress voltage | 250 | 250 | V    |

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| 5 (                                           | MIN  | MAX  | UNIT |

|-----------------------------------------------|------|------|------|

| Analog Supply Voltage (V <sub>DD</sub> – GND) | 4.75 | 5.25 | V    |

| IO Supply Voltage (V <sub>IO</sub> – GND)     | 1.8  | 5.25 | V    |

| $V_{DD}$ - $V_{IO}$                           | 0    |      | V    |

| Operating Temperature, T <sub>A</sub>         | -40  | 125  | °C   |

## 6.4 Thermal Information

|               | THERMAL METRIC <sup>(1)</sup>          | NHR<br>(16-TERMINALS) | UNIT |

|---------------|----------------------------------------|-----------------------|------|

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | 28                    | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics(1)

Unless otherwise specified, all limits ensured for  $T_A = T_J = 25$ °C,  $V_{DD} = 5$  V,  $V_{IO} = 3.3$  V

|                         | PARAMETER                       | TEST CONDITIONS                                              | MIN <sup>(2)</sup>    | TYP <sup>(3)</sup>           | MAX <sup>(2)</sup>       | UNIT                  |

|-------------------------|---------------------------------|--------------------------------------------------------------|-----------------------|------------------------------|--------------------------|-----------------------|

| POWER                   |                                 |                                                              |                       |                              |                          |                       |

| $V_{DD}$                | Analog supply voltage           |                                                              | 4.75                  | 5                            | 5.25                     | V                     |

| V <sub>IO</sub>         | IO supply voltage               | V <sub>IO</sub> ≤V <sub>DD</sub>                             | 1.8                   | 3.3                          | 5.25                     | V                     |

| I <sub>DD</sub>         | Supply current, V <sub>DD</sub> | Does not include sensor current. (4)                         |                       | 1.7                          | 2.3                      | mA                    |

| I <sub>VIO</sub>        | IO supply current               | Static current                                               |                       |                              | 14                       | μΑ                    |

| I <sub>DD_LP</sub>      | Stand-by mode supply current    |                                                              |                       | 250                          |                          | μΑ                    |

| t <sub>START</sub>      | Start-Up Time                   | From POR to ready-to-convert.                                |                       | 2                            |                          | ms                    |

| LDC                     |                                 |                                                              |                       |                              |                          |                       |

| f <sub>sensor_MIN</sub> | Minimum sensor frequency        |                                                              |                       | 5                            |                          | kHz                   |

| $f_{ m sensor\_MAX}$    | Maximum sensor frequency        |                                                              |                       | 5                            |                          | MHz                   |

| A <sub>sensor_MIN</sub> | Minimum sensor amplitude        |                                                              |                       | 1                            |                          | V <sub>PP</sub>       |

| A <sub>sensor_MAX</sub> | Maximum sensor amplitude        |                                                              |                       | 4                            |                          | $V_{PP}$              |

| t <sub>REC</sub>        | Recovery time                   | Oscillation start-up time after Rp under-<br>range condition |                       | 10                           |                          | 1/f <sub>sensor</sub> |

| Rp Min                  | Minimum sensor Rp range         |                                                              |                       | 798                          |                          | Ω                     |

| Rp Max                  | Maximum Sensor Rp range         |                                                              |                       | 3.93                         |                          | МΩ                    |

| Rp Res                  | Rp measurement resolution       |                                                              |                       | 8                            |                          | Bits                  |

| t <sub>S_MIN</sub>      | Minimum response time           | Minimum programmable settling time of digital filter         | 1                     | 92 x 1 / f <sub>sensor</sub> |                          | S                     |

| t <sub>S_MAX</sub>      | Maximum response time           | Maximum programmable settling time of digital filter         |                       | 6144 × 1 / f sensor          |                          | s                     |

| DIGITAL I/O             | CHARACTERISTICS                 |                                                              |                       |                              |                          |                       |

| V <sub>IH</sub>         | Logic 1 input voltage           |                                                              | 0.8 × V <sub>IO</sub> |                              |                          | V                     |

| V <sub>IL</sub>         | Logic 0 input voltage           |                                                              |                       |                              | 0.2 ×<br>V <sub>IO</sub> | V                     |

| V <sub>OH</sub>         | Logic 1 output voltage          | I <sub>SOURCE</sub> = 400 μA                                 |                       | V <sub>IO</sub> - 0.3        |                          | V                     |

| V <sub>OL</sub>         | Logic 0 output voltage          | I <sub>SINK</sub> = 400 μA                                   |                       |                              | 0.3                      | V                     |

| I <sub>IOHL</sub>       | Digital IO leakage current      |                                                              | -500                  |                              | 500                      | nA                    |

<sup>(1)</sup> Electrical Characteristics Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that TJ = TA. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

(4) LC tank current depends on the Q-factor of the tank, distance and material of the target.

<sup>(2)</sup> Limits are specified by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

# TEXAS INSTRUMENTS

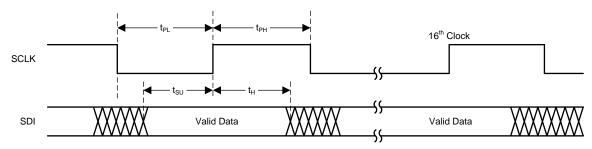

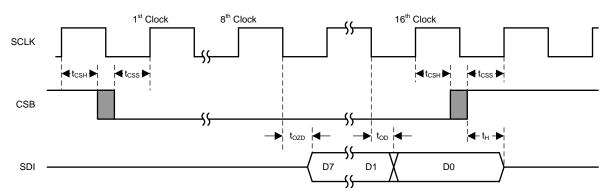

## 6.6 Timing Requirements

Unless otherwise noted, all limits specified at  $T_A$  = 25°C,  $V_{DD}$  = 5,  $V_{IO}$  = 3.3, 10 pF capacitive load in parallel with a 10 k $\Omega$  load on the SDO terminal. Specified by design; not production tested.

|                    | PARAMETER                   |                                                      | MIN                     | TYP                  | MAX | UNIT |

|--------------------|-----------------------------|------------------------------------------------------|-------------------------|----------------------|-----|------|

| $f_{\sf SCLK}$     | Serial Clock Frequency      |                                                      |                         |                      | 4   | MHz  |

| t <sub>PH</sub>    | SCLK Pulse Width High       | $f_{\rm SCLK}$ = 4 MHz                               | 0.4 / f <sub>SCLK</sub> |                      |     | S    |

| t <sub>PL</sub>    | SCLK Pulse Width Low        | $f_{\rm SCLK}$ = 4 MHz                               | 0.4 / f <sub>SCLK</sub> |                      |     | S    |

| t <sub>SU</sub>    | SDI Setup Time              |                                                      | 10                      |                      |     | ns   |

| t <sub>H</sub>     | SDI Hold Time               |                                                      | 10                      |                      |     | ns   |

| t <sub>ODZ</sub>   | SDO Driven-to-Tristate Time | Measured at 10% / 90% point                          |                         |                      | 20  | ns   |

| t <sub>OZD</sub>   | SDO Tristate-to-Driven Time | Measured at 10% / 90% point                          |                         |                      | 20  | ns   |

| t <sub>OD</sub>    | SDO Output Delay Time       |                                                      |                         |                      | 20  | ns   |

| t <sub>CSS</sub>   | CSB Setup Time              |                                                      | 20                      |                      |     | ns   |

| t <sub>CSH</sub>   | CSB Hold Time               |                                                      | 20                      |                      |     | ns   |

| t <sub>IAG</sub>   | Inter-Access Gap            |                                                      | 100                     |                      |     | ns   |

| t <sub>DRDYB</sub> | Data ready pulse width      | Data ready pulse at every 1 / ODR if no data is read | 1                       | /f <sub>sensor</sub> |     | S    |

Unless otherwise noted, all limits specified at TA = 25°C, VDD=5.0, VIO=3.3, 10pF capacitive load in parallel with a  $10k\Omega$  load on SDO. Specified by design; not production tested.

Figure 1. Write Timing Diagram

Figure 2. Read Timing Diagram

# 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

## 7 Detailed Description

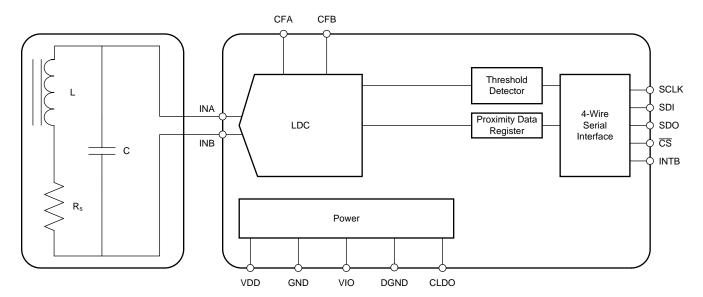

#### 7.1 Overview

The LDC1051 is an Inductance-to-Digital Converter that measures the parallel impedance of an LC resonator. It accomplishes this task by regulating the oscillation amplitude in a closed loop configuration to a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1051 can determine the value of Rp; it returns this as a digital value which is inversely proportional to Rp.

The threshold detector block provides a comparator with hysteresis, with the threshold registers programed and comparator enabled, proximity data register is compared with threshold registers and INTB terminal indicates the output.

The device has a simple 4-wire SPI interface. The INTB terminal provides multiple functions which are programmable with SPI.

The device has separate supplies for Analog and I/O, with analog operating at 5V and I/O at 1.8-5V. The integrated LDO needs a 56nF capacitor connected from CLDO terminal to GND.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

## 7.3.1 Inductive Sensing

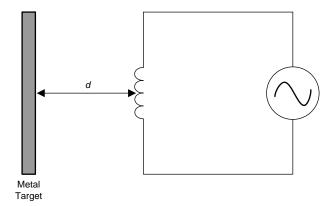

An AC current flowing through a coil will generate an AC magnetic field. If a conductive material, such as a metal target, is brought into the vicinity of the coil, this magnetic field will induce circulating currents (eddy currents) on the surface of the target. These eddy currents are a function of the distance, size, and composition of the target. The eddy currents then generate their own magnetic field, which opposes the original field generated by the coil. This mechanism is best compared to a transformer, where the coil is the primary core and the eddy current is the secondary core. The inductive coupling between both cores depends on distance and shape. Hence the resistance and inductance of the secondary core (eddy current), shows up as a distant dependent resistive and inductive component on the primary side (coil). The figures(Figure 5 to Figure 8) below show a simplified circuit model.

## **Feature Description (continued)**

Figure 5. Inductor With A Metal Target

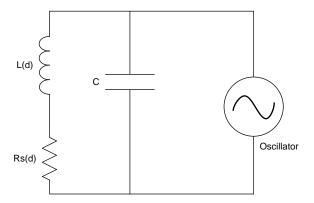

Eddy currents generated on the surface of the target can be modeled as a transformer as shown in Figure 6. The coupling between the primary and secondary coils is a function of the distance and the conductor's characteristics. In Figure 6, the inductance Ls is the coil's inductance, and Rs is the coil's parasitic series resistance. The inductance L(d), which is a function of distance d, is the coupled inductance of the metal target. Likewise, R(d) is the parasitic resistance of the eddy currents and is also a function of distance.

Figure 6. Metal Target Modeled As L And R With Circulating Eddy Currents

Generating an alternating magnetic field with just an inductor will consume a large amount of power. This power consumption can be reduced by adding a parallel capacitor, turning it into a resonator as shown in Figure 7. In this manner the power consumption is reduced to the eddy and inductor losses Rs+R(d) only.

Figure 7. LC Tank Connected To Oscillator

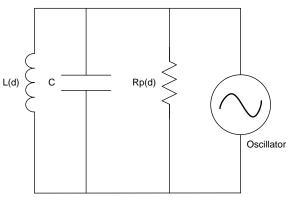

The LDC1051 doesn't measure the series resistance directly; instead it measures the equivalent parallel resonance impedance Rp (see Figure 8). This representation is equivalent to the one shown in Figure 8, where the parallel resonance impedance Rp(d) is given by:

# **Feature Description (continued)**

$$Rp(d) = \frac{Ls + L(d)}{[Rs + R(d)] \times C}$$

(1)

Figure 8. Equivalent Resistance Of Rs in Parallel With LC Tank

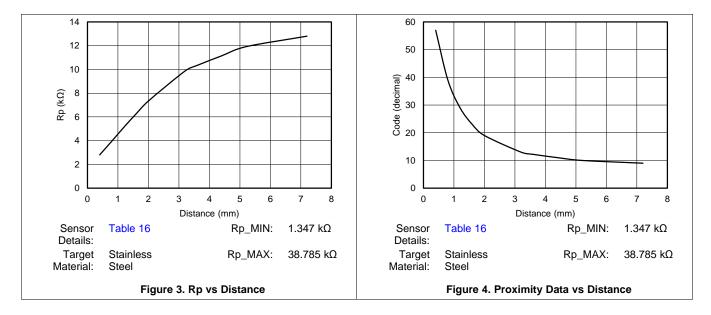

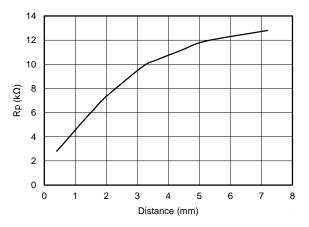

Figure 9 below shows the variation in Rp as a function of distance for a 14mm diameter PCB coil (Sensor Details: Table 16). The target in this example is a section of a 2mm thick stainless steel disk.

Figure 9. Typical Rp vs Distance With 14mm PCB Coil

#### 7.3.2 Measuring Rp with LDC1051

The LDC1051 supports a wide range of LC combinations, with oscillation frequencies ranging from 5kHz to 5MHz and Rp ranging from  $798\Omega$  to  $3.93M\Omega$ . This range of Rp can be viewed as the maximum input range of an ADC. As illustrated in Figure 9, the range of Rp is typically much smaller than the maximum input range supported by the LDC1051. To get better resolution in the desired sensing range, the LDC1051 offers a programmable input range through the Rp\_MIN and Rp\_MAX registers. Refer to Calculation of Rp\_MIN and Rp\_MAX below for how to set these registers.

When the sensor's resonance impedance Rp drops below the programed Rp\_MIN, the LDC's Rp output will clip at its full scale output. This situation could, for example, happen when a target comes too close to the coil.

Product Folder Links: *LDC1051*

**ISTRUMENTS**

## **Feature Description (continued)**

Figure 10. Transfer Characteristics Of LDC1051 With Rp\_MIN= 1.347 k $\Omega$  And Rp\_MAX= 38.785 k $\Omega$

The resonance impedance can be calculated from the digital output code as follows:

$$Rp = \frac{Rp\_MAX \times Rp\_MIN}{Rp\_MIN \times (1 - Y) + Rp\_MAX \times Y}$$

Where:

- Y=Proximity Data/2<sup>7</sup>

- Rp MAX and Rp MIN are the maximum and minimum Rp values selected in the respective registers

- Proximity data is the LDC output, register address 0x22.

(2)

**Example:** If Proximity data (address 0x22) is 50, Rp\_MIN is 2.394 k $\Omega$ , and Rp\_MAX is 38.785 k $\Omega$ , the resonance impedance is given by:

$Y=50/2^7=0.3906$

$Rp = (38785*2394)/(2394 \times (1-0.3906) + 38785 \times 0.3906) = (92851290)/(15149.421 + 1458.9036)$

$Rp = 5.59 k\Omega$

#### 7.4 Device Functional Modes

## 7.4.1 Power Modes

The LDC1051 has two power modes:

- · Active Mode: In this mode the Proximity data conversion is enabled.

- Stand-by Mode: This is the default mode on device power-up. In this mode conversion is disabled.

#### 7.4.2 INTB terminal Modes

The INTB terminal is a configurable output terminal which can be used to drive an interrupt on an MCU. The LDC1051 provides three different modes on INTB terminal:

- 1. Comparator Mode

- 2. Wake-Up Mode

- 3. DRDY Mode

LDC1051 has built-in High and Low trigger threshold registers which can be used as a comparator with programmable hysteresis or in a special mode which can be used to wake-up an MCU. These modes are explained in detail below.

# TEXAS INSTRUMENTS

## **Device Functional Modes (continued)**

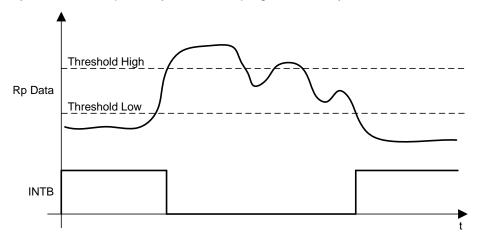

## 7.4.2.1 Comparator Mode

In the Comparator mode, the INTB terminal is asserted or deasserted when the proximity register value increases above Threshold High or decreases below Threshold Low registers respectively. In this mode, the LDC1051 essentially behaves as a proximity switch with programmable hysteresis.

Figure 11. Behavior Of INTB Terminal In Comparator Mode

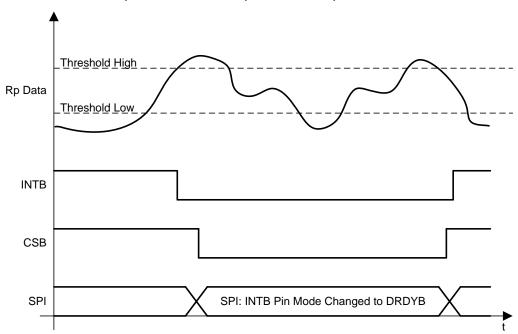

#### 7.4.2.2 Wake-Up Mode

In Wake-Up mode, the INTB terminal is asserted when proximity register value increases above Threshold High and de-asserted when wake-up mode is disabled in INTB terminal mode register.

This mode can be used to wake-up an MCU from sleep, to conserve power.

Figure 12. Behavior Of INTB Terminal In Wake-Up Mode

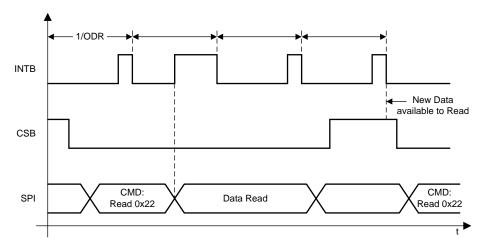

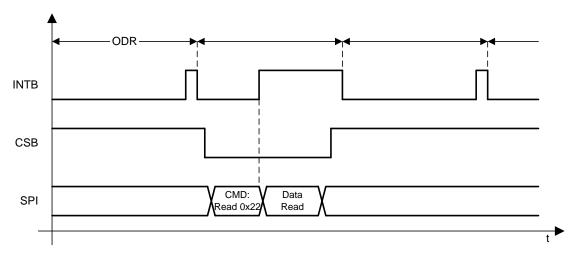

## 7.4.2.3 DRDYB Mode

In DRDY(Data Ready) mode, the INTB terminal is asserted every time the conversion data is available and deasserted once the read command on register 0x22 is registered internally; if the read is in progress, the terminal is pulsed instead. The valid condition for new data availability is CSB high and DRDYB falling edge.

# **Device Functional Modes (continued)**

Figure 13. Behavior of INTB Terminal in DRDYB Mode with SPI Extending Beyond Subsequent Conversions

Figure 14. Behavior Of INTB Terminal In DRDYB Mode with SPI Reading The Data Within Subsequent Conversion

# TEXAS INSTRUMENTS

#### 7.5 Programming

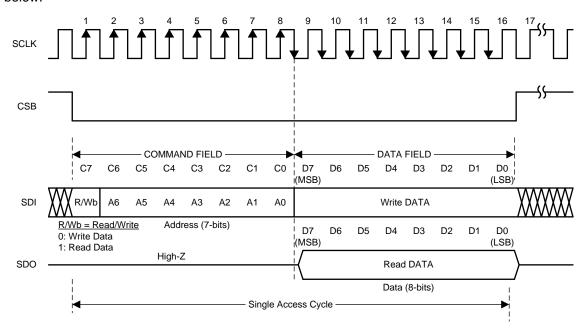

The LDC1051 utilizes a 4-wire SPI to access control and data registers. The LDC1051 is an SPI slave device and does not initiate any transactions.

## 7.5.1 SPI Description

A typical serial interface transaction begins with an 8-bit instruction, which is comprised of a read/write bit (MSB, R=1) and a 7 bit address of the register, followed by a data field which is typically 8 bits. However, the data field can be extended to a multiple of 8 bits by providing sufficient SPI clocks. Refer to the Extended SPI Transactions section below.

Figure 15. Serial Interface Protocol

Each assertion of CSB starts a new register access. The R/Wb bit in the command field configures the direction of the access; a value of 0 indicates a write operation and a value of 1 indicates a read operation. All output data is driven on the falling edge of the serial clock (SCLK), and all input data is sampled on the rising edge of the serial clock (SCLK). Data is written into the register on the rising edge of the 16th clock. It is required to deassert CSB after the 16th clock; if CSB is deasserted before the 16th clock, no data write will occur.

#### 7.5.1.1 Extended SPI Transactions

A transaction may be extended to multiple registers by keeping the CSB asserted beyond the initial 16 clocks. In this mode, the register addresses increment automatically. CSB must be asserted during 8\*(1+N) clock cycles of SCLK, where N is the amount of bytes to write or read during the transaction.

During an extended read access, SDO outputs the register contents every 8 clock cycles after the initial 8 clocks of the command field. During an extended write access, the data is written to the registers every 8 clock cycles after the initial 8 clocks of the command field.

# 7.6 Register Map and Description

# Table 1. Register Map<sup>(1)(2)(3)</sup>

| Register<br>Name                    | Address | Direction | Default | Bit 7                                     | Bit 6 | Bit 5       | Bit 4      | Bit 3       | Bit 2 | Bit 1   | Bit 0        |

|-------------------------------------|---------|-----------|---------|-------------------------------------------|-------|-------------|------------|-------------|-------|---------|--------------|

| Device ID                           | 0x00    | RO        | 0x84    |                                           |       |             | Devi       | ce ID       |       |         |              |

| Rp_MAX                              | 0x01    | R/W       | 0x0E    |                                           |       |             | Rp Ma      | ximum       |       |         |              |

| Rp_MIN                              | 0x02    | R/W       | 0x14    |                                           |       |             | Rp Mi      | nimum       |       |         |              |

| Watchdog<br>Timer<br>Frequency      | 0x03    | R/W       | 0x45    |                                           |       |             | Min Sensor | · Frequency |       |         |              |

| LDC<br>Configuration                | 0x04    | R/W       | 0x1B    | Reserved(000) Amplitude Response Time     |       |             |            | me          |       |         |              |

| Reserved                            | 0x05    | RO        | 0x01    | Reserved(0000001)                         |       |             |            |             |       |         |              |

| Reserved                            | 0x06    | R/W       | 0xFF ?? | Reserved                                  |       |             |            |             |       |         |              |

| Comparator<br>Threshold<br>High MSB | 0x07    | R/W       | 0xFF    | Threshold High MSB                        |       |             |            |             |       |         |              |

| Reserved                            | 0x08    | R/W       | 0x00 ?? | Reserved                                  |       |             |            |             |       |         |              |

| Comparator<br>Threshold<br>Low MSB  | 0x09    | R/W       | 0x00    |                                           |       |             | Threshold  | Low MSB     |       |         |              |

| INTB<br>Terminal<br>Configuration   | 0x0A    | R/W       | 0x00    |                                           | Re    | eserved(000 | 00)        |             | I     | NTB_MOD | E            |

| Power<br>Configuration              | 0x0B    | R/W       | 0x00    |                                           |       | Res         | erved(0000 | 000)        |       |         | PWR_M<br>ODE |

| Status                              | 0x20    | RO        |         | OSC DRDYB Wake-up Compara Do Not Care tor |       |             |            |             |       |         |              |

| Reserved                            | 0x21    | RO        |         | Reserved(00000000)                        |       |             |            |             |       |         |              |

| Proximity<br>Data                   | 0x22    | RO        |         | Proximity Data                            |       |             |            |             |       |         |              |

| Reserved                            | 0x23    | RO        |         | Reserved                                  |       |             |            |             |       |         |              |

| Reserved                            | 0x24    | RO        |         |                                           |       |             | Rese       | erved       |       |         |              |

| Reserved                            | 0x25    | RO        |         |                                           |       |             | Rese       | erved       |       |         |              |

<sup>(1)</sup> Values of register fields which are unused should be set to default values only.

(2) Registers 0x01 through 0x05 are Read Only when the part is awake (PWR\_MODE bit is SET)

(3) R/W: Read/Write. RO: Read Only. WO: Write Only.

## Table 2. Revision ID

| Address = 0x00, Default=0x84, Direction=RO |             |                         |  |  |  |

|--------------------------------------------|-------------|-------------------------|--|--|--|

| Bit Field Field Name Description           |             |                         |  |  |  |

| 7:0                                        | Revision ID | Revision ID of Silicon. |  |  |  |

## Table 3. Rp\_MAX

| Address = 0x01, Default=0x0E, Direction=R/W |            |                                                                                                                             |

|---------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------|

| Bit Field                                   | Field Name | Description                                                                                                                 |

| 7:0                                         | Rp Maximum | Maximum Rp that LDC1051 needs to measure. Configures the input dynamic range of LDC1051. See Table 4 for register settings. |

# Table 4. Register Settings for Rp\_MAX

| Register setting | Rp (kΩ)  |

|------------------|----------|

| 0x00             | 3926.991 |

| 0x01             | 3141.593 |

| 0x02             | 2243.995 |

| 0x03             | 1745.329 |

| 0x04             | 1308.997 |

| 0x05             | 981.748  |

| 0x06             | 747.998  |

| 0x07             | 581.776  |

| 0x08             | 436.332  |

| 0x09             | 349.066  |

| 0x0A             | 249.333  |

| 0x0B             | 193.926  |

| 0x0C             | 145.444  |

| 0x0D             | 109.083  |

| 0x0E             | 83.111   |

| 0x0F             | 64.642   |

| 0x10             | 48.481   |

| 0x11             | 38.785   |

| 0x12             | 27.704   |

| 0x13             | 21.547   |

| 0x14             | 16.160   |

| 0x15             | 12.120   |

| 0x16             | 9.235    |

| 0x17             | 7.182    |

| 0x18             | 5.387    |

| 0x19             | 4.309    |

| 0x1A             | 3.078    |

| 0x1B             | 2.394    |

| 0x1C             | 1.796    |

| 0x1D             | 1.347    |

| 0x1E             | 1.026    |

| 0x1F             | 0.798    |

Product Folder Links: LDC1051

NSTRUMENTS

# Table 5. Rp\_MIN

|         | Address = 0x02, Default=0x14, Direction=R/W |            |                                                                                                                                 |

|---------|---------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| Bit Fie | ld                                          | Field Name | Description                                                                                                                     |

| 7:0     |                                             | Rp Minimum | Minimum Rp that LDC1051 needs to measure. Configures the input dynamic range of LDC1051. See Table 6 for register settings. (1) |

<sup>(1)</sup> This Register needs a mandatory write as it defaults to 0x14.

# Table 6. Register Settings for Rp\_MIN

| Register setting | Rp (kΩ)  |

|------------------|----------|

| 0x20             | 3926.991 |

| 0x21             | 3141.593 |

| 0x22             | 2243.995 |

| 0x23             | 1745.329 |

| 0x24             | 1308.997 |

| 0x25             | 981.748  |

| 0x26             | 747.998  |

| 0x27             | 581.776  |

| 0x28             | 436.332  |

| 0x29             | 349.066  |

| 0x2A             | 249.333  |

| 0x2B             | 193.926  |

| 0x2C             | 145.444  |

| 0x2D             | 109.083  |

| 0x2E             | 83.111   |

| 0x2F             | 64.642   |

| 0x30             | 48.481   |

| 0x31             | 38.785   |

| 0x32             | 27.704   |

| 0x33             | 21.547   |

| 0x34             | 16.160   |

| 0x35             | 12.120   |

| 0x36             | 9.235    |

| 0x37             | 7.182    |

| 0x38             | 5.387    |

| 0x39             | 4.309    |

| 0x3A             | 3.078    |

| 0x3B             | 2.394    |

| 0x3C             | 1.796    |

| 0x3D             | 1.347    |

| 0x3E             | 1.026    |

| 0x3F             | 0.798    |

## **Table 7. Watchdog Timer Frequency**

|           | Address = 0x03, Default=0x45, Direction=R/W |                                                                                                                                                                                              |     |

|-----------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Bit Field | Field Name                                  | Description                                                                                                                                                                                  |     |

| 7:0       | Min Sensor Frequency                        | Sets the watchdog timer. The Watchdog timer is set based on the lower sensor frequency. $N=68.94\times log_{10}\left(\frac{F}{2500}\right)$ where                                            |     |

|           |                                             | <ul> <li>F is the sensor frequency</li> <li>Example:</li> <li>If Sensor frequency is 1Mhz</li> <li>Min Sensor Frequency=68.94*log10(1M/2500)=Round to nearest integer(179.38)=179</li> </ul> | (3) |

# **Table 8. LDC Configuration**

| Address = 0x04, Default=0x1B, Direction=R/W |               |                                |

|---------------------------------------------|---------------|--------------------------------|

| Bit Field                                   | Field Name    | Description                    |

| 7:5                                         | Reserved      | Reserved to 0                  |

| 4:3                                         | Amplitude     | Sets the oscillation amplitude |

|                                             |               | 00:1V                          |

|                                             |               | 01:2V                          |

|                                             |               | 10:4V                          |

|                                             |               | 11:Reserved                    |

| 2:0                                         | Response Time | 000: Reserved                  |

|                                             |               | 001: Reserved                  |

|                                             |               | 010: 192                       |

|                                             |               | 011: 384                       |

|                                             |               | 100: 768                       |

|                                             |               | 101: 1536                      |

|                                             |               | 110: 3072                      |

|                                             |               | 111: 6144                      |

# Table 9. Comparator Threshold High MSB

| Address = 0x07, Default=0xFF, Direction=R/W |                |                          |

|---------------------------------------------|----------------|--------------------------|

| Bit Field                                   | Field Name     | Description              |

| 7:0                                         | Threshold High | Threshold High Register. |

# Table 10. Comparator Threshold Low MSB

| Address = 0x09, Default=0x00, Direction=R/W |               |                         |

|---------------------------------------------|---------------|-------------------------|

| Bit Field                                   | Field Name    | Description             |

| 7:0                                         | Threshold Low | Threshold Low Register. |

## **Table 11. INTB Terminal Configuration**

| Address = 0x0A, Default=0x00, Direction=R/W |            |                                                              |

|---------------------------------------------|------------|--------------------------------------------------------------|

| Bit Field                                   | Field Name | Description                                                  |

| 7:3                                         | Reserved   | Reserved to 0                                                |

| 2:0                                         | Mode       | 000: All modes disabled                                      |

|                                             |            | 001: Wake-up Enabled on INTB terminal                        |

|                                             |            | 010: INTB terminal indicates the status of Comparator output |

|                                             |            | 100: DRDYB Enabled on INTB terminal                          |

|                                             |            | All other combinations are Reserved                          |

## **Table 12. Power Configuration**

|           | Address = 0x0B, Default=0x00, Direction=R/W |                                                                                             |  |

|-----------|---------------------------------------------|---------------------------------------------------------------------------------------------|--|

| Bit Field | Field Name                                  | Description                                                                                 |  |

| 7:1       | Reserved                                    | Reserved to 0                                                                               |  |

| 0         |                                             | 0:Stand-By mode 1:Active Mode. Conversion is Enabled Refer to Power Modes for more details. |  |

## Table 13. Status

| Address = 0x20, Default=NA, Direction=RO |             |                                                                        |

|------------------------------------------|-------------|------------------------------------------------------------------------|

| Bit Field                                | Field Name  | Description                                                            |

| 7                                        | OSC status  | 1:Indicates oscillator overloaded and stopped                          |

|                                          |             | 0:Oscillator working                                                   |

| 6                                        | Data Ready  | 1:No new data available                                                |

|                                          |             | 0:Data is ready to be read                                             |

| 5                                        | Wake-up     | 1:Wake-up disabled                                                     |

|                                          |             | 0:Wake-up triggered. Proximity data is more than Threshold High value. |

| 4                                        | Comparator  | 1:Proximity data is less than Threshold Low value                      |

|                                          |             | 0:Proximity data is more than Threshold High value                     |

| 3:0                                      | Do not Care |                                                                        |

## **Table 14. Proximity Data**

| Address = 0x22, Default=NA, Direction=RO |                |                |

|------------------------------------------|----------------|----------------|

| Bit Field                                | Field Name     | Description    |

| 7:0                                      | Proximity data | Proximity data |

Conversion data is updated to the proximity register only when a read is initiated on 0x22 register. If the read is delayed between subsequent conversions, these registers are not updated until another read is initiated on 0x22.

# TEXAS INSTRUMENTS

## 8 Applications and Implementation

#### 8.1 Application Information

#### 8.1.1 Calculation of Rp\_MIN and Rp\_MAX

Different sensing applications may have a different range of the resonance impedance Rp to measure. The LDC1051 measurement range of Rp is controlled by setting 2 registers – Rp\_MIN and Rp\_MAX. For a given application, Rp must never be outside the range set by these register values, otherwise the measured value will be clipped. For optimal sensor resolution, the range of Rp\_MIN to Rp\_MAX should not be unnecessarily large. The following procedure is recommended to determine the Rp\_MIN and Rp\_MAX register values.

## 8.1.1.1 Setting Rp\_MAX

Rp\_MAX sets the upper limit of the LDC1051 resonant impedance input range.

- Configure the sensor such that the eddy current losses are minimized. As an example, for a proximity sensing

application, set the distance between the sensor and the target to the maximum sensing distance.

- Measure the resonant impedance Rp using an impedance analyzer.

- Multiply Rp by 2 and use the next higher value from Table 4.

Note that setting Rp\_MAX to a value not listed in Table 4 can result in indeterminate behavior.

## 8.1.1.2 Setting Rp MIN

Rp\_MIN sets the lower limit of the LDC1051 resonant impedance input range.

- Configure the sensor such that the eddy current losses are maximized. As an example, for a proximity sensing application, set the distance between the sensor and the metal target to the minimum sensing distance.

- Measure the resonant impedance Rp using an impedance analyzer.

- Divide the Rp value by 2 and then select the next lower Rp value from Table 6.

Note that setting Rp\_MIN to a value not listed on Table 6 can result in indeterminate behavior. In addition, Rp\_MIN powers on with a default value of 0x14 which must be set to a value from Table 6 prior to powering on the LDC.

#### 8.1.2 Output Data Rate

Output data rate of LDC1051 depends on the sensor frequency, f<sub>sensor</sub> and 'Response Time' field in LDC Configuration register(Address:0x04).

Output Data Rate =

$$\frac{f_{sensor}}{\left(\frac{Response time}{3}\right)}$$

(4)

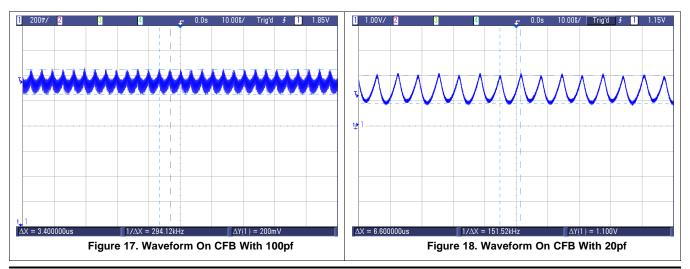

## 8.1.3 Choosing Filter Capacitor (CFA and CFB Terminals)

The Filter capacitor is critical to the operation of the LDC1051. The capacitor should be low leakage, temperature stable, and it must not generate any piezoelectric noise (the dielectrics of many capacitors exhibit piezoelectric characteristics and any such noise is coupled directly through Rp into the converter). The optimal capacitance values range from 20pF to 100nF. The value of the capacitor is based on the time constant and resonating frequency of the LC tank.

If a ceramic capacitor is used, then a C0G (or NP0) grade dielectric is recommended; the voltage rating should be ≥10V. The traces connecting CFA and CFB to the capacitor should be as short as possible to minimize any parasitics.

For optimal performance, the chosen filter capacitor, connected between terminals CFA and CFB, needs to be as small as possible, but large enough such that the active filter does not saturate. The size of this capacitor depends on the time constant of the sense coil, which is given by L/Rs, (L=inductance, Rs=series resistance of the inductor at oscillation frequency). The larger this time constant, the larger filter capacitor is required. Hence, this time constant reaches its maximum when there is no target present in front of the sensing coil.

## **Application Information (continued)**

The following procedure can be used to find the optimal filter capacitance:

- 1. Start with a large filter capacitor. For a ferrite core coil, 10nF is usually large enough. For an air coil or PCB coil, 100pF is usually large enough.

- 2. Power on the LDC and set the desired register values. Minimize the eddy currents losses. This is done by minimizing the amount of conductive target covering the sensor. For an axial sensing application, the target should be at farthest distance from coil. For a lateral or angular position sensing application, the target coverage of the coil should be minimized.

- 3. Observe the signal on the CFB terminal using a scope. Since this node is very sensitive to capacitive loading, it is recommended to use an active probe. As an alternative, a passive probe with a  $1k\Omega$  series resistance between the tip and the CFB terminal can be used.

- 4. Vary the values of the filter capacitor until that the signal observed on the CFB terminal has an amplitude of approximate 1V peak-to-peak. This signal scales linearly with the reciprocal of the filter capacitance. For example, if a 100pF filter capacitor is applied and the signal observed on the CFB terminal has a peak-to-peak value of 200mV, the desired 1V peak-to-peak value is obtained using a 200mV / 1V \* 100pF = 20pF filter capacitor.

## 8.2 Typical Applications

## 8.2.1 Axial Distance Sensing Using a PCB Sensor with LDC1051

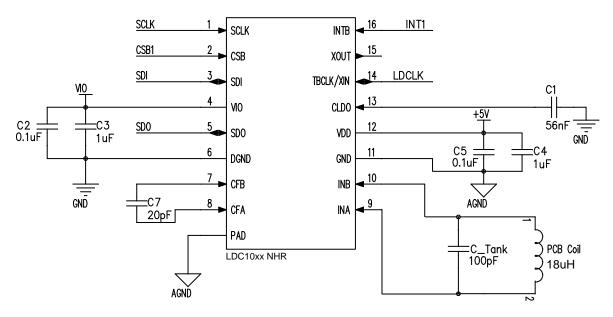

Figure 16. Typical Application Schematic, LDC10xx

#### 8.2.1.1 Design Requirements

For this design example, use the following as the input parameters.

**Table 15. Design Parameters**

| DESIGN PARAMETER                | EXAMPLE VALUE                               |  |  |  |  |

|---------------------------------|---------------------------------------------|--|--|--|--|

| Minimum sensing distance        | 1 mm                                        |  |  |  |  |

| Maximum sensing distance        | 8 mm                                        |  |  |  |  |

| Output data rate                | 78 KSPS (Max data rate with LDC10xx series) |  |  |  |  |

| Number of PCB layers for sensor | 2 layers                                    |  |  |  |  |

# TEXAS INSTRUMENTS

## 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Sensor and Target

In this example, consider a sensor with the below characteristics.

**Table 16. Sensor Characteristics**

| PARAMETER           | VALUE    |

|---------------------|----------|

| Layers              | 2        |

| Thickness of copper | 1 Oz     |

| Coil shape          | Circular |

| Number of turns     | 23       |

| Trace thickness     | 4 mil    |

| Trace spacing       | 4 mil    |

| PCB core material   | FR4      |

| Rp @ 1 mm           | 5 kΩ     |

| Rp @ 8 mm           | 12.5 kΩ  |

| Nominal Inductance  | 18 µH    |

Target material used is stainless steel

#### 8.2.1.2.2 Calculating Sensor Capacitor

Sensor frequency depends on various factors in the application. In this example since one of the design parameter is to achieve output data rate of 78 KSPS, sensor frequency can be calculated as below.

Output Data Rate =

$$\frac{f_{sensor}}{\left(\frac{Response time}{3}\right)}$$

(5)

With the lowest Response time of 192 and output data rate of 78 KSPS, sensor frequency calculated using the above formula is 4.99 MHz.

Now, using the below formula sensor capacitor is calculated to be 55 pF with a sensor inductance of 18 µH

$$L = \frac{1}{C \times (2\pi \times f_{sensor})^2}$$

(6)

### 8.2.1.2.3 Choosing Filter Capacitor

Using the steps given in Choosing Filter Capacitor (CFA and CFB Terminals) filter capacitor for the example sensor is 20 pF. Below waveform shows the pattern on CFB terminal with 100 pF and 20 pF filter capacitor.

## 8.2.1.2.4 Setting Rp\_MIN and Rp\_MAX

Calculating value for Rp\_MAX Register : Rp at 8mm is  $12.5k\Omega$ , 12500x2 = 25000. In Table 4, then  $27.704 k\Omega$  is the nearest value larger than  $25k\Omega$ ; this corresponds to Rp\_MAX value of 0x12

Calculating value for Rp\_MIN Register : Rp at 1mm is  $5k\Omega$ , 5000/2 = 2500. In Table 6,  $2.394k\Omega$  is the nearest value lower than  $2.5k\Omega$ ; this corresponds to Rp\_MIN value of 0x3B

#### 8.2.1.2.5 Calculating Minimum Sensor Frequency

Using,

$$N = 68.94 \times \log_{10} \left( \frac{F}{2500} \right) \tag{7}$$

N is 227.51, round off to 228 decimal. This value has to be written into Watchdog Timer Register, which is used to wake up the internal circuit when the sensor is saturated.

## 8.2.1.3 Application Curves

Figure 19. Rp vs Distance

# TEXAS INSTRUMENTS

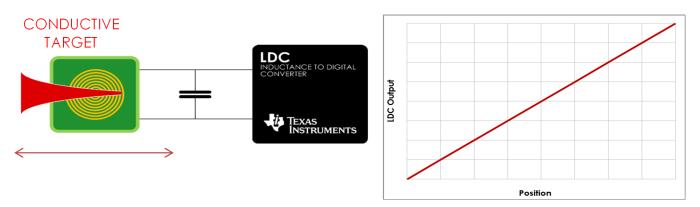

## 8.2.2 Lateral Position Sensing Application Diagram

Figure 20. Linear Position Sensing

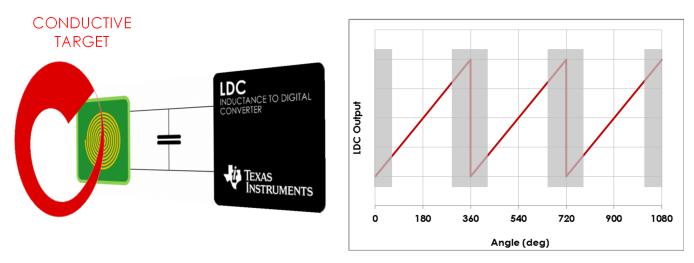

## 8.2.3 Angular Position Sensing Application Diagram

Figure 21. Angular Position Sensing

## 9 Power Supply Recommendations

The LDC1051 is designed to operate from an analog supply range of 4.75 V to 5.25 V and digital I/O supply range of 1.8V to 5.25V. The analog supply voltage should be greater than or equal to the digital supply voltage for proper operation of the device. The supply voltage should be well regulated. If the supply is located more than a few inches from the LDC1051 additional bulk capacitance may be required in addition to the ceramic bypass capacitors. An electrolytic capacitor with a value of 10uF is a typical choice.

## 10 Layout

## 10.1 Layout Guidelines

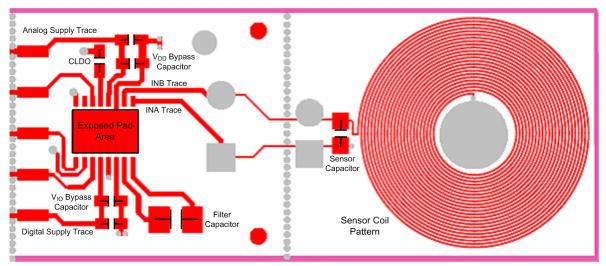

- The VDD and VIO terminal should be bypassed to ground with a low ESR ceramic bypass capacitor. The

typical recommended bypass capacitance is 0.1uF ceramic with a X5R or X7R dielectric.

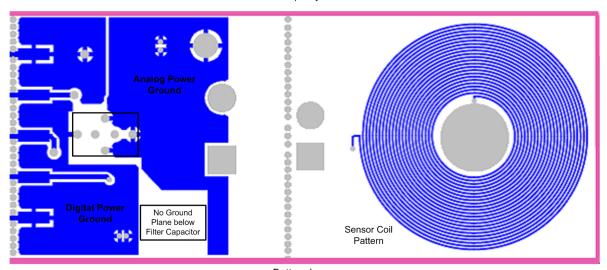

- The optimum placement is closest to the VDD/VIO and GND/DGND terminals of the device. Care should be taken to minimize the loop area formed by the bypass capacitor connection, the VDD/VIO terminal, and the GND/DGND terminal of the IC. See Figure 22 for a PCB layout example.

- The CLDO terminal should be bypassed to digital ground (DGND) with a 56nF ceramic bypass capacitor.

- The filter capacitor selected for the application using the procedure described in section Choosing Filter

Capacitor (CFA and CFB Terminals) is connected between CFA and CFB terminals. Place the filter capacitor

close to the CFA and CFB terminals. Do not use any ground/power plane below the capacitor and the trace

connecting the capacitor and the CFA /CFB terminals.

- Use of two separate ground plane for GND and DGND is recommended with a start connection. See Figure 22 for a PCB layout example.

# TEXAS INSTRUMENTS

## 10.2 Layout Example

Top Layer

**Bottom Layer**

Figure 22. LDC10xx Board Layout

Submit Documentation Feedback

# 11 Device and Documentation Support

## 11.1 Trademarks

All trademarks are the property of their respective owners.

## 11.2 Electrostatic Discharge Caution

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

6-Feb-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| LDC1051NHRJ      | ACTIVE | WSON         | NHR     | 16   | 4500    | Green (RoHS<br>& no Sb/Br) | SN               | Level-1-260C-UNLIM | -40 to 125   | LDC1051        | Samples |

| LDC1051NHRR      | ACTIVE | WSON         | NHR     | 16   | 1000    | Green (RoHS<br>& no Sb/Br) | SN               | Level-1-260C-UNLIM | -40 to 125   | LDC1051        | Samples |

| LDC1051NHRT      | ACTIVE | WSON         | NHR     | 16   | 250     | Green (RoHS<br>& no Sb/Br) | SN               | Level-1-260C-UNLIM | -40 to 125   | LDC1051        | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

6-Feb-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 7-Aug-2016

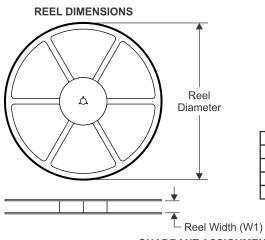

## TAPE AND REEL INFORMATION

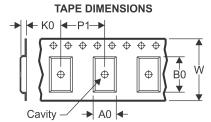

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

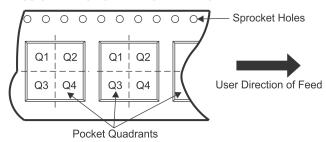

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All difficultions are norminal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|--------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LDC1051NHRJ                    | WSON            | NHR                | 16 | 4500 | 330.0                    | 12.4                     | 4.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LDC1051NHRR                    | WSON            | NHR                | 16 | 1000 | 178.0                    | 12.4                     | 4.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LDC1051NHRT                    | WSON            | NHR                | 16 | 250  | 178.0                    | 12.4                     | 4.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com 7-Aug-2016

\*All dimensions are nominal

| ı |             |              |                 |      |      |             |            |             |  |

|---|-------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

|   | Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|   | LDC1051NHRJ | WSON         | NHR             | 16   | 4500 | 367.0       | 367.0      | 35.0        |  |

|   | LDC1051NHRR | WSON         | NHR             | 16   | 1000 | 210.0       | 185.0      | 35.0        |  |

|   | LDC1051NHRT | WSON         | NHR             | 16   | 250  | 210.0       | 185.0      | 35.0        |  |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated