# Am9044/AM90L44

4096x1 Static RAM

#### DISTINCTIVE CHARACTERISTICS

- Low operating and standby power

- · Access times down to 200 ns

- Am9044 is a direct plug-in replacement for 4044

- High output drive -- 4.0 mA sink current @ 0.4 V

- TTL identical interface logic levels

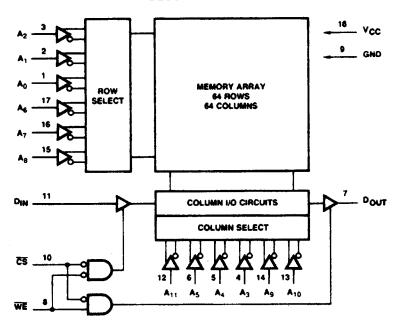

#### **GENERAL DESCRIPTION**

The Am9044/Am90L44 Series are high-performance, static, N-Channel, read/write, random-access memories organized as 4096 x 1. Operation is from a single 5 V supply, and all input/output levels are identical to standard TTL specifications. A Low-power version is available with power savings of about 30%.

Data readout is not destructive and the same polarity as data input. CS provides for easy selection of an individual package when the outputs are OR-tied. The outputs of 4.0 mA Am9044 provide increased short-circuit current for improved drive.

#### **BLOCK DIAGRAM**

BD000091

## PRODUCT SELECTOR GUIDE

| Part Number<br>Speed Indicator |          |           | Am9044/Am90L44 |     |     |    |  |  |  |  |

|--------------------------------|----------|-----------|----------------|-----|-----|----|--|--|--|--|

|                                |          |           | В              | , C | D   | E  |  |  |  |  |

| Maximum<br>Access Time (ns)    |          | 450       | 300            | 250 | 200 |    |  |  |  |  |

| 0 to +70°C                     | loc (mA) | Standard  | 70             | 70  | 70  | 70 |  |  |  |  |

|                                |          | Low-Power | 50             | 50  | 70  |    |  |  |  |  |

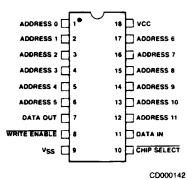

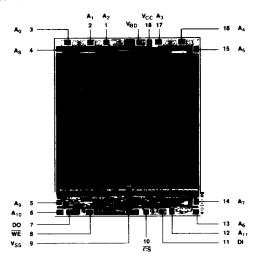

# CONNECTION DIAGRAM Top View DIPs

Note: Pin 1 is marked for orientation.

# METALLIZATION AND PAD LAYOUT

| Address Designators |                 |  |  |  |  |  |

|---------------------|-----------------|--|--|--|--|--|

| External            | Internal        |  |  |  |  |  |

| Ao                  | A <sub>2</sub>  |  |  |  |  |  |

| A <sub>1</sub>      | A <sub>1</sub>  |  |  |  |  |  |

| A <sub>2</sub>      | Ao              |  |  |  |  |  |

| Aз                  | A <sub>8</sub>  |  |  |  |  |  |

| A4                  | A <sub>9</sub>  |  |  |  |  |  |

| A <sub>5</sub>      | A <sub>10</sub> |  |  |  |  |  |

| A <sub>6</sub>      | A <sub>3</sub>  |  |  |  |  |  |

| A <sub>7</sub>      | A4              |  |  |  |  |  |

| A <sub>8</sub>      | A <sub>5</sub>  |  |  |  |  |  |

| Ag                  | A <sub>7</sub>  |  |  |  |  |  |

| A <sub>10</sub>     | A <sub>6</sub>  |  |  |  |  |  |

| A <sub>11</sub>     | A <sub>11</sub> |  |  |  |  |  |

Die Size 0.137" x 0.167"

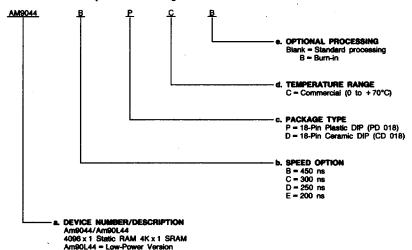

#### ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- e. Temperature Range

- e. Optional Processing

| Valid Combinations |          |  |  |  |  |

|--------------------|----------|--|--|--|--|

| AM9044B            |          |  |  |  |  |

| AM90L44B           |          |  |  |  |  |

| AM9044C            |          |  |  |  |  |

| AM90L44C           | PC, PCB, |  |  |  |  |

| AM9044D            | DC, DCB  |  |  |  |  |

| AM90L44D           |          |  |  |  |  |

| AM9044E            | 7        |  |  |  |  |

| AM90L44E           |          |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

## A<sub>0</sub>-A<sub>11</sub> Address Inputs (Inputs)

The address input lines select the memory location from which to read or write.

#### CS Chip Select (Input, Active LOW)

The CS line selects the memory device for active operation.

#### WE Write Enable (Input, Active LOW)

When both CS and WE are LOW, data on the input lines is written to the location presented on the address input lines.

#### D<sub>IN</sub> Data In (Input)

This pin is used to enter data during write operations.

## DOUT Data Out (Output, Three-State)

The content of the selected memory location is presented on the Data Output line during read operations (CS LOW, WE HIGH). The line goes three-state during write operations.

V<sub>CC</sub> Power Supply

Vss Ground

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Storage Temperature      | 65 to +150°C    |

|--------------------------|-----------------|

| Ambient Temperature with |                 |

| Power Applied            | 0 to 70°C       |

| Supply Voltage           | 0.5 V to +7.0 V |

| All Signal Voltage with  |                 |

| Respect to Ground        | 0.5 V to +7.0 V |

| Power Dissipation        | 1.0 W           |

|                          | 10 mA           |

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages.

#### **OPERATING RANGES** (Note 2)

| Commercial (C) Devices |                              |

|------------------------|------------------------------|

| Ambient Temperature    | (T <sub>A</sub> ) 0 to +70°C |

| Supply Voltage (Vcc)   | +4.5 V to +5.5 V             |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified (Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description                                           | 7                                                             | Min.                                          | Max.             | Unit |     |    |

|---------------------|--------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|------------------|------|-----|----|

| ЮН                  | Output HIGH Current                                                | V <sub>OH</sub> = 2.4 V<br>V <sub>CC</sub> = 4.5 V            | T <sub>A</sub> = 70°C                         |                  | -1.0 |     | mA |

| loL                 | Output LOW Current                                                 | VOL = 0.4 V                                                   | V <sub>OL</sub> = 0.4 V T <sub>A</sub> = 70°C |                  | 4.0  |     | mA |

| VIH                 | Input HIGH Voltage                                                 |                                                               |                                               |                  | 2.0  | Vcc | ٧  |

| VIL                 | Input LOW Voltage                                                  |                                                               |                                               |                  |      | 0.8 | ٧  |

| lix                 | Input Load Current                                                 | VSS < VIN < VCC                                               |                                               |                  |      | 10  | μΑ |

| loz                 | Output Leakage Current                                             | 0.4 V ≤ V <sub>O</sub> ≤ V <sub>CC</sub> ,<br>Output Disabled | T <sub>A</sub> = + 70°C                       | -50              | 50   | μΑ  |    |

|                     |                                                                    | Vcc = Max.                                                    | 1                                             | Standard Devices |      | 70  | mA |

| loc                 | Operating Supply Current                                           | V <sub>CC</sub> = Max.<br>CS ≤ V <sub>IL</sub>                | VCC - MAX.  CS ≤ VIL  TA = 0°C                |                  |      | 50  | шА |

| Ci                  | Input Capacitance (Note 6)                                         | Test Frequency = 1.0 MHz                                      |                                               |                  |      | 7.0 | ρF |

| Co                  | Output Capacitance (Note 6) T <sub>A</sub> = 25°C, All pins at 0 V |                                                               |                                               |                  |      | 7.0 |    |

# Notes: 1. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- 2. For test and correlation purposes, ambient temperature is defined as the "instant-on" case temperature.

- 3. Test conditions assume signal transition time of 10 ns or less, timing reference levels of 1.5 V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> plus 100 pF or 5 pF for T<sub>CX</sub>, T<sub>OTD</sub>, T<sub>OTW</sub> and T<sub>WO</sub>.

- 4. The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write.

- 5. The specified address access time will be valid only when CS is LOW soon enough for too elapse.

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

- 7. Transition is measured from 1.5 V on the input to (VOH 500 mV) and (VOL + 500 mV) on the output using CL = 5 pF.

**SWITCHING CHARACTERISTICS** over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted) (Notes 3-6)

|     | _                   |                                                              | B Devices |      | C Devices |      | D Devices |      | E Devices |          |          |

|-----|---------------------|--------------------------------------------------------------|-----------|------|-----------|------|-----------|------|-----------|----------|----------|

| No. | Parameter<br>Symbol | Parameter<br>Description                                     |           | Max. | Min.      | Max. | Min.      | Max. | Min.      | Max.     | Unit     |

| R   | EAD CYCLE           |                                                              |           |      |           |      |           |      |           |          |          |

| 1   | <sup>t</sup> RC     | Address Valid to Address Do Not Care Time (Read Cycle Time)  | 450       |      | 300       |      | 250       |      | 200       |          |          |

| 2   | t <sub>A</sub>      | Address Valid to Data Out Valid Delay (Address Access Time)  |           | 450  |           | 300  |           | 250  |           | 200      |          |

| 3   | \$co                | Chip Select LOW to Data Out Valid (Note 5)                   |           | 100  |           | 100  |           | 70   |           | 70       |          |

| 4   | tcx                 | Chip Select LOW to Data Out On (Note 6, 7)                   | 10        |      | 10        |      | 10        |      | 10        |          |          |

| 5   | totd                | Chip Select HIGH to Data Out Off (Note 6, 7)                 |           | 100  |           | 80   |           | 60   |           | 60       |          |

| 6   | <sup>t</sup> OHA    | Output hold time after address change                        | 20        |      | 20        |      | 20        |      | 20        | <u> </u> | <u> </u> |

| W   | RITE CYCLE          |                                                              |           |      | _         |      |           |      |           |          |          |

| 7   | twc                 | Address Valid to Address Do Not Care Time (Write Cycle Time) | 450       |      | 300       |      | 250       |      | 200       |          |          |

| 8   | tw                  | Write Enable LOW to Write<br>Enable HIGH Time (Note 4)       | 200       |      | 150       |      | 100       |      | 100       |          |          |

| 9   | twn                 | Write Enable HIGH to Address Do Not Care<br>Time             | 0         |      | 0         |      | 0         |      | 0         |          |          |

| 10  | totw                | Write Enable LOW to Data Out Off Delay (Note 6, 7)           |           | 100  |           | 80   |           | 60   |           | 60       |          |

| 11  | tow                 | Data In Valid to Write Enable HIGH Time                      | 200       |      | 150       |      | 100       |      | 100       |          |          |

| 12  | tон                 | Write Enable HIGH to Data In Do Not Care<br>Time             | 0         |      | 0         |      | 0         |      | 0         |          | ns       |

| 13  | taw                 | Address Valid to Write Enable LOW Time                       | 0         |      | 0         |      | 0         |      | 0         |          |          |

| 14  | tcw                 | Chip Select LOW to Write<br>Enable HIGH Time (Note 4)        | 200       |      | 150       |      | 100       |      | 100       |          |          |

| 15  | two                 | Write Enable HIGH To Output Turn On (Note 6, 7)              | 0         | 100  | 0         | 100  | 0         | 70   | 0         | 70       |          |

Notes: See notes following DC Characteristics table.

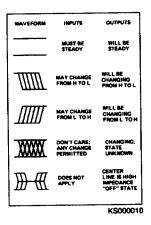

# SWITCHING WAVEFORMS

# KEY TO SWITCHING WAVEFORMS

ADORESS

ACCESS

AC

Notes: See notes following DC Characteristics table.

# 4

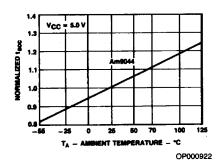

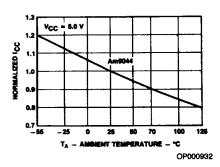

#### TYPICAL PERFORMANCE CURVES

#### Normalized Supily Current Versus Supply Voltage

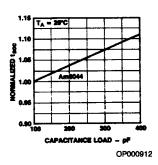

Normalized Access Time Versus

Output Loading

Normalized Access Time Versus Ambient Temperature

Normalized Supply Current Versus Ambient Temperature