#### **MAX31331**

### **General Description**

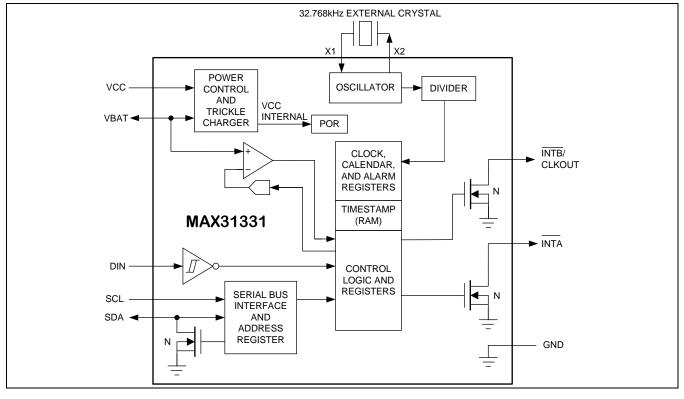

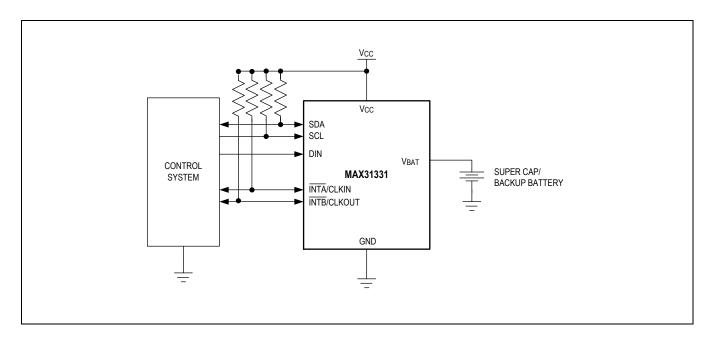

The MAX31331 ultra-low power, real-time clock (RTC) is a time-keeping device that consumes nominal 65nA timekeeping current, extending battery life. The MAX31331 supports a wide range of 32.768kHz crystals. A crystal with any capacitive loading (CL) spec can be used, which broadens the pool of usable crystals for this device. This device is accessed through an I<sup>2</sup>C serial interface.

The device also features a backup supply pin (VBAT) and automatically switches over to the backup supply (VBAT) when the main supply (VCC) drops below the programmed threshold voltage and the backup supply (VBAT) voltage.

Other features include two time-of-day alarms, interrupt outputs, programmable square-wave output, event detection input with timestamping, and a serial bus timeout mechanism. The 32-byte timestamp registers double as RAM storage. The device features a digital Schmitt trigger input (DIN) which can be used to record timestamps and/or generate an interrupt on the falling/rising edge of the DIN signal. The clock/calendar provides seconds, minutes, hours, day, month, year, and date information. A 1/128 second register is available for a sub-second timestamp resolution. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in 24-hour/12-hour format.

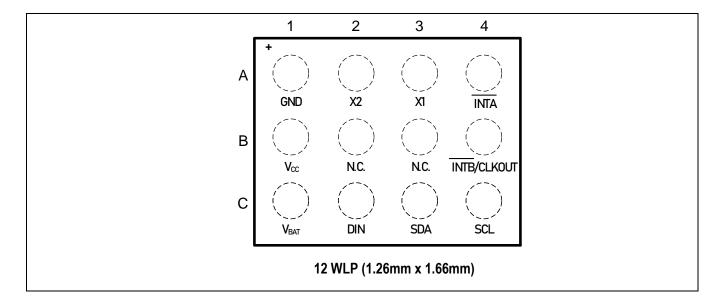

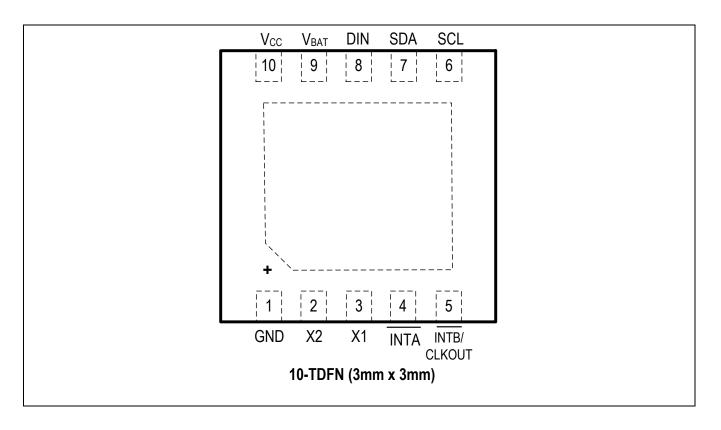

The MAX31331 is available in lead (Pb)-free/RoHS compliant, 12-bump, 1.66mm x 1.26mm WLP with 0.4mm pitch, as well as a 10-pin 3mm x 3mm TDFN package.

The device supports the -40°C to +85°C extended temperature range.

### **Applications**

- Medical

- Wearables

- Portable Instruments

- Telematics

- Industrial

- IOT

### **Benefits and Features**

- Ultra-Low-Power Extends Run Time

- 65nA Timekeeping Current

- 1.1V to 5.5V Timekeeping Voltage Range

- Automatic Switchover to Backup Supply on Power Fail Event

- Trickle Charger for External Supercapacitor or Rechargeable Battery

- Small Footprint and Low BOM

- 1.66mm x 1.26mm 12-bump WLP

- 3mm x 3mm 10-pin TDFN

- No External Load Capacitors Required

- Provides Flexibility

- Wide Range of External Crystals Supported (No External Loading Required)

- Frequency Correction with <0.5ppm Resolution</li>

- 1.62V to 5.5V Interface Voltage Range

- Value-added Features for Ease of Use

- Event Detection with Dedicated Pin

- Timestamps for Various Events

- Low Battery Voltage Detection

- 1/128 Second Register

- · Alarms and Countdown Timer

- 32-byte User RAM

Ordering Information appears at end of data sheet.

19-101203; Rev 1; 4/22

### **Simplified Block Diagram**

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

# **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to Ground0.3V to +6V |

|--------------------------------------------------------|

| Operating Temperature Range40°C to +85°C               |

| Junction Temperature+125°C                             |

| Storage Temperature Range      | 55°C to +125°C |

|--------------------------------|----------------|

| Soldering Temperature (Reflow) |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 12-WLP

| PACKAGE CODE                                           | W121P1+1                       |  |  |  |

|--------------------------------------------------------|--------------------------------|--|--|--|

| Outline Number                                         | <u>21-100554</u>               |  |  |  |

| Land Pattern Number                                    | Refer to Application Note 1891 |  |  |  |

| Four Layer Board:                                      |                                |  |  |  |

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})$ | 72.82°C/W                      |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$    | N/A                            |  |  |  |

#### 10-TDFN

| PACKAGE CODE                                             | T1033+1C       |  |  |

|----------------------------------------------------------|----------------|--|--|

| Outline Number                                           | <u>21-0137</u> |  |  |

| Land Pattern Number                                      | <u>90-0003</u> |  |  |

| Single Layer Board:                                      |                |  |  |

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 54°C/W         |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$      | 9°C/W          |  |  |

| Four Layer Board:                                        |                |  |  |

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 41°C/W         |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )    | 9°C/W          |  |  |

## **Electrical Characteristics**

(VCC = +1.1V to +5.5V,  $T_A$  = -40°C to +85°C unless otherwise noted. = Typical values at VCC = +3.0V,  $T_A$  = +25°C unless otherwise noted. Limits are 100% tested at  $T_A$  = +25°C.)

| PARAMETER                                                                     | SYMBOL                        | CO                                                                             | CONDITIONS MIN TYP M                 |                               |      |                               | UNITS |  |

|-------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------|--------------------------------------|-------------------------------|------|-------------------------------|-------|--|

| DC CHARACTERISTICS                                                            |                               |                                                                                |                                      |                               |      |                               |       |  |

| Timekeeping Supply<br>Voltage Range                                           | V <sub>CC</sub>               | ( <u>Note 3</u> )                                                              |                                      | 1.1                           |      | 5.5                           | V     |  |

| Interface Supply<br>Voltage Range                                             | V <sub>ccio</sub>             | Full Operation                                                                 |                                      | 1.62                          |      | 5.5                           | V     |  |

| Minimum Initial<br>Power-On Voltage                                           | $V_{\text{CC}(\text{POR})}$   |                                                                                |                                      |                               | 1.7  |                               | V     |  |

|                                                                               |                               |                                                                                | Vcc = +1.1V                          |                               | 65   | 650                           |       |  |

| Timekeeping Current                                                           | I <sub>CCT</sub>              | ( <u>Note 4</u> )                                                              | $V_{CC} = +3.0V$                     |                               | 65   | 650                           | nA    |  |

|                                                                               |                               |                                                                                | $V_{CC} = +5.5V$                     |                               | 70   | 700                           |       |  |

| Maximum Supply<br>Power-Up Slew Rate                                          | T <sub>VCCR</sub>             |                                                                                |                                      |                               | 5    |                               | V/ms  |  |

| Maximum Supply<br>Switchover Slew Rate                                        | $T_{VCCF}$                    |                                                                                |                                      |                               | 0.5  |                               | V/ms  |  |

| BATTERY BACKUP AND                                                            | THRESHOLD                     |                                                                                |                                      | 1                             |      |                               |       |  |

| Timekeeping Backup<br>Voltage Range                                           | $V_{\text{BAT}}$              |                                                                                |                                      | 1.1                           |      | 5.5                           | V     |  |

| Power Fail Threshold                                                          |                               | PFVT = 0                                                                       |                                      | 1.55                          |      | v                             |       |  |

| Voltage                                                                       | $V_{PF}$                      | PFVT = 1                                                                       | 2                                    |                               |      | v                             |       |  |

|                                                                               | IBATT                         |                                                                                | $V_{BAT} = +1.1V$                    |                               | 65   | 650                           |       |  |

| Timekeeping Battery<br>Current                                                |                               | ( <u>Note 4</u> )                                                              | $V_{BAT} = +3.0V$                    |                               | 65   | 650                           | nA    |  |

| ounon                                                                         |                               |                                                                                | $V_{BAT} = +5.5V$                    |                               | 70   | 700                           |       |  |

| Trickle-Charge                                                                | R1                            |                                                                                |                                      |                               | 3.3  |                               |       |  |

| Current-Limiting                                                              | R2                            |                                                                                |                                      |                               | 6.4  |                               | kΩ    |  |

| Resistance                                                                    | R3                            |                                                                                |                                      |                               | 11.3 |                               |       |  |

| Minimum Battery<br>Voltage for $V_{CC}$ to<br>$V_{BAT}$ Switch (Auto<br>Mode) | V <sub>BAT_SW</sub>           | V <sub>CC</sub> < V <sub>PF</sub> and<br>V <sub>CC</sub> < V <sub>BAT_SW</sub> |                                      |                               | 1.5  |                               | V     |  |

| SCHMITT TRIGGER INPL                                                          | JT (DIN)                      |                                                                                |                                      |                               |      |                               |       |  |

| Logic 1 Input                                                                 | V                             | ( <u>Note 14</u> )                                                             | V <sub>CC_INT</sub> = 1.8 to<br>5.5V | 0.7 x<br>V <sub>CC_INT</sub>  |      | V <sub>CC_INT</sub><br>+ 0.3  | v     |  |

| Logic i iriput                                                                | V <sub>IH</sub> ( <u>Note</u> | ( <u>19018-14</u> )                                                            | V <sub>CC_INT</sub> = 1.62V          | 0.75 x<br>V <sub>CC_INT</sub> |      | V <sub>CC_INT</sub><br>+ 0.3  | v     |  |

| Logic Olpout                                                                  | out V <sub>IL</sub>           | (Noto 14)                                                                      | V <sub>CC_INT</sub> = 1.8 to<br>5.5V | -0.3                          |      | 0.3 x<br>V <sub>CC_INT</sub>  |       |  |

| Logic 0 Input                                                                 |                               | ( <u>Note 14</u> )                                                             | $V_{CC_{INT}} = 1.62V$               | -0.3                          |      | 0.25 x<br>V <sub>CC_INT</sub> | V     |  |

| Input Leakage                                                                 | ILI                           |                                                                                | •                                    | -0.1                          |      | +0.1                          | μA    |  |

| LOGIC INPUTS AND OUT                                                          | TPUTS                         | 1                                                                              |                                      | 1                             |      |                               | 1     |  |

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

| PARAMETER                                              | SYMBOL              | CONDITIONS                                       | MIN                       | TYP                       | MAX                           | UNITS |

|--------------------------------------------------------|---------------------|--------------------------------------------------|---------------------------|---------------------------|-------------------------------|-------|

| Logic 1 Input                                          | V <sub>IH</sub>     | VCC = 1.62V                                      | 0.75 x<br>V <sub>cc</sub> |                           | V <sub>CC</sub> + 0.3         | V     |

|                                                        |                     | VCC = 1.8V to 5.5V                               | 0.7 x V <sub>CC</sub>     |                           | V <sub>CC</sub> + 0.3         |       |

| Logic 0 Input                                          | V <sub>IL</sub>     | VCC = 1.62V                                      | -0.3                      |                           | 0.25 x<br>V <sub>CC</sub>     | V     |

|                                                        |                     | VCC = 1.8V to 5.5V                               | -0.3                      |                           | $0.3 \text{ x V}_{\text{CC}}$ |       |

| Input Leakage (SCL)                                    | IIL                 | V <sub>CC</sub> ≥ 1.62V                          | -0.1                      |                           | +0.1                          | μA    |

| Output Leakage<br>(SDA, INTA,<br>INTB/CLKOUT)          | lo                  | V <sub>CC</sub> ≥ 1.62V                          | -1                        |                           | +1                            | μΑ    |

| Output Logic 0 (SDA,<br>INTA, INTB,<br>CLKOUT)         | I <sub>OL</sub>     | V <sub>OL</sub> = +0.4V, V <sub>CC</sub> ≥ 1.62V | 2                         |                           |                               | mA    |

| AC CHARACTERISTICS                                     | (Vcc = +1.62V t     | o +5.5V)                                         | I.                        |                           |                               |       |

| SCL Clock Frequency                                    | f <sub>SCL</sub>    | ( <u>Note 5</u> )                                | 10                        |                           | 400                           | kHz   |

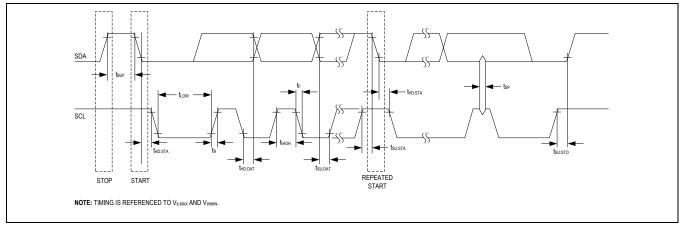

| Bus Free Time<br>Between a STOP and<br>START Condition | t <sub>BUF</sub>    |                                                  | 1.3                       |                           |                               | μs    |

| Hold Time<br>(Repeated) START<br>Condition             | thd:sta             | ( <u>Note 6</u> )                                | 0.6                       |                           |                               | μs    |

| Low Period of SCL<br>Clock                             | t <sub>LOW</sub>    |                                                  | 1.3                       |                           |                               | μs    |

| High Period of SCL<br>Clock                            | t <sub>HIGH</sub>   |                                                  | 0.6                       |                           |                               | μs    |

| Data Hold Time                                         | t <sub>HD:DAT</sub> | ( <u>Note 7, Note 8</u> )                        | 0                         |                           | 0.9                           | μs    |

| Data Setup Time                                        | t <sub>su:dat</sub> | Vcc = 3V ( <u>Note 9</u> )                       | 100                       |                           |                               | ns    |

| Setup Time for a<br>Repeated START<br>Condition        | t <sub>su:sta</sub> |                                                  | 0.6                       |                           |                               | μs    |

| Minimum Rise Time<br>of Both SDA and SCL<br>Signals    | t <sub>RMIN</sub>   | ( <u>Note 10</u> )                               |                           | 20 +<br>0.1С <sub>в</sub> |                               | ns    |

| Maximum Rise Time<br>of Both SDA and SCL<br>Signals    | t <sub>RMAX</sub>   |                                                  |                           | 300                       |                               | ns    |

| Minimum Fall Time<br>for Both SDA and<br>SCL Signals   | t <sub>FMIN</sub>   | ( <u>Note 10</u> )                               |                           | 20 +<br>0.1С <sub>в</sub> |                               | ns    |

| Maximum Fall Time<br>for Both SDA and<br>SCL Signals   | t <sub>FMAX</sub>   |                                                  |                           | 300                       |                               | ns    |

| Setup Time for STOP<br>Condition                       | t <sub>su:sto</sub> |                                                  | 0.6                       |                           |                               | μs    |

(VCC = +1.1V to +5.5V,  $T_A$  = -40°C to +85°C unless otherwise noted. = Typical values at VCC = +3.0V,  $T_A$  = +25°C unless otherwise noted. Limits are 100% tested at  $T_A$  = +25°C.)

### Ultra-Low-Power, I2C Real-Time Clock and Power Management

| $(VCC = +1.1V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +25^{\circ}C \text{ unless otherwise noted.} = Typical values at VCC = +3.0V, T_A = +3$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| noted. Limits are 100% tested at $T_A = +25$ °C.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PARAMETER                                       | SYMBOL               | CONDITIONS         | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|----------------------|--------------------|-----|-----|-----|-------|

| Maximum Capacitive<br>Load for Each Bus<br>Line | C <sub>B</sub>       | ( <u>Note 10</u> ) |     | 400 |     | pF    |

| I/O Capacitance                                 | Cı/o                 | ( <u>Note 11</u> ) |     | 10  |     | pF    |

| SCL Spike<br>Suppression                        | t <sub>SP</sub>      | ( <u>Note 11</u> ) |     | 110 |     | ns    |

| Oscillator Stop Flag<br>(OSF) Delay             |                      | ( <u>Note 12</u> ) |     | 0.5 | 2   | ms    |

| Timeout Interval                                | t <sub>TIMEOUT</sub> | ( <u>Note 13</u> ) | 25  |     | 35  | ms    |

Note 1: Limits at -40°C and +85°C are guaranteed by design and characterization; not production tested.

Note 2: Voltage referenced to ground.

- Note 3: Timekeeping function is active through this range. I<sup>2</sup>C and other I/O functions are not active below V<sub>CCIO(min)</sub>.

- **Note 4:** Specified with I<sup>2</sup>C bus inactive. Oscillator (timekeeping function) operational. (CLKOEN = 0).

- Note 5: The minimum SCL clock frequency is limited by the bus timeout feature, which resets the serial bus interface if SCL is held low for t<sub>TIMEOUT</sub>.

- **Note 6:** After this period, the first clock pulse is generated.

- **Note 7:** A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 8: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 9: A fast-mode device can be used in a standard-mode system, but the requirement t<sub>SU:DAT</sub> ≥ to 250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>RMAX</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns before the SCL line is released.

- Note 10: C<sub>B</sub> is the total capacitance of one bus line, including all connected devices, in pF.

- Note 11: Guaranteed by design; not 100% production tested.

- Note 12: The parameter t<sub>OSF</sub> is the period of time the oscillator must be stopped for the OSF flag to be set over V<sub>CC</sub> range.

- Note 13: The device I<sup>2</sup>C interface is in reset state and can receive a new START condition when SCL is held low for at least t<sub>TIMEOUTMAX</sub>. Once the device detects this condition, the SDA output is released. The oscillator must be running for this function to work.

- Note 14: V<sub>CC\_INT</sub> is the Active Internal supply. V<sub>CC\_INT</sub> = VBAT when VCC < VPF and VCC < VBAT in auto mode (*Table 1*).

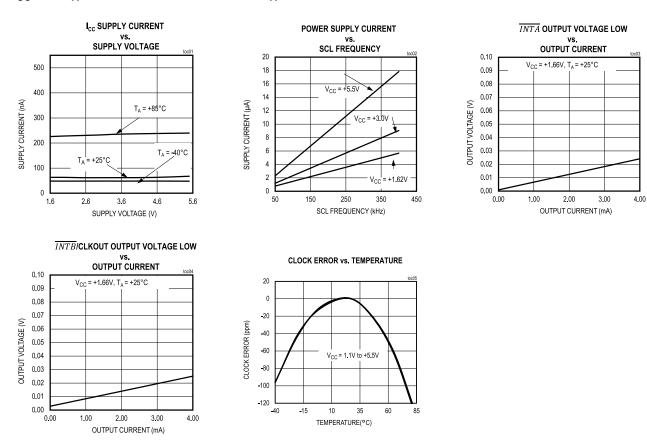

# **Typical Operating Characteristics**

$V_{CC} = 3V$ ;  $T_A = +25^{\circ}C$ , unless noted otherwise ( $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **Pin Configuration**

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

# **Pin Description**

| Р      | PIN  |                 | FUNCTION                                                                                                                                                                                                                                                                   |

|--------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLP    | TDFN | NAME            | FUNCTION                                                                                                                                                                                                                                                                   |

| A1     | 1    | GND             | Ground Connection                                                                                                                                                                                                                                                          |

| A2     | 2    | X2              | Second Crystal Input for an External 32.768kHz Crystal. See the <u>Oscillator Circuit and</u><br><u>Clock Accuracy</u> section for recommended external crystal parameters.                                                                                                |

| A3     | 3    | X1              | First Crystal Input for an External 32.768kHz Crystal. See the <u>Oscillator Circuit and Clock</u><br><u>Accuracy</u> section for recommended external crystal parameters.                                                                                                 |

| A4     | 4    | INTA            | Active-Low Interrupt Output. This pin is used to output an alarm interrupt. It is an open-<br>drain pin and requires an external pullup resistor. If not used, connect this pin to ground.<br>See <u>Table 2</u> .                                                         |

| B4     | 5    | INTB/CLK<br>OUT | Square-Wave Clock or Active-Low Interrupt Output. This pin is used to output a programmable square wave or an alarm interrupt signal. This is an open-drain output and requires an external pullup resistor. If not used, connect this pin to ground. See <u>Table 2</u> . |

| C4     | 6    | SCL             | Serial-Clock Input. SCL is used to synchronize data movement on the serial interface.                                                                                                                                                                                      |

| C3     | 7    | SDA             | Serial-Data Input/Output. SDA is the input/output pin for the I <sup>2</sup> C serial interface. The SDA pin is open-drain and requires an external pullup resistor.                                                                                                       |

| C2     | 8    | DIN             | Digital SCHMITT TRIGGER Input. Connect to ground if not used.                                                                                                                                                                                                              |

| C1     | 9    | VBAT            | Backup Battery Input and Trickle Charger Output. Connect to GND when backup battery is not used.                                                                                                                                                                           |

| B1     | 10   | VCC             | Supply Voltage                                                                                                                                                                                                                                                             |

| B2, B3 |      | N.C.            | Not Connected.                                                                                                                                                                                                                                                             |

## **Detailed Description**

### Clock/Calendar

The time and calendar information are obtained by reading the appropriate I<sup>2</sup>C registers. The time and calendar data are set or initialized by writing to the appropriate time/date registers. The contents of the time and calendar registers are in the binary-coded decimal (BCD) format. The century bit (bit 7 of the Month register) is toggled when the Years register overflows from 99 to 00. The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation. A write to any of clock/calendar registers updates the clock/calendar after a 3ms window.

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is guaranteed to operate when VCC is between 1.62V and 5.5V. The I<sup>2</sup>C interface is accessible whenever VCC is at a valid level. To prevent invalid device operation, the I<sup>2</sup>C interface should not be accessed when VCC is below +1.62V. The slave address is defined as the seven most significant bits (MSBs) sent by the master after a START condition. The address is 1101000 (or 0xD0, left justified with LSB set to 0). The eighth bit is used to define a write or read operation. If a microcontroller connected to the MAX31331 resets during I<sup>2</sup>C communication, it is possible that the microcontroller and the MAX31331 could become unsynchronized. In such scenarios, the timeout feature in MAX31331 can be used to reset the I<sup>2</sup>C slave controller if the SCL is held low for >t<sub>TIMEOUT</sub>. After a loss of communication, if the microcontroller initiates a new I<sup>2</sup>C transaction, the MAX31331's I<sup>2</sup>C state machine is reset.

Figure 1. I<sup>2</sup>C Timing Diagram

#### **Oscillator Circuit and Clock Accuracy**

The MAX31331 uses an external 32.768kHz crystal. The oscillator circuit does not require any external components to operate. This also enables the use of many 32.768kHz crystals regardless of the loading (CL) spec. Crystal with minimum Quality Factor of 9000 must be used for sustaining oscillations. After the oscillator is enabled, the startup time of the oscillator circuit is usually less than 1 second.

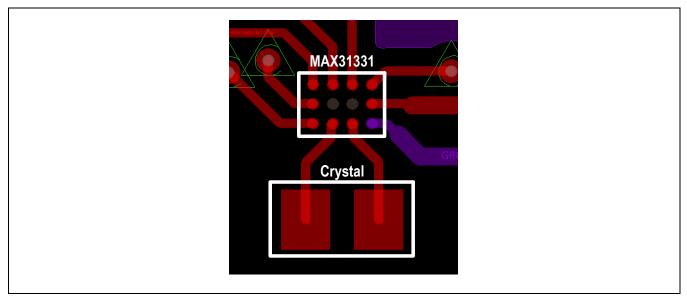

It is recommended to minimize the trace lengths from the crystal to the X1/X2 pins of MAX31331 and keep them away from any nearby ground plane to minimize the parasitic capacitance. Also, keep any other high-speed clock routings including signal from INTB/CLKO pin far away from these X1/X2 pins to reduce coupling effect which can degrade the oscillator signal integrity. <u>Figure 2</u> shows the recommended PCB layout for the crystal and oscillator.

Figure 2. PCB Layout Example

The accuracy of the MAX31331 depends on the parallel resonant frequency of the crystal used, which is typically above the nominal 32.768kHz. The device includes a fractional divider circuit that can correct the typical accuracy close to 0ppm. The MAX31331 is factory-trimmed to ensure a typical accuracy of ±20ppm with the NDK NX2012SA 6pF crystal, which is also used on the MAX31331SHLD evaluation board. As stated above, any other suitable crystal can be used instead. Due to the nature of the oscillator and the nature of quartz blanks inside different crystals, the accuracy observed with other crystals may be off by 10 to 100's of ppm. The MAX31331 provides an option to digitally correct the clock accuracy using the OFFSET\_HIGH (1Dh) and OFFSET\_LOW (1Eh) registers. These registers enable the user to measure and enter the absolute error. The digital logic then calculates the required compensation and corrects the accuracy with a resolution of 0.477ppm. Follow the steps to measure and correct the clock accuracy on your board.

- 1. Power on the MAX31331 and write 0x07 to the RTC\_CONFIG2 (04h) register to enable the uncorrected 32kHz output clock.

- 2. Measure the clock frequency on INTB/CLKO pin using a frequency counter and record it as MEAS.

- 3. Calculate uncorrected crystal accuracy in ppm as: ACC =  $\frac{(MEAS-32,768) \times 10^6}{32,768}$

- 4. Calculate the offset value as: OFFSET = int{ACC/0.477}.

- 5. Split the final 16-bit OFFSET value and enter the upper eight bits into the OFFSET\_HIGH register and the lower eight bits into the OFFSET\_LOW register.

- 6. The new offset correction starts taking effect after the OFFSET\_LOW byte is written.

The new offset correction remains valid as long as there is power source (VCC or VBAT) provided. The offset registers default to a factory-trimmed value at every POR event.

#### **Power Management**

The MAX31331 features a backup battery voltage pin (VBAT) in addition to the primary supply voltage pin (VCC). Initial power-up should always be performed on the VCC domain, and this rail is expected to be equal to or higher than VCC(POR) = 1.7V. This ensures a successful power-on-reset (POR) function. If the VCC rail stays below 1.7V (but above 1.62V) during the initial power-up, an external I<sup>2</sup>C master can communicate with the MAX31331, but successful operation is not guaranteed because POR was not achieved.

The MAX31331 has a power management function which monitors supply voltage on VCC and backup battery voltage on VBAT, and then determines which source to use as internal supply. There is a PFAIL interrupt flag status bit in the register map to indicate the power fail condition. The VBAT pin should be connected to the backup battery; if there is no backup battery, VBAT should be tied to ground.

Power management control bits PWR\_MGMT[1:0] (register 1Ah) are used as follows; for the Power Management Auto and Trickle Charger mode, a "power fail voltage" can be programmed to 1.55V (default) or 2V. MAX31331 switches from the backup battery to the internal power supply if and only if the main supply VCC is lower than both the power fail voltage and the backup battery voltage (and the backup battery voltage is higher than VBAT\_SW = 1.5V). Otherwise, VCC remains as the main supply. There is an PFAIL interrupt flag status bit in the STATUS (00h) register that can be used as a power fail flag. The PFAIL interrupt flag monitors the VCC supply and is set when VCC falls below the power fail threshold voltage.

| EN_TRICKLE | VBACK_SEL | MANUAL_SEL | MODE OF OPERATION                                                                      |               |  |

|------------|-----------|------------|----------------------------------------------------------------------------------------|---------------|--|

|            |           |            | Power Management Auto and Trickle Charger On                                           |               |  |

|            |           |            | Supply Condition                                                                       | Active Supply |  |

|            |           | 0          | VCC < VPF, VCC < VBAT                                                                  | VBAT          |  |

| 1          | x         | 0          | VCC < VPF, VCC > VBAT                                                                  | VCC           |  |

|            |           |            | VCC > VPF, VCC < VBAT                                                                  | VCC           |  |

|            |           |            | VCC > VPF, VCC > VBAT                                                                  | VCC           |  |

| 1          | 0         | 1          | Power Management Manual and Trickle Charger<br>Active Supply = VCC                     | On            |  |

| 1          | 1         | 1          | Power Management Manual and Trickle Charger On<br>Active Supply = VBAT for VBAT > VCC  |               |  |

|            |           |            | Power Management Auto and Trickle Charger Off                                          |               |  |

|            |           |            | Supply Condition                                                                       | Active Supply |  |

| <u> </u>   |           | 0          | VCC < VPF, VCC < VBAT                                                                  | VBAT          |  |

| 0          | х         | 0          | VCC < VPF, VCC > VBAT                                                                  | VCC           |  |

|            |           |            | VCC > VPF, VCC < VBAT                                                                  | VCC           |  |

|            |           |            | VCC > VPF, VCC > VBAT                                                                  | VCC           |  |

| 0          | 0         | 1          | 1 Power Management Manual and Trickle Charger Off<br>Active Supply = VCC               |               |  |

| 0          | 1         | 1          | Power Management Manual and Trickle Charger Off<br>Active Supply = VBAT for VBAT > VCC |               |  |

### Table 1. Power Management

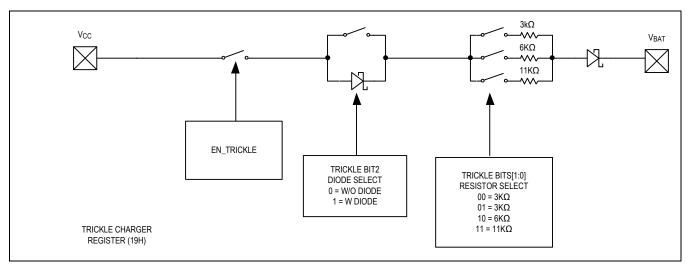

### **Trickle Charger**

The trickle charger is for charging an external super capacitor or a rechargeable battery. The maximum charging current can be calculated as follows:

IMAX = (VCC - VD - VBAT)/R

Where VD is the diode voltage drop, VBAT is the voltage of the battery being charged, and R is the resistance selected in the charging path. As the battery charges, the battery voltage increases and the voltage across the charging path decreases. Therefore, the charging current also decreases.

Figure 3. Trickle Charger

#### **Interrupt Status and Outputs**

When an interrupt is asserted, a corresponding status bit in STATUS (00h) register becomes "1", and an interrupt output transitions from High to Low. The interrupt status bit and output can be cleared by reading the STATUS (00h) register. See <u>Table 2</u> for interrupt configurations.

#### Table 2. Interrupt Modes

| ENCLKO | INTA                                                                       | CLKOUT/INTB  |

|--------|----------------------------------------------------------------------------|--------------|

| 0      | INTA: Alarm2, Timer, Power Fail<br>(PFAIL), Digital interrupt (DIN)        | INTB: Alarm1 |

| 1      | INTA: Alarm1, Alarm2 Timer, Power<br>Fail (PFAIL), Digital interrupt (DIN) | CLKOUT       |

#### Alarms

The MAX31331 contains two time-of-day/date alarms. Alarm 1 can be set by writing to registers 0Fh–14h. Alarm 2 can be set by writing to registers 15h–17h. The alarms can be programmed by the A1IE and A2IE bits in INT\_EN register to activate the INT output on an alarm match condition. Bit 7 of each of the time-of-day/date alarm registers and bit 6 of Alm1\_mon register are mask bits (*Table 2*). When all the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers match the corresponding values stored in the time-of-day, date, month, and year alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. *Table 3* and *Table 4* show the possible settings. Configurations not listed in the table result in illogical operation. The DY\_DT\_MATCH bit (bit 6 of the alarm day/date registers) controls whether the alarm value stored in bits 0–5 of that register represents the day of the week or the date of the month. If DY\_DT\_MATCH is written to logic 0, the alarm is the result of a match with date of the month. If DY\_DT\_MATCH is written to logic 1, the alarm is the result of a match with day of the week.

### Table 3. Alarm 1 Settings

| DY/DT | ALAI | RM 1 RE | GISTER | R MASK | BITS (E | BIT 7) | ALARM RATE                                                         |

|-------|------|---------|--------|--------|---------|--------|--------------------------------------------------------------------|

|       | A1M6 | A1M5    | A1M4   | A1M3   | A1M2    | A1M1   |                                                                    |

| Х     | 1    | 1       | 1      | 1      | 1       | 1      | Alarm once a second                                                |

| Х     | 1    | 1       | 1      | 1      | 1       | 0      | Alarm when seconds match                                           |

| Х     | 1    | 1       | 1      | 1      | 0       | 0      | Alarm when minutes and seconds match                               |

| Х     | 1    | 1       | 1      | 0      | 0       | 0      | Alarm when hours, minutes, and seconds match                       |

| 0     | 1    | 1       | 0      | 0      | 0       | 0      | Alarm when dates, hours, minutes, and seconds match                |

| 0     | 1    | 0       | 0      | 0      | 0       | 0      | Alarm when months, dates, hours, minutes, and seconds match        |

| 0     | 0    | 0       | 0      | 0      | 0       | 0      | Alarm when years, months, dates, hours, minutes, and seconds match |

| 1     | 1    | 1       | 0      | 0      | 0       | 0      | Alarm when days, hours, minutes, and seconds match                 |

### Table 4. Alarm 2 Settings

| DY/DT | ALARM 2 F | REGISTER | MASK BITS (BIT 7) | ALARM RATE                                         |

|-------|-----------|----------|-------------------|----------------------------------------------------|

|       | A2M4      | A2M3     | A2M2              | Alarm once per minute (00 seconds of every minute) |

| х     | 1         | 1        | 1                 | Alarm when minutes match                           |

| х     | 1         | 1        | 0                 | Alarm when hours and minutes match                 |

| х     | 1         | 0        | 0                 | Alarm when dates, hours, and minutes match         |

| 0     | 0         | 0        | 0                 | Alarm when days, hours, and minutes match          |

| 1     | 0         | 0        | 0                 | Alarm when days, hours, and minutes match          |

#### **Countdown Timer**

The MAX31331 features a countdown timer with a pause function. The timer can be configured by writing into registers TIMER\_CONFIG (06h) and TIMER\_INIT (19h). The TIMER\_INIT register should be loaded with the initial value from which the timer would start counting down. The TIMER\_CONFIG register allows these configuration options:

- Select the frequency of the timer using the TFS[1:0] field.

- Start/stop the timer using the TE (Timer Enable) bit.

- Enable/disable the timer repeat function using the TRPT bit. This function reloads and restarts the timer with the same init value once it counts down to zero.

- Pause/resume the countdown at any time when the timer is enabled using the TPAUSE bit (explained as follows).

The timer can be programmed to assert the INT output (see <u>Table 5</u>) whenever it counts down to zero. This can be enabled/disabled using the TIE bit in register INT\_EN register (01h).

The TPAUSE bit is only valid when TE = 1. This bit must be reset to 0 whenever TE is reset to 0.

Table 5 highlights the steps for various use cases involving TE and TPAUSE.

Typical use cases:

- Countdown timer without pause: Step 1 → Step 2 → Step 1 and so on

- Countdown timer with pause: Step 1 → Step 2 → Step 3a → Step 3b → Step 1 and so on

| SEQUENCE                 | TE | TPAUSE | ACTION                                                                                                                                                             |

|--------------------------|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1                   | 0  |        | Countdown timer is reset, and ready for next countdown operation. Timer_init can be programmed in this state.                                                      |

| Step 2                   | 1  | 0      | Countdown timer starts counting down from the value programmed in Timer_init.                                                                                      |

| Step 3a<br>(Optional)    | 1  |        | Countdown timer is paused, and is ready to start counting down when TPAUSE is programmed back to '0'. Contents of the countdown timer are preserved in this state. |

| Step 3b<br>If 3a is true | 1  | 0      | Countdown timer is brought out of pause state, and starts counting down from the paused value.                                                                     |

|                          | 0  | 1      | Not allowed                                                                                                                                                        |

### Table 5. Countdown Timer Sequence

### Timestamps

The MAX31331 can record and store timestamps when triggered by specific events. Up to four timestamps can be stored in the four banks of timestamp registers (TS0, TS1, TS2, and TS3). Each TS bank contains seven registers for date/time information and one TSx\_Flags register to indicate which event triggered this timestamp.

The MAX31331 can be configured to record timestamps on these events:

- Rising/falling edge (configurable) on DIN pin .

- Supply switch from VCC to VBAT

- Supply switch from VBAT to VCC

- VBAT voltage drops below VBATLOW level (2V)

The part can either be configured to record only the first four timestamps and not record any subsequent events (TSOW = 0, Figure 4) or to keep recording every configured event and only keep the four latest events by overwriting the oldest event each time (TSOW = 1, Figure 5).

All the configuration related to timestamps can be found in the TIMESTAMP\_CONFIG (05h) register. To start recording timestamps, the TSVLOW, TSPWM, TSDIN, TSOW bits need to be configured as desired and the TSE (timestamp enable) bit should be set to 1. The timestamp banks can be read through I<sup>2</sup>C by accessing the corresponding register address. The TSR bit can be used to reset all the timestamp banks to 0 and start recording new timestamps again (if TSE = 1). When the timestamp functionality is not used (TSE = 0), all 32 bytes of timestamp registers can be used as user RAM. After setting TSE = 0, write TSR = 1 to ensure RAM functionality.

| EVENT1 | TS0<br>1 <sup>st</sup> Record | EVENT2 | TS0<br>2 <sup>nd</sup> Record | EVENT3 | TS0<br>3 <sup>rd</sup> Record | EVENT4 | TS0<br>4 <sup>th</sup> Record | EVENT5 | TS0<br>4 <sup>th</sup> Record |  |

|--------|-------------------------------|--------|-------------------------------|--------|-------------------------------|--------|-------------------------------|--------|-------------------------------|--|

|        | TS1                           |        | TS1<br>1 <sup>st</sup> Record |        | TS1<br>2 <sup>nd</sup> Record |        | TS1<br>3 <sup>rd</sup> Record |        | TS1<br>3 <sup>rd</sup> Record |  |

|        | TS2                           |        | TS2                           |        | TS2<br>1 <sup>st</sup> Record |        | TS2<br>2 <sup>nd</sup> Record |        | TS2<br>2 <sup>nd</sup> Record |  |

|        | TS3                           |        | TS3                           |        | TS3                           |        | TS3<br>1 <sup>st</sup> Record |        | TS3<br>1 <sup>st</sup> Record |  |

|        | TS3                           |        | T\$3                          |        | T\$3                          |        |                               |        |                               |  |

|        |                               |        |                               |        |                               |        |                               |        |                               |  |

|        |                               |        |                               |        |                               |        |                               |        |                               |  |

#### Figure 4. Limestamps with ISOW = 0

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |  | 5 <sup>th</sup> Record<br>TS1<br>4 <sup>th</sup> Record<br>TS2<br>3 <sup>rd</sup> Record<br>TS3 | EVENT5 | 4 <sup>th</sup> Record<br>TS1<br>3 <sup>rd</sup> Record<br>TS2<br>2 <sup>rd</sup> Record<br>TS3 | EVENT4 | 3 <sup>rd</sup> Record<br>TS1<br>2 <sup>nd</sup> Record<br>TS2<br>1 <sup>st</sup> Record | EVENT3 | 2 <sup>nd</sup> Record<br>TS1<br>1 <sup>st</sup> Record<br>TS2 | EVENT2 | TS1<br>TS2 | EVENT1 |  |

|---------------------------------------------------------|--|-------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------|--------|------------|--------|--|

|---------------------------------------------------------|--|-------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------|--------|------------|--------|--|

Figure 5. Timestamps with TSOW = 1

## **Applications Information**

#### **Power Supply Decoupling**

To achieve the best results when using the device, decouple the VCC and/or VBAT power supplies with 0.1µF and/or 1.0µF capacitors. Use a high-quality ceramic surface-mount capacitor if possible. Surface-mount components minimize lead inductance which improves performance and ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

#### Using Open-Drain Outputs

The  $\overline{INTA}$  and  $\overline{INTB}/CLKO$  outputs are open-drain and therefore require an external pullup resistor to realize logic-high output levels. Pullup resistor values around  $10k\Omega$  are typical.

#### Battery Leakage Current

When the MAX31331 switches from V<sub>CC</sub> to V<sub>BAT</sub> supply, the DIN pin buffer internally operates on the V<sub>BAT</sub> supply rail. If this pin is externally connected to an intermediate voltage level (between 0.7V and V<sub>BAT</sub> - 0.7V), then there is a high leakage current (tens of microamperes) on the V<sub>BAT</sub> supply. This scenario can occur when the system V<sub>CC</sub> rail is discharging and the MAX31331 has switched to V<sub>BAT</sub> supply, but the DIN pin is pulled up to the V<sub>CC</sub> rail. Set EN\_IO = 0 in RTC\_CONFIG1 (03h) register to ensure that the DIN pin is disabled before switching the main supply to V<sub>BAT</sub> to minimize the leakage current. The DIN pin is automatically enabled when the MAX31331 switches back to V<sub>CC</sub> supply. Alternatively, the DIN pin can be pulled up to V<sub>BAT</sub> instead of V<sub>CC</sub> to ensure minimal negligible leakage when running on V<sub>BAT</sub>.

#### **SDA and SCL Pullup Resistors**

SDA is an open-drain output and requires an external pullup resistor to realize a logic-high level. Because the device does not use clock cycle stretching, a master using either an open-drain output with a pullup resistor or CMOS output driver (push-pull) could be used for SCL.

### **Typical Application Circuits**

# **Register Map**

### RC31\_REGS

| ADDRESS | NAME                  | MSB         |                    |                    |                 |                  |         |                 | LSB     |

|---------|-----------------------|-------------|--------------------|--------------------|-----------------|------------------|---------|-----------------|---------|

| RTC_REG | I                     |             |                    |                    |                 |                  |         |                 |         |

| 0x00    | <u>STATUS[7:0]</u>    | PSDECT      | OSF                | PFAIL              | VBATLO<br>W     | DIF              | TIF     | A2F             | A1F     |

| 0x01    | <u>INT_EN[7:0]</u>    | -           | DOSF               | PFAILE             | VBATLO<br>WIE   | DIE              | TIE     | A2IE            | A1IE    |

| 0x02    | RTC_RESET[7:0]        | -           | _                  | -                  | -               | -                | -       | -               | SWRST   |

| 0x03    | RTC_CONFIG1[7:0]      | -           | EN_IO              | A1A0               | C[1:0]          | DIP              | _       | I2C_TIME<br>OUT | EN_OSC  |

| 0x04    | RTC_CONFIG2[7:0]      | _           | _                  | Ι                  | _               | Ι                | ENCLKO  | CLKO_           | HZ[1:0] |

| 0x05    | TIMESTAMP_CONFIG[7:0] | _           | _                  | TSVLOW             | TSPWM           | TSDIN            | TSOW    | TSR             | TSE     |

| 0x06    | TIMER_CONFIG[7:0]     | -           | -                  | -                  | TE              | TPAUSE           | TRPT    | TFS             | [1:0]   |

| 0x07    | SECONDS_1_128[7:0]    | -           | _1_2s              | _1_4s              | _1_8s           | _1_16s           | _1_32s  | _1_64s          | _1_128s |

| 0x08    | SECONDS[7:0]          | -           |                    | SEC_10[2:0]        |                 |                  | SECON   | IDS[3:0]        |         |

| 0x09    | MINUTES[7:0]          | -           |                    | MIN_10[2:0]        |                 | MINUTES[3:0]     |         |                 |         |

| 0x0A    | HOURS[7:0]            | _           | F_24_12            | HR_20_A<br>M_PM    | HR_10           |                  | HOU     | R[3:0]          |         |

| 0x0B    | <u>DAY[7:0]</u>       | -           | -                  | -                  | -               | -                |         | DAY[2:0]        |         |

| 0x0C    | DATE[7:0]             | -           | -                  | DATE_              | _10[1:0]        |                  | DAT     | E[3:0]          |         |

| 0x0D    | MONTH[7:0]            | CENTUR<br>Y | -                  | -                  | MONTH_1<br>0    |                  | MONT    | FH[3:0]         |         |

| 0x0E    | YEAR[7:0]             |             | YEAR_              | _10[3:0]           |                 |                  | YEAI    | R[3:0]          |         |

| 0x0F    | ALM1_SEC[7:0]         | A1M1        | A                  | 1_SEC_10[2:        | 0]              |                  | A1_SECO | ONDS[3:0]       |         |

| 0x10    | ALM1_MIN[7:0]         | A1M2        | A                  | 1_MIN_10[2:        | 0]              | A1_MINUTES[3:0]  |         |                 |         |

| 0x11    | ALM1_HRS[7:0]         | A1M3        | _                  | A1_HR_2<br>0_AM_PM | A1_HR_1<br>0    | A1_HOUR[3:0]     |         |                 |         |

| 0x12    | ALM1_DAY_DATE[7:0]    | A1M4        | A1_DY_D<br>T_MATCH | A1_DAT             | E_10[1:0]       | A1_DAY_DATE[3:0] |         |                 |         |

| 0x13    | ALM1_MON[7:0]         | A1M5        | A1M6               | -                  | A1_MONT<br>H_10 |                  | A1_MO   | NTH[3:0]        |         |

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

| ADDRESS   | NAME               | MSB         |                    |                    |              |              |                 |               | LSB            |  |

|-----------|--------------------|-------------|--------------------|--------------------|--------------|--------------|-----------------|---------------|----------------|--|

| 0x14      | ALM1_YEAR[7:0]     |             | A1_YEAR_10[3:0]    |                    |              |              | A1_YE           | AR[3:0]       |                |  |

| 0x15      | ALM2_MIN[7:0]      | A2M2        | А                  | 2_MIN_10[2:        | 0]           |              | A2_MINUTES[3:0] |               |                |  |

| 0x16      | ALM2_HRS[7:0]      | A2M3        | _                  | A2_HR_2<br>0_AM_PM | A2_HR_1<br>0 |              | A2_HC           | UR[3:0]       |                |  |

| 0x17      | ALM2_DAY_DATE[7:0] | A2M4        | A2_DY_D<br>T_MATCH | A2_DAT             | E_10[1:0]    |              | A2_DAY_         | DATE[3:0]     |                |  |

| 0x18      | TIMER_COUNT[7:0]   |             |                    |                    | TIMER_C      | OUNT[7:0]    |                 |               |                |  |

| 0x19      | TIMER_INIT[7:0]    |             |                    |                    | TIMER_       | INIT[7:0]    |                 |               |                |  |

| 0x1A      | PWR_MGMT[7:0]      | -           | -                  | -                  | -            | -            | -               | VBACK_S<br>EL | MANUAL_<br>SEL |  |

| 0x1B      | TRICKLE_REG[7:0]   | -           | -                  | -                  | _            | TRICKLE[2:0] |                 |               | EN_TRIC<br>KLE |  |

| 0x1D      | OFFSET_HIGH[7:0]   |             |                    |                    | COMPWO       | ORD[15:8]    |                 |               |                |  |

| 0x1E      | OFFSET_LOW[7:0]    |             | COMPWORD[7:0]      |                    |              |              |                 |               |                |  |

| TS_RAM_RE | G                  |             |                    |                    |              |              |                 |               |                |  |

| 0x20      | TS0_SEC_1_128[7:0] | _           | _1_2s              | _1_4s              | _1_8s        | _1_16s       | _1_32s          | _1_64s        | _1_128s        |  |

| 0x21      | TS0_SEC[7:0]       | _           |                    | SEC_10[2:0]        |              |              | SEC             | 2[3:0]        |                |  |

| 0x22      | TS0_MIN[7:0]       | -           |                    | MIN_10[2:0]        |              |              | MIN             | [3:0]         |                |  |

| 0x23      | TS0_HOUR[7:0]      | -           | F_24_12            | HR_20_A<br>M_PM    | HR_10        |              | HOU             | R[3:0]        |                |  |

| 0x24      | TS0_DATE[7:0]      | _           | _                  | DATE_              | _10[1:0]     |              | DAT             | E[3:0]        |                |  |

| 0x25      | TS0_MONTH[7:0]     | CENTUR<br>Y | -                  | -                  | MONTH_1<br>0 |              | MONT            | FH[3:0]       |                |  |

| 0x26      | TS0_YEAR[7:0]      |             | YEAR_              | _10[3:0]           |              |              | YEA             | R[3:0]        |                |  |

| 0x27      | TS0_FLAGS[7:0]     | _           | _                  | _                  | _            | VLOWF        | VBATF           | VCCF          | DINF           |  |

| 0x28      | TS1_SEC_1_128[7:0] | _           | _1_2s              | _1_4s              | _1_8s        | _1_16s       | _1_32s          | _1_64s        | _1_128s        |  |

| 0x29      | TS1_SEC[7:0]       | _           |                    | SEC_10[2:0]        |              |              | SEC             | [3:0]         |                |  |

| 0x2A      | TS1_MIN[7:0]       | _           |                    | MIN_10[2:0]        |              |              | MIN             | [3:0]         |                |  |

| 0x2B      | TS1_HOUR[7:0]      | _           | F_24_12            | HR_20_A<br>M_PM    | HR_10        |              | HOU             | R[3:0]        |                |  |

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

| ADDRESS | NAME               | MSB         |         |                 |              |            |            |        | LSB     |

|---------|--------------------|-------------|---------|-----------------|--------------|------------|------------|--------|---------|

| 0x2C    | TS1_DATE[7:0]      | -           | -       | DATE_           | _10[1:0]     | DATE[3:0]  |            |        |         |

| 0x2D    | TS1_MONTH[7:0]     | CENTUR<br>Y | _       | _               | MONTH_1<br>0 |            | MONTH[3:0] |        |         |

| 0x2E    | TS1_YEAR[7:0]      |             | YEAR_   | _10[3:0]        |              |            | YEA        | R[3:0] |         |

| 0x2F    | TS1_FLAGS[7:0]     | -           | -       | -               | -            | VLOWF      | VBATF      | VCCF   | DINF    |

| 0x30    | TS2_SEC_1_128[7:0] | -           | _1_2s   | _1_4s           | _1_8s        | _1_16s     | _1_32s     | _1_64s | _1_128s |

| 0x31    | TS2_SEC[7:0]       | -           |         | SEC_10[2:0]     |              |            | SEC        | [3:0]  |         |

| 0x32    | TS2_MIN[7:0]       | -           |         | MIN_10[2:0]     |              |            | MIN        | [3:0]  |         |

| 0x33    | TS2_HOUR[7:0]      | _           | F_24_12 | HR_20_A<br>M_PM | HR_10        | HOUR[3:0]  |            |        |         |

| 0x34    | TS2_DATE[7:0]      | -           | -       | DATE_           | _10[1:0]     | DATE[3:0]  |            |        |         |

| 0x35    | TS2_MONTH[7:0]     | CENTUR<br>Y | _       | _               | MONTH_1<br>0 | MONTH[3:0] |            |        |         |

| 0x36    | TS2_YEAR[7:0]      |             | YEAR_   | _10[3:0]        |              |            | YEA        | R[3:0] |         |

| 0x37    | TS2_FLAGS[7:0]     | _           | Ι       | Ι               | _            | VLOWF      | VBATF      | VCCF   | DINF    |

| 0x38    | TS3_SEC_1_128[7:0] | -           | _1_2s   | _1_4s           | _1_8s        | _1_16s     | _1_32s     | _1_64s | _1_128s |

| 0x39    | TS3_SEC[7:0]       | -           |         | SEC_10[2:0]     |              |            | SEC        | [3:0]  |         |

| 0x3A    | TS3_MIN[7:0]       | -           |         | MIN_10[2:0]     |              |            | MIN        | [3:0]  |         |

| 0x3B    | TS3_HOUR[7:0]      | _           | F_24_12 | HR_20_A<br>M_PM | HR_10        | HOUR[3:0]  |            |        |         |

| 0x3C    | TS3_DATE[7:0]      | -           | -       | DATE_           | _10[1:0]     | DATE[3:0]  |            |        |         |

| 0x3D    | TS3_MONTH[7:0]     | CENTUR<br>Y | _       | _               | MONTH_1<br>0 | MONTH[3:0] |            |        |         |

| 0x3E    | TS3_YEAR[7:0]      |             | YEAR_   | _10[3:0]        |              |            | YEA        | R[3:0] |         |

| 0x3F    | TS3_FLAGS[7:0]     | -           | -       | -               | _            | VLOWF      | VBATF      | VCCF   | DINF    |

### **Register Details**

STATUS (0x0)

Interrupt Status Register

| BIT         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Field       | PSDECT    | OSF       | PFAIL     | VBATLOW   | DIF       | TIF       | A2F       | A1F       |

| Reset       | 0b0       | 0b1       | 0b0       | 0x0       | 0b0       | 0b0       | 0b0       | 0b0       |

| Access Type | Read, Ext |

| BITFIELD | BITS | DESCRIPTION                                                                                             | DECODE                                                                                                                                                                                                                                                |

|----------|------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSDECT   | 7    | Main supply source indication. This bit is not cleared after successful I <sup>2</sup> C read.          | 0x0: Device is running on VCC<br>0x1: Device is running on VBAT                                                                                                                                                                                       |

| OSF      | 6    | Oscillator stop flag. This bit is not cleared after successful I <sup>2</sup> C read.                   | 0x0: Oscillator is running (or DOSF = 1)<br>0x1: Oscillator has stopped.                                                                                                                                                                              |

| PFAIL    | 5    | Power Fail interrupt flag. This bit is cleared automatically after successful I <sup>2</sup> C read.    | 0x0: No power fail condition on $V_{CC}$<br>0x1: There is a power fail condition on $V_{CC}$ . After an initial<br>power fail condition occurs, if the condition does not<br>persist, this bit can only be cleared by reading the Status<br>register. |

| VBATLOW  | 4    | VBAT Low interrupt flag. This bit is cleared automatically after successful I <sup>2</sup> C read.      | 0x0: VBAT > 2V<br>0x1: VBAT < 2V                                                                                                                                                                                                                      |

| DIF      | 3    | Digital (DIN) interrupt flag. This bit is cleared automatically after successful I <sup>2</sup> C read. | 0x0: DIN interrupt is not triggered.<br>0x1: DIN interrupt is trigerred.                                                                                                                                                                              |

| TIF      | 2    | Timer interrupt flag. This bit is cleared automatically after successful I <sup>2</sup> C read.         | 0x0: Countdown timer is still running.<br>0x1: Countdown timer elapses (COUNT = 0).                                                                                                                                                                   |

| A2F      | 1    | Alarm2 interrupt flag. This bit is cleared automatically after successful I <sup>2</sup> C read.        | 0x0: RTC time doesn't match the Alarm2 registers.<br>0x1: RTC time matches the Alarm2 registers.                                                                                                                                                      |

| A1F      | 0    | Alarm1 Interrupt flag. This bit cleared automatically after successful I <sup>2</sup> C read.           | 0x0: Set to zero when RTC time doesn't match to alarm1 register.<br>0x1: Set to 1 when RTC time matches the alarm1 register.<br>When this is set to 1, and A11E = 1, an interrupt will be generated on pin $\overline{INTA/INTB}$ .                   |

### INT\_EN (0x1)

Interrupt Enable Register

| BIT         | 7 | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|---|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | _ | DOSF        | PFAILE      | VBATLOWIE   | DIE         | TIE         | A2IE        | A1IE        |

| Reset       | _ | 0b0         | 0b0         | 0x0         | 0b0         | 0b0         | 0b0         | 0b0         |

| Access Type | _ | Write, Read |

| BITFIELD | BITS | DESCRIPTION             | DECODE                                                                                                                               |

|----------|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| DOSF     | 6    | Disable oscillator flag | 0x0: Allow the OSF to indicate the oscillator status.<br>0x1: Disable the oscillator flag, irrespective of the<br>oscillator status. |

# Ultra-Low-Power, I2C Real-Time Clock and Power Management

| BITFIELD  | BITS | DESCRIPTION                    | DECODE                                                                              |

|-----------|------|--------------------------------|-------------------------------------------------------------------------------------|

| PFAILE    | 5    | Power fail Interrupt enable    | 0x0: Enable PFAIL flag and interrupt<br>0x1: Disable PFAIL flag and interrupt       |

| VBATLOWIE | 4    | VBAT Low interrupt enable      | 0x0: Disable VBAT Low flag and interrupt<br>0x1: Enable VBAT Low flag and interrupt |

| DIE       | 3    | Digital (DIN) interrupt enable | 0x0: Disable DIN flag and interrupt<br>0x1: Enable DIN flag and interrupt           |

| TIE       | 2    | Timer interrupt enable         | 0x0: Disable Timer flag and interrupt<br>0x1: Enable Timer flag and interrupt       |

| A2IE      | 1    | Alarm2 interrupt enable        | 0x0: Disable Alarm2 flag and interrupt<br>0x1: Enable Alarm2 flag and interrupt     |

| A1IE      | 0    | Alarm1 interrupt enable        | 0x0: Disable Alarm1 flag and interrupt<br>0x1: Enable Alarm1 flag and interrupt     |

### RTC\_RESET (0x2)

### RTC Software Reset Register

| BIT         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0                   |

|-------------|---|---|---|---|---|---|---|---------------------|

| Field       | - | - | - | - | - | - | - | SWRST               |

| Reset       | _ | _ | _ | _ | _ | _ | _ | 0b0                 |

| Access Type | _ | _ | _ | _ | _ | _ | _ | Write, Read,<br>Ext |

| BITFIELD | BITS | DESCRIPTION                    | DECODE                                                                                                                                                                                      |

|----------|------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWRST    | 0    | Active high software reset bit | 0x0: Device is in normal mode.<br>0x1: Resets the digital block and the I <sup>2</sup> C programmable<br>registers except for RAM registers and<br>RTC_reset.SWRST. Oscillator is disabled. |

### RTC\_CONFIG1 (0x3)

**RTC** Configuration Register 1

| BIT         | 7 | 6           | 5         | 4    | 3           | 2 | 1               | 0           |

|-------------|---|-------------|-----------|------|-------------|---|-----------------|-------------|

| Field       | - | EN_IO       | A1AC[1:0] |      | DIP         | - | I2C_TIMEOU<br>T | EN_OSC      |

| Reset       | _ | 0b1         | 0x0       |      | 060         | _ | 0b1             | 0b1         |

| Access Type | _ | Write, Read | Write,    | Read | Write, Read | _ | Write, Read     | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                      | DECODE                                                                                    |