### **FEATURES**

- 600-kHz Sample Rate

- ±2 LSB Typ, ±4 LSB Max INL

- 18-Bit NMC Ensured Over Temperature

- SINAD 91 dB, SFDR 119 dB at f<sub>i</sub> = 1 kHz

- High-Speed Serial Interface up to 40 MHz

- Onboard Reference Buffer

- Onboard 4.096-V Reference

- Pseudo-Differential Input, 0 V to 4.2 V

- Onboard Conversion Clock

- Selectable Output Format, 2's Complement or Straight Binary

- Zero Latency

- Wide Digital Supply

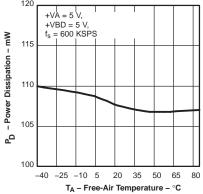

- Low Power:

- 115 mW at 600 kHz

- 15 mW During Nap Mode

- 10 μW During Power Down

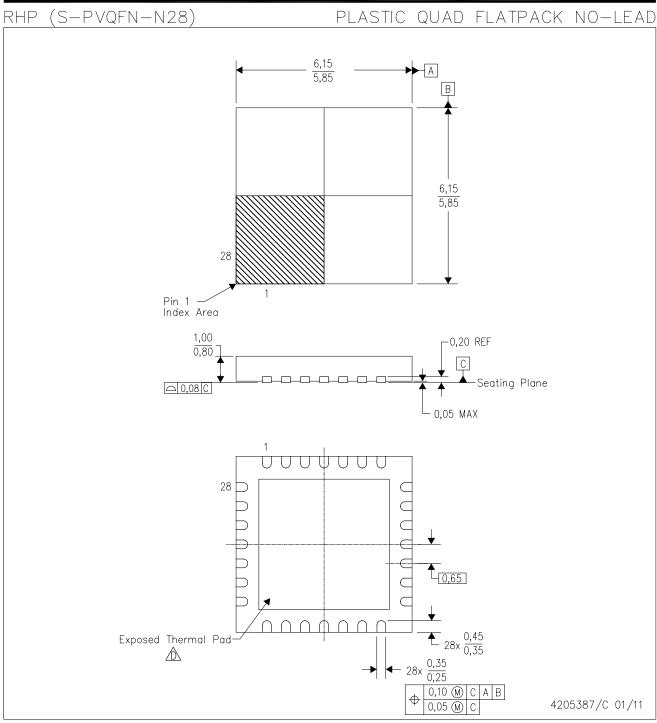

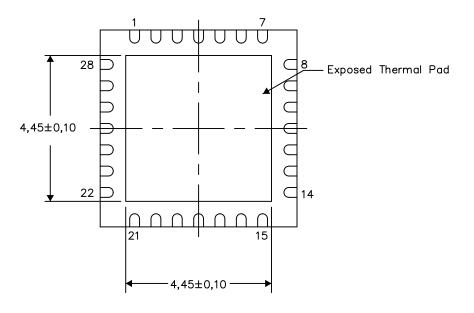

- 28-Pin 6 x 6 QFN Package

# **APPLICATIONS**

- Medical Instruments

- Optical Networking

- Transducer Interface

- High Accuracy Data Acquisition Systems

- Magnetometers

## **DESCRIPTION**

The ADS8380 is a high performance 18-bit, 600-kHz A/D converter with single-ended (pseudo-differential) input. The device includes an 18-bit capacitor-based SAR A/D converter with inherent sample and hold. The ADS8380 offers a high-speed CMOS serial interface with clock speeds up to 40 MHz.

The ADS8380 is available in a 28 lead  $6 \times 6$  QFN package and is characterized over the industrial  $-40^{\circ}$ C to 85°C temperature range.

### **High Speed SAR Converter Family**

| Type/Speed                        | 500 kHz | ~ 600 kHz   | 750 kHZ | ) kHZ   |             | 2 MHz   | 3 MHz   | 4 MHz   |

|-----------------------------------|---------|-------------|---------|---------|-------------|---------|---------|---------|

| 40 Dit Daguda Diff                | ADS8383 | ADS8381     |         |         |             |         |         |         |

| 18-Bit Pseudo-Diff                |         | ADS8380 (S) |         |         |             |         |         |         |

| 18-Bit Pseudo-Bipolar, Fully Diff |         | ADS8382 (S) |         |         |             |         |         |         |

| 16-Bit Pseudo-Diff                |         |             | ADS8371 |         | ADS8401/05  | ADS8411 |         |         |

| 16-Bit Pseudo-Bipolar, Fully Diff |         |             |         |         | ADS8402/06  | ADS8412 |         |         |

| 14-Bit Pseudo-Diff                |         |             |         |         | ADS7890 (S) |         | ADS7891 |         |

| 12-Bit Pseudo-Diff                |         |             |         | ADS7886 |             |         |         | ADS7881 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ORDERING INFORMATION(1)

| MODEL     | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES<br>RESOLUTION<br>(BIT) | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QUANTITY |

|-----------|-------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------|-----------------------|----------------------|-------------------------|--------------------------------|

| ADS8380I  | ±6                                        | -2/2.5                                        | 17                                         | 28 Pin          | DUD                   | –40°C to 85°C        | ADS8380IRHPT            | Small Tape and reel 250        |

| AD363601  | ±0                                        | -2/2.5                                        | 17                                         | 6x6 QFN RHP -   |                       | -40 C to 65 C        | ADS8380IRHPR            | Tape and reel<br>2500          |

| ADC0200ID | ±4                                        | -1/1.5                                        | 18                                         | 28 Pin          | RHP                   | -40°C to 85°C        | ADS8380IBRHPT           | Small Tape and reel 250        |

| ADS8380IB | ±4                                        | -1/1.5                                        | 10                                         | 6×6 QFN         | MIT                   | -40 C 10 65 C        | ADS8380IBRHPR           | Tape and reel<br>2500          |

<sup>(1)</sup> For the most current specifications and package information, refer to our web site at www.ti.com

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted (1)

|                                          |                                                  | UNIT                             |  |  |  |

|------------------------------------------|--------------------------------------------------|----------------------------------|--|--|--|

|                                          | +IN to AGND                                      | -0.3 V to +VA + 0.3 V            |  |  |  |

| Valtana                                  | -IN to AGND                                      | -0.3 V to +VA + 0.3 V            |  |  |  |

| Voltage                                  | +VA to AGND                                      | –0.3 V to 7 V                    |  |  |  |

|                                          | +VBD to BDGND                                    | –0.3 V to 7 V                    |  |  |  |

| Digital input voltage to BDGN            | ital input voltage to BDGND -0.3 V to +VBD + 0.3 |                                  |  |  |  |

| Digital input voltage to +VA             | gital input voltage to +VA +0.3 V                |                                  |  |  |  |

| Operating free-air temperatur            | e range, T <sub>A</sub>                          | -40°C to 85°C                    |  |  |  |

| Storage temperature range, T             | -<br>stg                                         | −65°C to 150°C                   |  |  |  |

| Junction temperature (T <sub>J</sub> max | ()                                               | 150°C                            |  |  |  |

| OEN poekege                              | Power dissipation                                | $(T_{J}max - T_{A})/\theta_{JA}$ |  |  |  |

| QFN package                              | $\theta_{JA}$ thermal impedance                  | 86°C/W                           |  |  |  |

| Load tomporature, coldering              | Vapor phase (60 sec)                             | 215°C                            |  |  |  |

| Lead temperature, soldering              | Infrared (15 sec)                                | 220°C                            |  |  |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **SPECIFICATIONS**

At  $-40^{\circ}$ C to  $85^{\circ}$ C, +VA = +5 V, +VBD = +5 V or +VBD = +2.7 V, using internal or external reference,  $f_{SAMPLE} = 600$  kHz, unless otherwise noted. (All performance parameters are valid only after device has properly resumed from power down, see Table 2.)

|       | DADAMETED                                              | TEST CONDITIONS                                                                                 | AI     | DS8380IB |                        | ADS8380I |     |                        | UNIT     |

|-------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|----------|------------------------|----------|-----|------------------------|----------|

|       | PARAMETER                                              | TEST CONDITIONS                                                                                 | MIN    | TYP      | MAX                    | MIN      | TYP | MAX                    | UNIT     |

| ANALO | G INPUT                                                |                                                                                                 |        |          | "                      |          |     |                        |          |

|       | Full-scale input voltage <sup>(1)</sup>                | +IN - (-IN)                                                                                     | 0      |          | V <sub>ref</sub>       | 0        |     | $V_{ref}$              | V        |

|       | Abachita innut valtaga                                 | +IN                                                                                             | -0.2   |          | V <sub>ref</sub> + 0.2 | -0.2     |     | V <sub>ref</sub> + 0.2 | V        |

|       | Absolute input voltage                                 | -IN                                                                                             | -0.2   |          | 0.2                    | -0.2     |     | 0.2                    | V        |

|       | Sampling capacitance<br>(measured from ±IN to<br>AGND) |                                                                                                 |        | 40       |                        |          | 40  |                        | pF       |

|       | Input leakage current                                  |                                                                                                 |        | 1        |                        |          | 1   |                        | nA       |

| SYSTE | M PERFORMANCE                                          |                                                                                                 |        |          | ·                      |          |     |                        |          |

|       | Resolution                                             |                                                                                                 |        | 18       |                        |          | 18  |                        | Bits     |

|       | No missing codes                                       |                                                                                                 | 18     |          |                        | 17       |     |                        | Bits     |

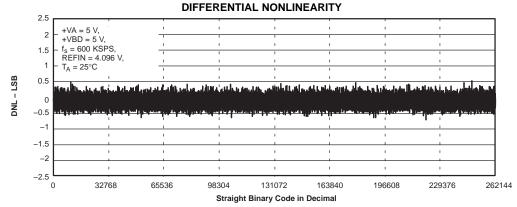

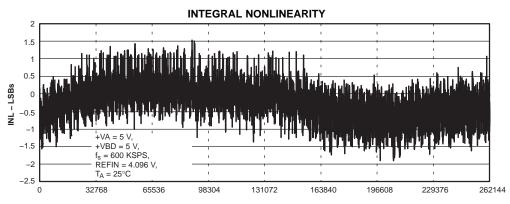

| INL   | IL Integral linearity (2)(3)(4)                        | Quiet zones observed                                                                            | -4     | ±2       | 4                      | -6       |     | 6                      | LSB      |

| IINL  | integral linearity (2)(4)                              | Quiet zones not observed                                                                        |        | ±2.75    |                        |          |     |                        | (18 bit) |

| DNL   | Differential linearity <sup>(3)</sup>                  | Quiet zones observed                                                                            | -1     | ±0.75    | 1.5                    | -2       |     | 2.5                    | LSB      |

| DINL  | Differential linearity (9)                             | Quiet zones not observed                                                                        |        | ±1.5     |                        |          |     | 1.5                    | (18 bit) |

| Eo    | Offset error (3)                                       |                                                                                                 | -0.75  | ±0.4     | 0.75                   | -1.5     |     | 1.5                    | mV       |

| $E_G$ | Gain error <sup>(3)(5)</sup>                           |                                                                                                 | -0.075 |          | 0.075                  | -0.1     |     | 0.1                    | %FS      |

|       |                                                        | At DC                                                                                           |        | 80       |                        |          | 80  |                        |          |

| CMRR  | Common-mode rejection ratio                            | [+IN - (-IN)] = V <sub>ref</sub> /2 with<br>50 mV <sub>p-p</sub> common mode<br>signal at 1 MHz |        | 55       |                        |          | 55  |                        | dB       |

|       | Noise                                                  | At 0 V analog input                                                                             |        | 40       |                        |          | 40  |                        | μV RMS   |

| PSRR  | DC Power supply rejection ratio                        | At full scale analog input                                                                      |        | 55       |                        |          | 55  |                        | dB       |

| SAMPL | ING DYNAMICS                                           |                                                                                                 |        |          |                        |          |     |                        |          |

|       | Conversion time                                        |                                                                                                 |        |          | 1.16                   |          |     | 1.16                   | μs       |

|       | Acquisition time                                       |                                                                                                 | 0.50   |          | 1000                   | 0.50     |     | 1000                   | μs       |

|       | Throughput rate                                        |                                                                                                 |        |          | 600                    |          |     | 600                    | kHz      |

|       | Aperture delay                                         |                                                                                                 |        | 10       |                        |          | 10  |                        | ns       |

|       | Aperture jitter                                        |                                                                                                 |        | 12       |                        |          | 12  |                        | ps RMS   |

|       | Step response                                          | (6)                                                                                             |        | 400      |                        |          | 400 |                        | ns       |

|       | Overvoltage recovery                                   |                                                                                                 |        | 400      |                        |          | 400 |                        | ns       |

- (1) Ideal input span; does not include gain or offset error.

- (2) LSB means least significant bit.

- (3) Measured using analog input circuit in Figure 51 and digital stimulus in Figure 56 and Figure 57 and reference voltage of 4.096 V.

- (4) This is endpoint INL, not best fit.

- (5) Measured using external reference source so does not include internal reference voltage error or drift.

- (6) Defined as sampling time necessary to settle an initial error of Vref on the sampling capacitor to a final error of 1 LSB at 18-bit level. Measured using the input circuit in Figure 51.

# **SPECIFICATIONS** (continued)

At  $-40^{\circ}$ C to  $85^{\circ}$ C, +VA = +5 V, +VBD = +5 V or +VBD = +2.7 V, using internal or external reference,  $f_{SAMPLE} = 600$  kHz, unless otherwise noted. (All performance parameters are valid only after device has properly resumed from power down, see Table 2.)

|                  | PARAMETER                                              |                                     |                                     | 1                   | DS8380IB |            |           | ADS8380I |            | UNIT   |

|------------------|--------------------------------------------------------|-------------------------------------|-------------------------------------|---------------------|----------|------------|-----------|----------|------------|--------|

|                  |                                                        |                                     | TEST CONDITIONS                     | MIN                 | TYP      | MAX        | MIN       | TYP MAX  |            | UNII   |

| DYNAMI           | IC CHARACTER                                           | RISTICS                             |                                     |                     |          |            |           |          |            |        |

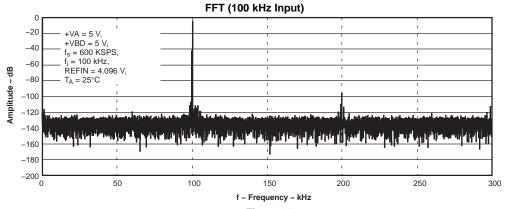

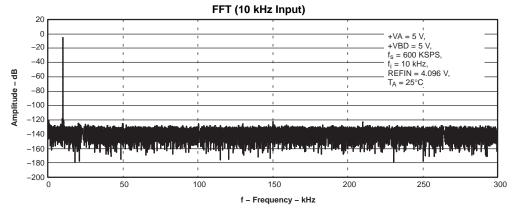

|                  |                                                        |                                     | VIN = 4 V <sub>p-p</sub> at 1 kHz   |                     | -112     |            |           | -112     |            |        |

| THD              | Total harmonic distortion (7)(8)                       |                                     | VIN = 4 V <sub>p-p</sub> at 10 kHz  |                     | -112     |            |           | -112     |            | dB     |

|                  |                                                        |                                     | $VIN = 4 V_{p-p}$ at 100 kHz        |                     | -92      |            |           | -92      |            |        |

|                  |                                                        |                                     | VIN = 4 V <sub>p-p</sub> at 1 kHz   |                     | 91       |            |           | 91       |            |        |

| SNR              | Signal-to-noise                                        | ratio (7)                           | VIN = 4 V <sub>p-p</sub> at 10 kHz  |                     | 91       |            | 91        |          |            | dB     |

|                  |                                                        |                                     | VIN = 4 V <sub>p-p</sub> at 100 kHz |                     | 89.5     |            | 89.5      |          |            |        |

|                  |                                                        |                                     | $VIN = 4 V_{p-p}$ at 1 kHz          |                     | 91       |            |           | 91       |            | ì      |

| SINAD            | INAD Signal-to-noise<br>+ distortion <sup>(7)(8)</sup> |                                     | $VIN = 4 V_{p-p}$ at 10 kHz         |                     | 91       |            |           | 91       |            | dB     |

|                  |                                                        |                                     | $VIN = 4 V_{p-p}$ at 100 kHz        |                     | 87.5     |            |           |          |            |        |

|                  |                                                        |                                     | VIN = 4 V <sub>p-p</sub> at 1 kHz   |                     | 119      |            |           | 119      |            |        |

| SFDR             | Spurious free d<br>range <sup>(7)</sup>                | ynamic                              | VIN = 4 V <sub>p-p</sub> at 10 kHz  |                     | 117      |            |           | 117      |            | dB     |

|                  | .ago                                                   |                                     | VIN = 4 V <sub>p-p</sub> at 100 kHz |                     | 92       |            |           | 92       |            |        |

|                  | -3dB Small sign                                        | nal                                 |                                     |                     | 75       |            |           | 75       |            | MHz    |

| REFERE           | ENCE INPUT                                             |                                     | ı                                   |                     |          |            |           |          |            |        |

| $V_{ref}$        | Reference volta                                        | age input                           |                                     | 2.5                 | 4.096    | 4.2        | 2.5       | 4.096    | 4.2        | V      |

|                  | Resistance (9)                                         |                                     |                                     |                     | 10       |            |           | 10       |            | МΩ     |

| NTERN            | AL REFERENCE                                           | E OUTPUT                            |                                     | 1                   |          |            |           |          |            |        |

| V <sub>ref</sub> | Reference volta                                        | age range                           | IOUT = 0 A, T <sub>A</sub> = 30°C   | 4.088               | 4.096    | 4.104      | 4.088     | 4.096    | 4.104      | V      |

|                  | Source current                                         |                                     | Static load                         |                     |          | 10         |           |          | 10         | μΑ     |

|                  | Line regulation                                        | gulation +VA = 4.75 V to 5.25 V 2.5 |                                     | 2.5                 |          | mV         |           |          |            |        |

| -                | Drift                                                  |                                     | IOUT = 0 A                          |                     | 25       |            |           | 25       |            | ppm/°C |

| DIGITAL          | INPUT/OUTPU                                            | Т                                   |                                     |                     |          |            |           |          |            |        |

| -                | Logic family CM                                        | //OS                                |                                     |                     |          |            |           |          |            |        |

| V <sub>IH</sub>  | High level input                                       | voltage                             |                                     | +VBD - 1            |          | +VBD + 0.3 | +VBD - 1  |          | +VBD + 0.3 | V      |

| V <sub>IL</sub>  | Low level input                                        | voltage                             |                                     | -0.3                |          | 0.8        | -0.3      |          | 0.8        | V      |

| V <sub>OH</sub>  | High level outpu                                       | ut voltage                          | I <sub>OH</sub> = 2 TTL loads       | +VBD -0.6           |          |            | +VBD -0.6 |          |            | V      |

| V <sub>OL</sub>  | Low level output                                       | ıt voltage                          | I <sub>OL</sub> = 2 TTL loads       |                     |          | 0.4        |           |          | 0.4        | V      |

|                  | Data format: MS                                        | SB first, 2's                       | complement or straight bina         | ary (selectable via | the SB/2 | C pin)     |           |          |            |        |

| POWER            | SUPPLY REQU                                            | IREMENT                             | S                                   |                     |          |            |           |          |            |        |

|                  | Power supply                                           | +VA                                 |                                     | 4.75                | 5        | 5.25       | 4.75      | 5        | 5.25       | V      |

|                  | voltage                                                | +VBD                                |                                     | 2.7                 | 3.3      | 5.25       | 2.7       | 3.3      | 5.25       | V      |

| lcc              | Supply current, sample rate <sup>(10)</sup>            |                                     | +VA = 5 V                           |                     | 22       | 25         |           | 22       | 25         | mA     |

| POWER            | DOWN                                                   |                                     |                                     |                     |          |            |           |          |            |        |

| CC(PD)           | Supply current, down                                   | power                               |                                     |                     | 2        |            |           | 2        |            | μΑ     |

| NAP MO           | DDE                                                    |                                     | •                                   | •                   |          |            |           |          |            |        |

| CC(NAP)          | Supply current, mode                                   | nap                                 |                                     |                     | 3        |            |           | 3        |            | mA     |

|                  | Power-up time                                          | from nap                            |                                     |                     |          | 300        |           |          | 300        | ns     |

| ГЕМРЕР           | RATURE RANGE                                           | E                                   | •                                   | •                   |          |            |           |          |            |        |

|                  | Specified perfor                                       | rmance                              |                                     | -40                 |          | 85         | -40       |          | 85         | °C     |

- (7) Measured using analog input circuit in Figure 51 and digital stimulus in Figure 56 and Figure 57 and reference voltage of 4.096 V.

- (8) Calculated on the first nine harmonics of the input frequency.

- (9) Can vary +/-30%.

- (10) This includes only +VA current. With +VBD = 5 V, +VBD current is typically 1 mA with a 10-pF load capacitance on the digital output pins.

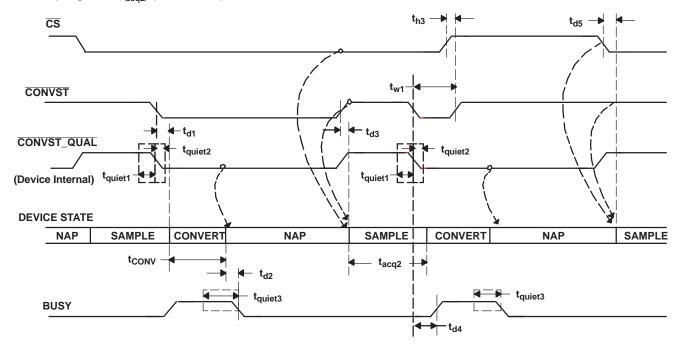

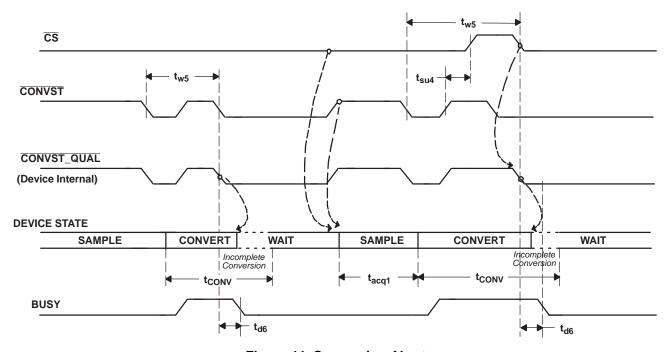

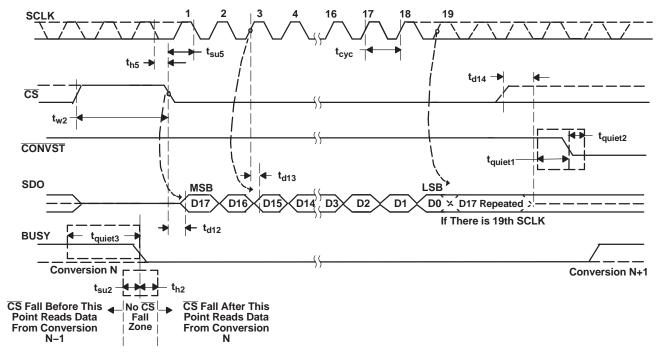

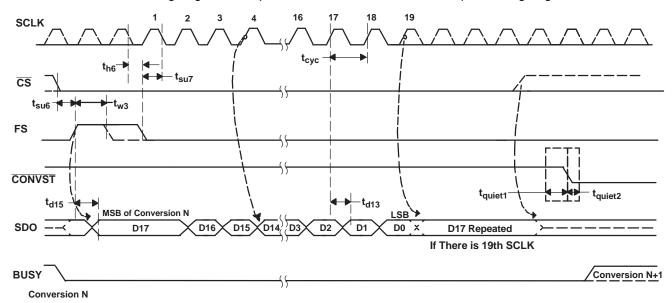

# **TIMING REQUIREMENTS**<sup>(1)(2)(3)(4)(5)(6)</sup>

|                     | DADAMETER                                                                                                                       | ADS8386  | 01/ADS838 | 0IB  | LINUT | REF                 |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------|-------|---------------------|--|

|                     | PARAMETER                                                                                                                       | MIN      | TYP       | MAX  | UNIT  | FIGURE              |  |

| t <sub>conv</sub>   | Conversion time                                                                                                                 | 1000     |           | 1160 | ns    | 41 – 44             |  |

| t <sub>acq1</sub>   | Acquisition time in normal mode                                                                                                 | 0.5      |           | 1000 | μs    | 41,42,44            |  |

| t <sub>acq2</sub>   | Acquisition time in nap mode ( $t_{acq2} = t_{acq1} + t_{d18}$ )                                                                | 0.8      |           | 1000 | μs    | 43                  |  |

|                     | ERSION AND SAMPLING                                                                                                             | <u> </u> |           |      |       |                     |  |

| t <sub>quiet1</sub> | Quite sampling time (last toggle of interface signals to convert start command) (6)                                             | 30       |           |      | ns    | 40 – 43,<br>45 – 47 |  |

| t <sub>quiet2</sub> | Quite sampling time (convert start command to first toggle of interface signals) <sup>(6)</sup>                                 | 10       |           |      | ns    | 40 – 43,<br>45 – 47 |  |

| t <sub>quiet3</sub> | Quite conversion time (last toggle of interface signals to fall of BUSY) (6)                                                    | 600      |           |      | ns    | 40 – 43,<br>45,47   |  |

| t <sub>su1</sub>    | Setup time, CONVST before BUSY fall                                                                                             | 15       |           |      | ns    | 41                  |  |

| t <sub>su2</sub>    | Setup time, CS before BUSY fall (only for conversion/sampling control)                                                          | 20       |           |      | ns    | 40,41               |  |

| t <sub>su4</sub>    | Setup time, CONVST before CS rise (so CONVST can be recognized)                                                                 | 5        |           |      | ns    | 41,43,44            |  |

| t <sub>h1</sub>     | Hold time, CS after BUSY fall (only for conversion/sampling control)                                                            | 0        |           |      | ns    | 41                  |  |

| t <sub>h3</sub>     | Hold time, CONVST after CS rise                                                                                                 | 7        |           |      | ns    | 43                  |  |

| t <sub>h4</sub>     | Hold time, CONVST after CS fall (to ensure width of CONVST_QUAL)(4)                                                             | 20       |           |      | ns    | 42                  |  |

| t <sub>w1</sub>     | CONVST pulse duration                                                                                                           | 20       |           |      | ns    | 43                  |  |

| t <sub>w2</sub>     | CS pulse duration                                                                                                               | 10       |           |      | ns    | 41,42               |  |

| t <sub>w5</sub>     | Pulse duration, time between conversion start command and conversion abort command to successfully abort the ongoing conversion |          |           | 1000 | ns    | 44                  |  |

| DATA                | READ OPERATION                                                                                                                  |          |           |      |       |                     |  |

| t <sub>cyc</sub>    | SCLK period                                                                                                                     | 25       |           |      | ns    | 45 – 47             |  |

|                     | SCLK duty cycle                                                                                                                 | 40%      |           | 60%  |       |                     |  |

| t <sub>su5</sub>    | Setup time, CS fall before first SCLK fall                                                                                      | 10       |           |      | ns    | 45                  |  |

| t <sub>su6</sub>    | Setup time, $\overline{\text{CS}}$ fall before FS rise                                                                          | 7        |           |      | ns    | 46,47               |  |

| t <sub>su7</sub>    | Setup time, FS fall before first SCLK fall                                                                                      | 7        |           |      | ns    | 46,47               |  |

| t <sub>h5</sub>     | Hold time, $\overline{\text{CS}}$ fall after SCLK fall                                                                          | 3        |           |      | ns    | 45                  |  |

| t <sub>h6</sub>     | Hold time, FS fall after SCLK fall                                                                                              | 7        |           |      | ns    | 46,47               |  |

| t <sub>su2</sub>    | Setup time, CS fall before BUSY fall (only for read control)                                                                    | 20       |           |      | ns    | 40,45               |  |

| t <sub>su3</sub>    | Setup time, FS fall before BUSY fall (only for read control)                                                                    | 20       |           |      | ns    | 40,47               |  |

| t <sub>h2</sub>     | Hold time, $\overline{\text{CS}}$ fall after BUSY fall (only for read control)                                                  | 15       |           |      | ns    | 40,45               |  |

| t <sub>h8</sub>     | Hold time, FS fall after BUSY fall (only for read control)                                                                      | 15       |           |      | ns    | 40,47               |  |

| t <sub>w2</sub>     | CS pulse duration                                                                                                               | 10       |           |      | ns    | 45                  |  |

| t <sub>w3</sub>     | FS pulse duration                                                                                                               | 10       |           |      | ns    | 46,47               |  |

| MISCE               | ELLANEOUS                                                                                                                       |          |           |      |       |                     |  |

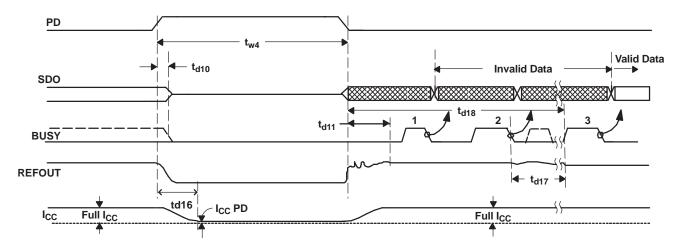

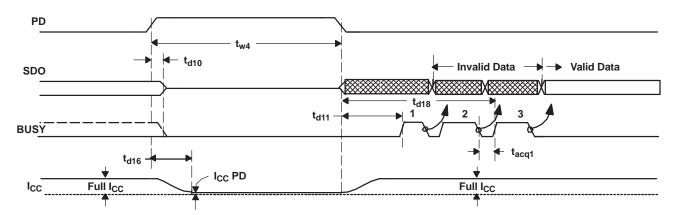

| t <sub>w4</sub>     | PD pulse duration for reset and power down                                                                                      | 60       |           |      | ns    | 53,54               |  |

|                     | All unspecified pulse durations                                                                                                 | 10       |           |      | ns    |                     |  |

|                     |                                                                                                                                 |          |           |      |       |                     |  |

- All input signals are specified with  $t_r = t_f = 5$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . All specifications typical at  $-40^{\circ}$ C to  $85^{\circ}$ C, +VA = +4.75 V to +5.25 V, +VBD = +2.7 V to +5.25 V. All digital output signals loaded with 10-pF capacitors. CONVST\_QUAL is CONVST latched by a low value on  $\overline{CS}$  (see Figure 39). Reference figure indicated is only a representative of where the timing is applicable and is not exhaustive. Quiet time zones are for meeting performance and not functionality.

- (2)

- (<del>5</del>)

# TIMING CHARACTERISTICS(1)(2)(3)(4)

|                  |                                         | DADAMETED                                                                                                          | ADS8 | 380I/ADS | 88380IB                              |      | REF     |

|------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|----------|--------------------------------------|------|---------|

|                  |                                         | PARAMETER                                                                                                          | MIN  | TYP      | MAX                                  | UNIT | FIGURE  |

| CON              | IVERSION AND SAM                        | MPLING                                                                                                             |      |          |                                      |      |         |

| t <sub>d1</sub>  | Delay time, convers                     | ion start command to conversion start (aperture delay)                                                             |      |          | 10                                   | ns   | 41,43   |

| t <sub>d2</sub>  | Delay time, convers                     | ion end to BUSY fall                                                                                               |      |          | 5                                    | ns   | 41 – 43 |

| $t_{d4}$         | Delay time, convers                     | ion start command to BUSY rise                                                                                     |      |          | 20                                   | ns   | 41      |

| $t_{d3}$         | Delay time, CONVS                       | T rise to sample start                                                                                             |      |          | 5                                    | ns   | 43      |

| t <sub>d5</sub>  | Delay time, CS fall t                   | o sample start                                                                                                     |      |          | 10                                   | ns   | 43      |

| t <sub>d6</sub>  | Delay time, convers                     | ion abort command to BUSY fall                                                                                     |      |          | 10                                   | ns   | 44      |

| DAT              | A READ OPERATIO                         | N                                                                                                                  |      |          |                                      |      |         |

| t <sub>d12</sub> | Delay time, CS fall t                   | o MSB valid                                                                                                        | 3    |          | 15                                   | ns   | 45      |

| t <sub>d15</sub> | Delay time, FS rise                     | to MSB valid                                                                                                       | 6    |          | 18                                   | ns   | 46,47   |

| t <sub>d7</sub>  | Delay time, BUSY fa                     | all to MSB valid (if FS is high when BUSY falls)                                                                   |      |          | 18                                   | ns   | 47      |

| t <sub>d13</sub> | Delay time, SCLK ri                     | se to bit valid                                                                                                    | 2    |          | 10                                   | ns   | 45– 47  |

| t <sub>d14</sub> | Delay time, $\overline{\text{CS}}$ rise | to SDO 3-state                                                                                                     |      |          | 6                                    | ns   | 45      |

| MIS              | CELLANEOUS                              |                                                                                                                    |      |          |                                      |      |         |

| t <sub>d10</sub> | Delay time, PD rise                     | to SDO 3-state                                                                                                     |      |          | 55                                   | ns   | 53,54   |

|                  |                                         | Nap mode                                                                                                           |      |          | 300                                  | ns   | 55      |

| t <sub>d18</sub> | Delay time, total device resume         | Full power down (external reference used with or without 1-μF  0.1-μF capacitor on REFOUT)                         |      | C        | t <sub>d11</sub> + 2x<br>conversions |      | 54      |

|                  | time                                    | Full power down (internal reference used with or without 1-μF  0.1-μF capacitor on REFOUT)                         |      |          | 25 <sup>(4)</sup>                    | ms   | 53      |

| t <sub>d11</sub> | Delay time, untrimm                     | ed circuit full power-down resume time                                                                             |      |          | 1                                    | ms   | 53,54   |

| +                | Delay time, device                      | Nap                                                                                                                |      | 200      |                                      | ns   | 55      |

| t <sub>d16</sub> | power-down time                         | Full power down (internal/external reference used)                                                                 |      | 10       |                                      | μs   | 53,54   |

| t <sub>d17</sub> |                                         | internal reference settling (either by turning on supply or ower-down mode), with 1-µF  0.1-µF capacitor on REFOUT |      |          | 4                                    | ms   | 53      |

<sup>(1)</sup> All input signals are specified with t<sub>r</sub> = t<sub>f</sub> = 5 ns (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2.

(2) All specifications typical at -40°C to 85°C, +VA = +4.75 V to +5.25 V, +VBD = +2.7 V to +5.25 V.

(3) All digital output signals loaded with 10-pF capacitors.

(4) Including t<sub>d11</sub>, two conversions (time to cycle CONVST twice), and t<sub>d17</sub>.

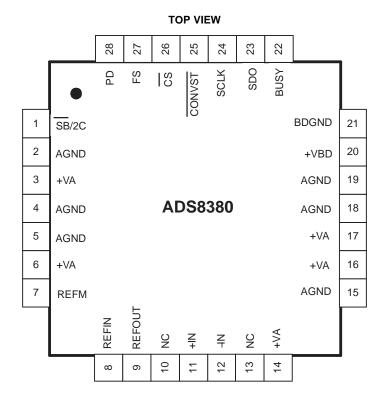

# **PIN ASSIGNMENTS**

# **TERMINAL FUNCTIONS**

| Р         | IN                     |     | DESCRIPTION                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME      | NO.                    | I/O | DESCRIFTION                                                                                                                                                                    |  |  |  |  |  |  |  |

| AGND      | 2, 4, 5, 15,<br>18, 19 | _   | Analog ground pins. AGND must be shorted to analog ground plane below the device.                                                                                              |  |  |  |  |  |  |  |

| BDGND     | 21                     | -   | Digital ground for all digital inputs and outputs. BDGND must be shorted to the analog ground plane below the device.                                                          |  |  |  |  |  |  |  |

| BUSY      | 22                     | 0   | Status output. This pin is high when conversion is in progress.                                                                                                                |  |  |  |  |  |  |  |

| CONVST    | 25                     | I   | Convert start. This signal is qualified with $\overline{\text{CS}}$ internally.                                                                                                |  |  |  |  |  |  |  |

| <u>cs</u> | 26                     | Ι   | Chip select                                                                                                                                                                    |  |  |  |  |  |  |  |

| FS        | 27                     | ı   | Frame sync. This signal is qualified with $\overline{\text{CS}}$ internally.                                                                                                   |  |  |  |  |  |  |  |

| +IN       | 11                     | ı   | Noninverting analog input channel                                                                                                                                              |  |  |  |  |  |  |  |

| -IN       | 12                     | ı   | Inverting analog input channel                                                                                                                                                 |  |  |  |  |  |  |  |

| NC        | 10, 13                 | _   | No connection                                                                                                                                                                  |  |  |  |  |  |  |  |

| PD        | 28                     | Ι   | Power down. Device resets and powers down when this signal is high.                                                                                                            |  |  |  |  |  |  |  |

| REFIN     | 8                      | I   | Reference (positive) input. REFIN must be decoupled with REFM pin using $0.1$ - $\mu$ F bypass capacitor and $1$ - $\mu$ F storage capacitor.                                  |  |  |  |  |  |  |  |

| REFM      | 7                      | I   | Reference ground. To be connected to analog ground plane.                                                                                                                      |  |  |  |  |  |  |  |

| REFOUT    | 9                      | 0   | Internal reference output. Shorted to REFIN pin only when internal reference is used.                                                                                          |  |  |  |  |  |  |  |

| SB/2C     | 1                      | I   | Straight binary or 2's complement output data format. When low the device output is straight binary format; when high the device output is 2's complement format. See Table 1. |  |  |  |  |  |  |  |

| SCLK      | 24                     | I   | Serial clock. Data is shifted onto SDO with the rising edge of this clock. This signal is qualified with $\overline{\text{CS}}$ internally.                                    |  |  |  |  |  |  |  |

| SDO       | 23                     | 0   | Serial data out. All bits except MSB are shifted out at the rising edge of SCLK.                                                                                               |  |  |  |  |  |  |  |

| +VA       | 3, 6, 14,<br>16, 17    | _   | Analog power supplies                                                                                                                                                          |  |  |  |  |  |  |  |

| +VBD      | 20                     | -   | Digital power supply for all digital inputs and outputs.                                                                                                                       |  |  |  |  |  |  |  |

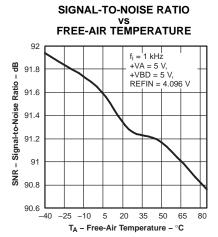

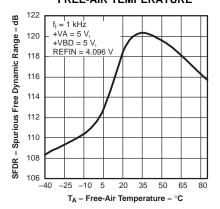

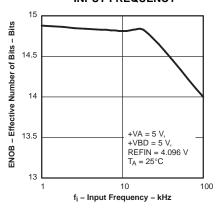

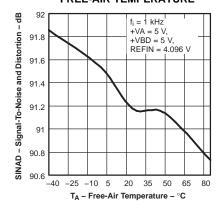

# **TYPICAL CHARACTERISTICS**

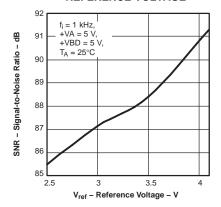

#### SIGNAL-TO-NOISE RATIO VS REFERENCE VOLTAGE

Figure 1.

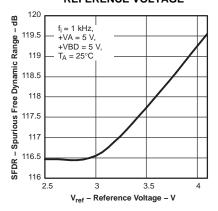

# SPURIOUS FREE DYNAMIC RANGE vs REFERENCE VOLTAGE

Figure 3.

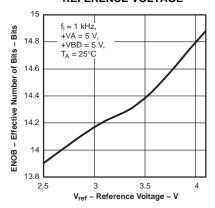

# EFFECTIVE NUMBER OF BITS VS REFERENCE VOLTAGE

Figure 5.

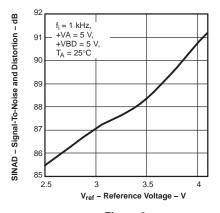

#### SIGNAL-TO-NOISE AND DISTORTION VS REFERENCE VOLTAGE

Figure 2.

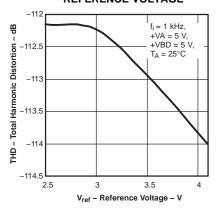

# TOTAL HARMONIC DISTORTION VS REFERENCE VOLTAGE

Figure 4.

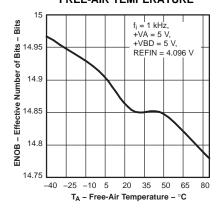

# EFFECTIVE NUMBER OF BITS VS FREE-AIR TEMPERATURE

Figure 6.

Figure 7.

# SPURIOUS FREE DYNAMIC RANGE vs FREE-AIR TEMPERATURE

Figure 9.

# EFFECTIVE NUMBER OF BITS VS INPUT FREQUENCY

Figure 11.

#### SIGNAL-TO-NOISE AND DISTORTION VS FREE-AIR TEMPERATURE

Figure 8.

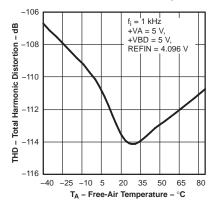

# TOTAL HARMONIC DISTORTION vs FREE-AIR TEMPERATURE

Figure 10.

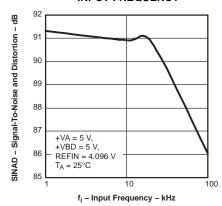

#### SIGNAL-TO-NOISE AND DISTORTION VS INPUT FREQUENCY

Figure 12.

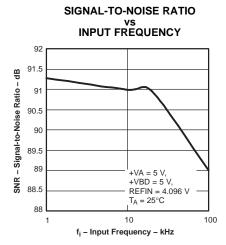

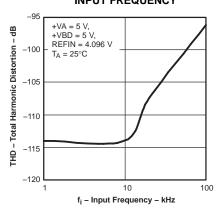

Figure 13.

Figure 14.

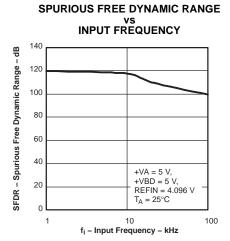

# TOTAL HARMONIC DISTORTION vs INPUT FREQUENCY

Figure 15.

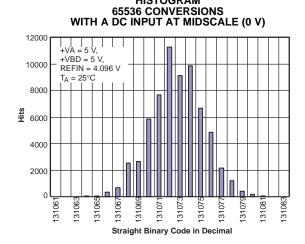

**HISTOGRAM**

Figure 16.

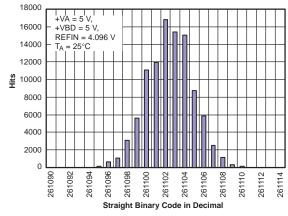

#### HISTOGRAM 100000 CONVERSIONS WITH A DC INPUT CLOSE TO FULL SCALE (4 V)

Figure 17.

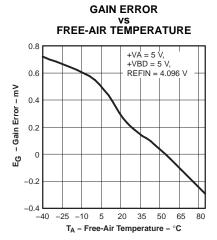

Figure 18.

Figure 20.

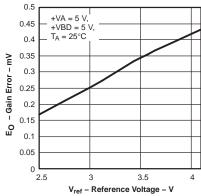

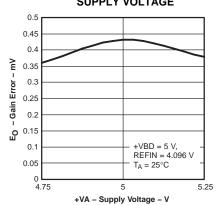

**OFFSET ERROR**

Figure 22.

Figure 19.

Figure 21.

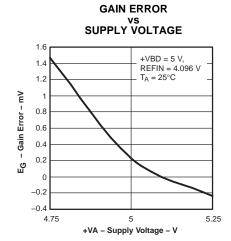

# OFFSET ERROR VS SUPPLY VOLTAGE

Figure 23.

Figure 24.

Figure 26.

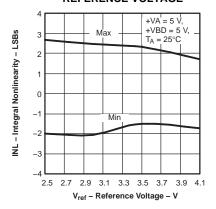

# INTEGRAL NONLINEARITY vs REFERENCE VOLTAGE

Figure 28.

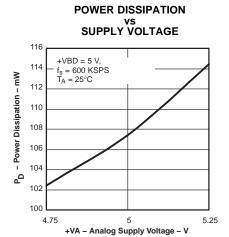

# POWER DISSIPATION VS SAMPLE RATE 140 Normal Mode Current 100 80 NAP Mode Current 40 +VA = 5 .25 V, +VBD = 5.25 V, TA = 25°C

200

0

Figure 25.

300 400

f<sub>s</sub> - Sample Rate - KSPS

500

600

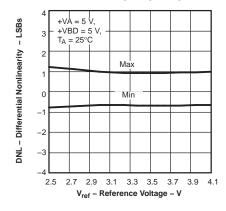

# DIFFERENTIAL NONLINEARITY vs REFERENCE VOLTAGE

Figure 27.

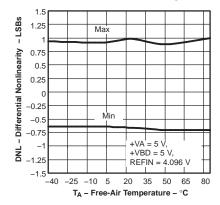

# DIFFERENTIAL NONLINEARITY vs FREE-AIR TEMPERATURE

Figure 29.

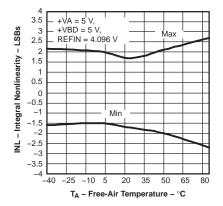

# INTEGRAL NONLINEARITY vs FREE-AIR TEMPERATURE

Figure 30.

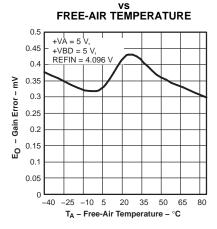

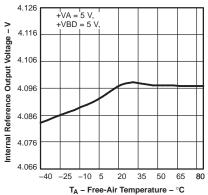

# vs FREE-AIR TEMPERATURE

INTERNAL VOLTAGE REFERENCE

Figure 31.

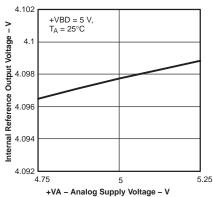

# INTERNAL VOLTAGE REFERENCE

vs SUPPLY VOLTAGE

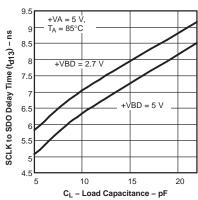

Figure 32. Figure 33.

Figure 34.

Straight Binary Code in Decimal

Figure 35.

Figure 36.

Figure 37.

A. EOC = End of conversion, SOC = Start of conversion,  $\overline{\text{CONVST\_QUAL}}$  is  $\overline{\text{CONVST}}$  latched by  $\overline{\text{CS}}$  = 0, see Figure 39.

Figure 38. Device States and Ideal Transitions

Figure 39. Relationship Between CONVST QUAL, CS, and CONVST

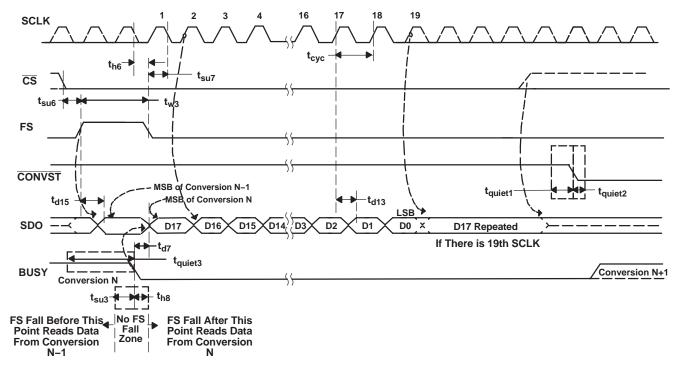

### **TIMING DIAGRAMS**

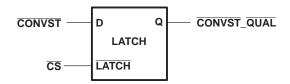

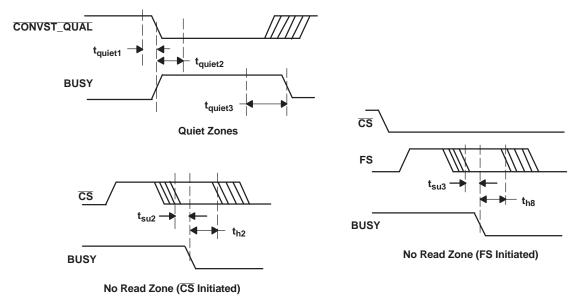

In the following descriptions, the signal CONVST\_QUAL represents CONVST latched by a low value on CS (see Figure 39).

To avoid performance degradation, there are three quiet zones to be observed ( $t_{quiet1}$  and  $t_{quiet2}$  are zones before and after the falling edge of  $\overline{CONVST\_QUAL}$  while  $t_{quiet3}$  is a time zone before the falling edge of BUSY) where there should be no I/O activities. Interface control signals, including the serial clock should remain steady. Typical degradation in performance if these quiet zones are not observed is depicted in the specifications section.

To avoid data loss a read operation should not start around the BUSY falling edge. This is constrained by  $t_{su2}$ ,  $t_{su3}$ ,  $t_{h2}$ , and  $t_{h8}$ .

Figure 40. Quiet Zones and No-Read Zones

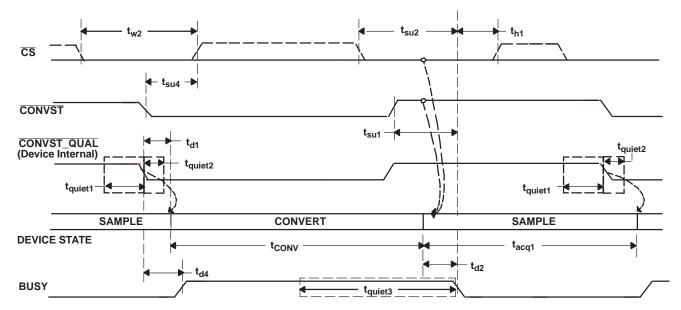

### **CONVERSION AND SAMPLING**

1. Convert start command:

The device enters the conversion phase from the sampling phase when a falling edge is detected on CONVST\_QUAL. This is shown in Figure 41, Figure 42, and Figure 43.

2. Sample (acquisition) start command:

The device starts sampling from the wait state or at the end of a conversion if  $\overline{\text{CONVST\_QUAL}}$  is detected as high and  $\overline{\text{CS}}$  as low. This is shown in Figure 41, Figure 42, and Figure 43.

Maintaining this condition when the device has just finished a conversion (as shown in Figure 41) takes the device immediately into the sampling phase after the conversion phase (back-to-back conversion) and hence achieves maximum throughput. Otherwise, the device enters the wait state.

Figure 41. Back-To-Back Conversion and Sample

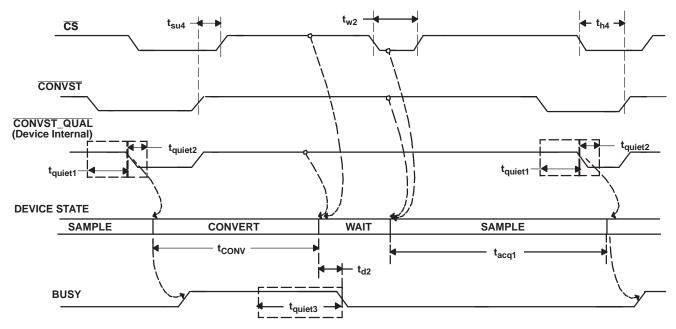

### 3. Wait/Nap entry stimulus:

The device enters the wait phase at the end of the conversion if the sample start command is not given. This is shown in Figure 42.

Figure 42. Convert and Sample with Wait

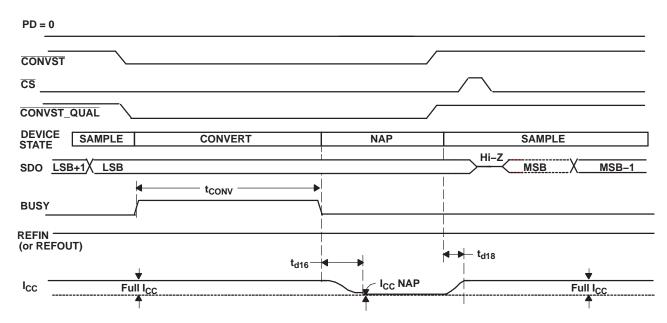

If lower power dissipation is desired and throughput can be compromised, a nap state can be inserted in between cycles (as shown in Figure 43). The device enters a low power (3 mA) state called nap if the end of the conversion happens when  $\overline{CONVST\_QUAL}$  is low. The cost for using this special wait state is a longer sampling time ( $t_{acq2}$ ) plus the nap time.

Figure 43. Convert and Sample with Nap

#### 4. Conversion abort command

An ongoing conversion can be abo<u>rted by using the conversion abort command.</u> This is done by forcing another start of conversion (a valid CONVST\_QUAL falling edge) onto an ongoing conversion as shown in Figure 44. The device enters the wait state after an aborted conversion. If the previous conversion was successfully aborted, the device output reads 0x3FC00 on SDO.

Figure 44. Conversion Abort

### **DATA READ OPERATION**

Data read control is independent of conversion control. Data can be read either during conversion or during sampling. Data that is read during a conversion involves latency of one sample. The start of a new data frame around the fall of BUSY is constrained by  $t_{su2}$ ,  $t_{su3}$ ,  $t_{h2}$ , and  $t_{h8}$ .

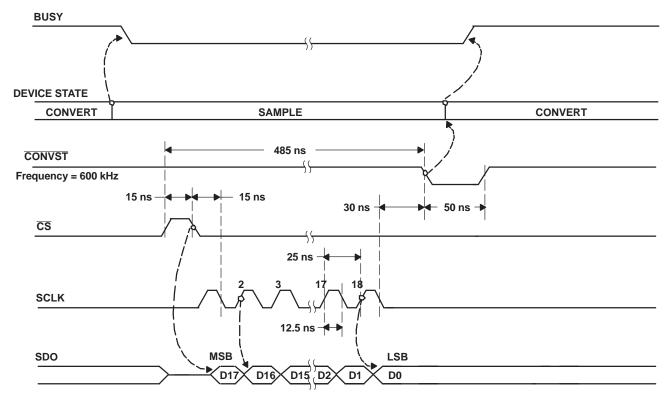

# 1. SPI Interface:

A data read operation in SPI interface mode is shown in Figure 45. FS must be tied high for operating in this mode. The MSB of the output data is available at the falling edge of  $\overline{CS}$ . MSB – 1 is shifted out at the first rising edge after the first falling edge of SCLK after  $\overline{CS}$  falling edge. Subsequent bits are shifted at the subsequent rising edges of SCLK. If another data frame is attempted (by pulling  $\overline{CS}$  high and subsequently low) during an active data frame, then the ongoing frame is aborted and a new frame is started.

Figure 45. Read Frame Controlled via  $\overline{CS}$  (FS = 1)

If another data frame is attempted (by pulling  $\overline{\text{CS}}$  high and then low) during an active data frame, then the ongoing frame is aborted and a new frame is started.

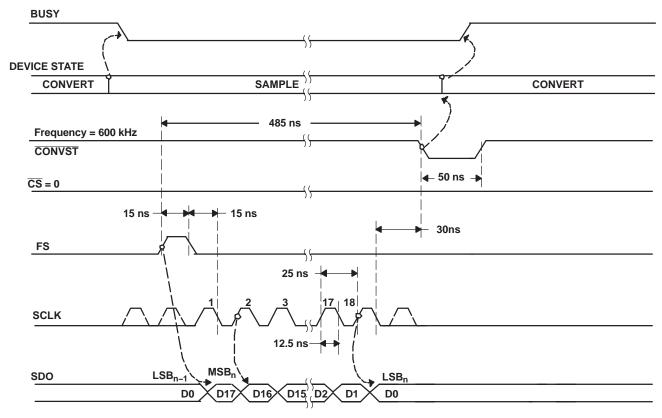

### 2. Serial interface using FS:

A data read operation in this mode is shown in Figure 46 and Figure 47. The MSB of the output data is available at the rising edge of FS. MSB – 1 is shifted out at the first rising edge after the first falling edge of SCLK after the FS falling edge. Subsequent bits are shifted at the subsequent rising edges of SCLK.

Figure 46. Read Frame Controlled via FS (FS is Low When BUSY Falls)

If FS is high when BUSY falls, the SDO is updated again with the new MSB when BUSY falls. This is shown in Figure 47.

Figure 47. Read Frame Controlled via FS (FS is High When BUSY Falls)

If another data frame is attempted by pulling up FS during an active data frame, then the ongoing frame is aborted and a new frame is started.

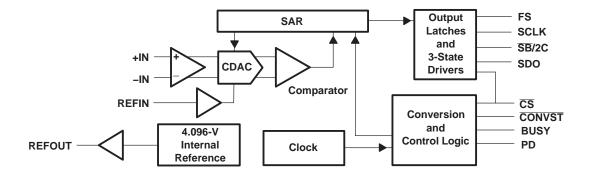

#### PRINCIPLES OF OPERATION

The ADS8380 is a high-speed successive approximation register (SAR) analog-to-digital converter (ADC). The architecture is based on charge redistribution, which inherently includes a sample/hold function.

The device includes a built-in conversion clock, internal reference, and 40-MHz SPI compatible serial interface. The maximum conversion time is 1.16 µs which is capable of sustaining a 600-kHz throughput.

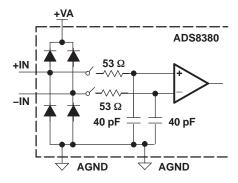

The analog input is provided to the two input pins: +IN and -IN. When a conversion is initiated, the differential input on these pins is sampled on the internal capacitor array. While a conversion is in progress, both inputs are disconnected from any internal function.

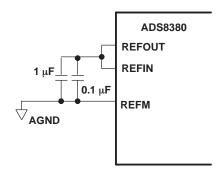

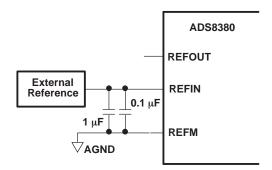

## **REFERENCE**

The ADS8380 has a built-in 4.096-V (nominal value) reference but can operate with an external reference also. When the internal reference is used, pin 9 (REFOUT) should be shorted to pin 8 (REFIN) and a 0.1- $\mu$ F decoupling capacitor and a 1- $\mu$ F storage capacitor must be connected between pin 8 (REFIN) and pin 7 (REFM) (see Figure 48). The internal reference of the converter is buffered.

# **PRINCIPLES OF OPERATION (continued)**

Figure 48. ADS8380 Using Internal Reference

The REFIN pin is also internally buffered. This eliminates the need to put a high bandwidth buffer on the board to drive the ADC reference and saves system area and power. When an external reference is used, the reference must be of low noise, which may be achieved by the addition of bypass capacitors from the REFIN pin to the REFM pin. See Figure 49 for operation of the ADS8380 with an external reference. REFM must be connected to the analog ground plane.

Figure 49. ADS8380 Using External Reference

Figure 50. Simplified Analog Input

# **ANALOG INPUT**

When the converter enters hold mode, the voltage difference between the +IN and -IN inputs is captured on the internal capacitor array. The +IN input has a range of -0.2 V to  $(+\text{V}_{REF} + 0.2 \text{ V})$ , whereas the -IN input has a range of -0.2 V to +0.2 V. The input span (+IN - (-IN)) is limited from 0 V to  $\text{V}_{REF}$ .

The input current on the analog inputs depends upon throughput and the frequency content of the analog input

### PRINCIPLES OF OPERATION (continued)

signals. Essentially, the current into the ADS8380 charges the internal capacitor array during the sampling (acquisition) time. After this capacitance has been fully charged, there is no further input current. The source of the analog input voltage must be able to charge the device sampling capacitance (40 pF each from +IN/-IN to AGND) to an 18-bit settling level within the sampling (acquisition) time of the device. When the converter goes into hold mode, the input resistance is greater than 1  $G\Omega$ .

Care must be taken regarding the absolute analog input voltage. To maintain the linearity of the converter, the +IN, -IN inputs and the span (+IN - (-IN)) should be within the limits specified. Outside of these ranges, the converter's linearity may not meet specifications.

Care should be taken to ensure that the output impedance of the sources driving +IN and -IN inputs are matched. If this is not observed, the two inputs can have different settling times. This can result in offset error, gain error, and linearity error which vary with temperature and input voltage.

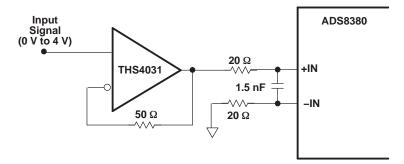

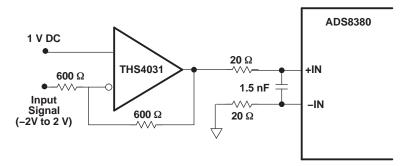

A typical input circuit using Tl's THS4031 is shown in Figure 52. In the figure, input from a bipolar source is converted to a unipolar signal for the ADS8380. In the case where the source signal is in range for the ADS8380, the circuit in Figure 51 may be used. Most of the specified performance figure were measured using the circuit in Figure 51.

Figure 51. Unipolar Input Drive Configuration

Figure 52. Bipolar Input Drive Configuration

### **DIGITAL INTERFACE**

### **TIMING AND CONTROL**

Conversion and sampling are controlled by the CONVST and CS pins. See the timing diagrams for detailed information on timing signals and their requirements. The ADS8380 uses an internally generated clock to control the conversion rate and in turn the throughput of the converter. SCLK is used for reading converted data only. A clean and low jitter conversion start command is important for the performance of the converter. There is a minimal quiet zone requirement around the conversion start command as mentioned in the timing requirements table.

3FFFF

20000

# **DIGITAL INTERFACE (continued)**

#### **READING DATA**

The ADS8380 offers a high speed serial interface that is compatible with the SPI protocol. The device outputs data in either 2's complement format or straight binary format depending on the state of the SB/2C pin. Refer to Table 1 for the ideal output codes.

**DESCRIPTION** ANALOG VALUE +IN - (-IN) **DIGITAL OUTPUT (HEXADECIMAL)** (+V<sub>REF</sub>)  $\overline{SB}/2C$  Pin = 0  $\overline{SB}/2c$  Pin = 1 Full-scale range Least significant bit  $(+V_{REF})/2^{18}$ (LSB) Full scale V<sub>REF</sub> - 1 LSB 3FFFF 1FFFF Mid scale (+V<sub>REF</sub>)/2 20000 00000

1FFFF

00000

Table 1. Input Voltages and Ideal Output Codes

To avoid performance degradation due to the toggling of device buffers, read operation must not be performed in the specified quiet zones ( $t_{quiet1}$ ,  $t_{quiet2}$ , and  $t_{quiet3}$ ). Internal to the device, the previously converted data is updated with the new data near the fall of BUSY. Hence, the fall of  $\overline{\text{CS}}$  and the fall of FS around the fall of BUSY is constrained. This is specified by  $t_{su2}$ ,  $t_{su3}$ ,  $t_{h2}$ , and  $t_{h8}$  in the timing requirements table.

(+V<sub>REF</sub>)/2 - 1 LSB

### **POWER SAVING**

Mid scale - 1 LSB

The converter provides two power saving modes, full power down and nap. Refer to Table 2 for information on activation/deactivation and resumption time for both modes.

| TYPE OF POWER DOWN                                      | SDO                                | POWER CONSUMPTION | ACTIVATED BY               | ACTIVATION TIME (t <sub>d16</sub> ) | RESUME POWER BY      |

|---------------------------------------------------------|------------------------------------|-------------------|----------------------------|-------------------------------------|----------------------|

| Normal operation                                        | Not 3 stated                       | 22 mA             | NA                         | NA                                  | NA                   |

| Full power down (Int Ref, 1-µF capacitor on REFOUT pin) | 3 Stated (t <sub>d10</sub> timing) | 2 μΑ              | PD = 1                     | 10 µs                               | PD = 0               |

| Full power down (Ext Ref, 1-µF capacitor on REFOUT pin) | 3 Stated (t <sub>d10</sub> timing) | 2 μΑ              | PD = 1                     | 10 µs                               | PD = 0               |

| Nap power down                                          | Not 3 stated                       | 3 mA              | At EOC and CONVST_QUAL = 0 | 200 ns                              | Sample Start command |

Table 2. Power Save

# **FULL POWER-DOWN MODE**

Full power-down mode is activated by turning off the supply or by asserting PD to 1. See Figure 53 and Figure 54. The device can be resumed from full power down by either turning on the power supply or by de-asserting the PD pin. The first two conversions produce inaccurate results because during this period the device loads its trim values to ensure the specified accuracy.

If an internal reference is used (with a  $1-\mu F$  capacitor installed between the REFOUT and REFM pins), the total resume time ( $t_{d18}$ ) is 25 ms. After the first two conversions,  $t_{d17}$  (4 ms) is required for the trimmed internal reference voltage to settle to the specified accuracy. Only then the converted results match the specified accuracy.

Figure 53. Device Full Power Down/Resume (Internal Refernce Used)

Figure 54. Device Full Power Down/Resume (External Reference Used)

### **NAP MODE**

Nap mode is automatically inserted at the end of a conversion if  $\overline{\text{CONVST\_QUAL}}$  is held low at EOC. The device can be operated in nap mode at the end of every conversion for saving power at lower throughputs. Another way to use this mode is to convert multiple times and then enter nap mode. The minimum sampling time after a nap state is  $t_{\text{acq1}} + t_{\text{d18}} = t_{\text{acq2}}$ .

Figure 55. Device Nap Power Down/Resume

### **LAYOUT**

For optimum performance, care should be taken with the physical layout of the ADS8380 circuitry.

Since the ADS8380 offers single-supply operation, it is often used in close proximity with digital logic, microcontrollers, microprocessors, and digital signal processors. The more the digital logic in the design and the higher the switching speed, the greater the need for better layout and isolation of the critical analog signals from these switching digital signals.

The basic SAR architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections and digital inputs that occur just prior to the end of sampling and just prior to the latching of the analog comparator. Such glitches might originate from switching power supplies, nearby digital logic, or high power devices. Noise during the end of sampling and the latter half of the conversion must be kept to a minimum (the former half of the conversion is not very sensitive since the device uses a proprietary error correction algorithm to correct for the transient errors made here).

The degree of error in the digital output depends on the reference voltage, layout, and the exact timing and degree of the external event.

On average, the ADS8380 draws very little current from an external reference as the reference voltage is internally buffered. If the reference voltage is external, it must be ensured that the reference source can drive the bypass capacitor without oscillation. A  $0.1-\mu F$  bypass capacitor is recommended from pin 8 directly to pin 7 (REFM).

The AGND and BDGND pins should be connected to a clean ground point. In all cases, this should be the analog ground. Avoid connections that are too close to the grounding point of a microcontroller or digital signal processor. If required, run a ground trace directly from the converter to the power supply entry point. The ideal layout consists of an analog ground plane dedicated to the converter and associated analog circuitry.

As with the AGND connections, +VA should be connected to a +5-V power-supply plane or trace that is separate from the connection for digital logic until they are connected at the power entry point. Power to the ADS8380 should be clean and well bypassed. A 0.1- $\mu$ F ceramic bypass capacitor should be placed as close to the device as possible. See Table 3 for the placement of these capacitors. In addition, a 1- $\mu$ F capacitor is recommended. In some situations, additional bypassing may be required, such as a 100- $\mu$ F electrolytic capacitor or even a Pi filter made up of inductors and capacitors—all designed to essentially low-pass filter the +5-V supply, removing the high frequency noise.

**Table 3. Power Supply Decoupling Capacitor Placement**

| SUPPLY PINS                                                     | CONVERTER ANALOG SIDE          | CONVERTER DIGITAL<br>SIDE |

|-----------------------------------------------------------------|--------------------------------|---------------------------|

| Pair of pins requiring a shortest path to decoupling capacitors | (2,3); (5,6); (15,16); (17,18) | (20,21)                   |

| Pins requiring no decoupling                                    | 4, 14, 19                      |                           |

When using the internal reference, ensure a shortest path from REFOUT (pin 9) to REFIN (pin 8) with the bypass capacitor directly between pins 8 and 7.

# **APPLICATION INFORMATION**

# **EXAMPLE DIGITAL STIMULUS**

The use of the ADS8380 is very straightforward. The following timing diagram shows one example of how to achieve a 600-KSPS throughput using a SPI compatible serial interface.

Figure 56. Example Stimulus in SPI Mode (FS =1), Back-To-Back Conversion that Achieves 600 KSPS

# **APPLICATION INFORMATION (continued)**

It is also possible to use the frame sync signal, FS. The following timing diagram shows how to achieve a 600-KSPS throughput using a modified serial interface with FS active.

Figure 57. Example Stimulus in Serial Interface With FS Active, Back-To-Back Conversion that Achieves 600 KSPS

www.ti.com 7-Oct-2021

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| ADS8380IBRHPT    | ACTIVE | VQFN         | RHP                | 28   | 250            | RoHS & Green | Call TI                       | Level-2-260C-1 YEAR | -40 to 85    | ADS8380I<br>B           | Samples |

| ADS8380IBRHPTG4  | ACTIVE | VQFN         | RHP                | 28   | 250            | RoHS & Green | Call TI                       | Level-2-260C-1 YEAR | -40 to 85    | AD\$8380I<br>B          | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 7-Oct-2021

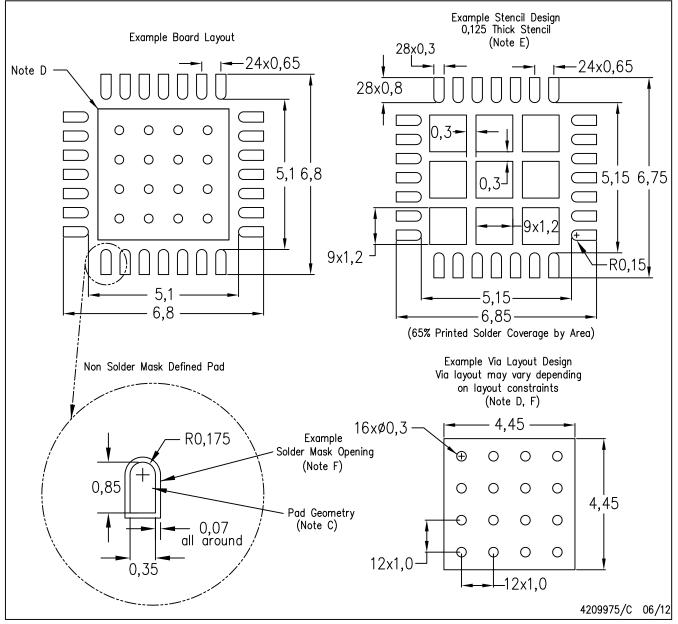

NOTES: All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994. This drawing is subject to change without notice. QFN (Quad Flatpack No—Lead) Package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

# RHP (S-PVQFN-N28)

PLASTIC QUAD FLATPACK NO-LEAD

# THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4206484/F 06/12

NOTE: All linear dimensions are in millimeters

RHP (S-PVQFN-N28)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated