## VMIVME-5565 Specifications

www DataSheet4I I com

## Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

## Features:

- High speed, easy to use fiber-optic network (2.12 Gbaud serially)

- Data written to memory in one node is also written to memory in all nodes on the network

- Up to 256 nodes

- Connection with multimode fiber up to 300m, single mode fiber up to 10km

- Dynamic packet size, 4 to 64 bytes of data

- Network transfer rate 43 Mbyte/s (4 byte packets) to 174 Mbyte/s (64 byte packets)

- VMEbus transfer rate 40 Mbyte/s

- 64 Mbyte or 128 Mbyte SDRAM Reflective Memory

- Two independent DMA channels

- Any node on the network can generate an interrupt in any other node on the network or in all network nodes with a single command

- Error detection

- Redundant transfer mode for extra error suppression

- No processor overhead

- No processor involvement in the operation of the network

- VMISFT-RFM2G network and shared memory driver included

- Operating system support for Windows NT®, Windows® 2000, VxWorks®, and Linux®

# Ordering Options May 13, 2005 800-005565-000 E A B C D E F VMIVME-5565 1 0 0 0

#### A = Memory Options

0 = 64 Mbute

1 = 128 Mbyte

#### B = FIFOs

0 = Reserved

1 = 4 K FIFOs

#### C = Transmission Mode

0 = Multimode

1 = Single Mode

DEF = 0 (Options reserved for future use)

## **Simplex Cable Specifications**

Fiber-Optic Cable - Multimode; (62.5 Micron core)

| Fiber-Optic Cable Assemblies | _ | Α | В | С | D | Ε | F |

|------------------------------|---|---|---|---|---|---|---|

| VMICBL-000-F5                | - | 0 |   |   | 0 | 0 | 0 |

## www.Da ABC = Cable Lengths

000 = .5 ft (0.15 m)011 = 350 ft (106.68m) 001 = 1 ft (.31m)012 = 500 ft (152.15m) 002 = 5 ft (1.52 m)013 = 574 ft (175 m)003 = 10 ft (3.04m)014 = 656 ft (200m) 004 = 25 ft (7.62m) 015 = 820 ft (250m) 005 = 50 ft (15.24 m)016 = 1.000 ft (304.30 m)006 = 80 ft (24.40 m)017 = 1,148 ft (350m) 007 = 100 ft (30.49 m)018 = 1,312 ft (400m) 008 = 150 ft (45.72 m)019 = 1,500 ft (456.45m) 009 = 200 ft (60.98 m)020 = 1,640 ft (500m) 010 = 250 ft (76.20m)

#### DEF = 0 (Options reserved for future use)

For Ordering Information, Call: 1-800-322-3616 or 1-256-880-0444 • FAX (256) 882-0859 Email: info.embeddedsystems@gefanuc.com Web Address: www.gefanuc.com/embedded

Copyright © 2005 by GE Fanuc Embedded Systems Specifications subject to change without notice.

## **Functional Characteristics**

Introduction: VMIVME-5565 is the VMEbus member of the GE Fanuc Embedded Systems VMIxxx-5565 family of Reflective Memory real-time network products. The other members of the family are VMIVME-5565, PCI mezzanine card (PMC), and VMIPCI-5565, the PCI-compatible board. All three of these products are network compatible, and may be integrated into a network in any combination. This family of products allows computers, workstations, PLCs, and other embedded controllers with dissimilar operating systems, or no operating system at all, to share data in real time.

To the local node, the Reflective Memory board appears as shared memory. Data can be written to or read from the memory by any level of software, including the application itself. Data written to the Reflective Memory in one node is transported by the network hardware to all other nodes, and placed in the same address on those node's Reflective Memory boards. This transport of data is accomplished without the

involvement of the processors on any node. Using this system, all nodes on the network have a local copy of shared data available for immediate access.

**Product Overview:** The Reflective Memory concept provides a very fast and efficient way of sharing data across distributed computer systems.

GE Fanuc Embedded Systems' VMIVME-5565 Reflective Memory interface allows data to be shared between up to 256 independent systems (nodes) at rates up to 174 Mbyte/s. Each Reflective Memory board can be configured with either 64 Mbyte or 128 Mbyte of onboard SDRAM. The local SDRAM provides fast Read access times to stored data. Writes are stored in local SDRAM and broadcast over a high speed fiberoptic data path to other Reflective Memory nodes. The transfer of data between nodes is software transparent, so no I/O overhead is required. Transmit and Receive FIFOs buffer data during peak data rates to optimize processor and bus performance to maintain high data throughput.

The Reflective Memory also allows interrupts to one or more nodes by writing to a byte register. These interrupt (four levels, each user definable) signals may be used to synchronize a system process, or used to follow any data. The interrupt always follows the data to ensure the reception of the data before the interrupt is acknowledged.

Each node on the system has a unique identification number between 0 and 255. The node number is established during hardware system integration by a series of onboard switches. This node number can be read by software by accessing an onboard register. In some applications, this node number would be useful in establishing the function of the node.

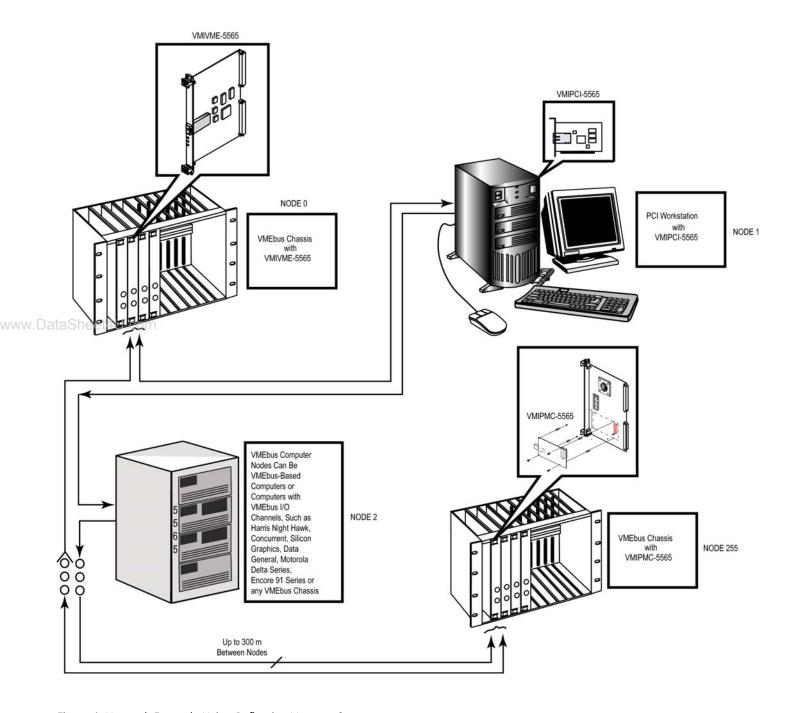

Link Arbitration: The VMIVME-5565 system is a fiber-optic daisy chain ring as shown in Figure 1. Each transfer is passed from node-to-node until it has gone all the way around the ring and reaches the originating node. Each node retransmits all transfers that it receives except those that it originated. Nodes are allowed to insert transfers between transfers passing through.

**Interrupt Transfers:** The VMIVME-5565 provides four network interrupts. Any processor can generate an interrupt on any other node on the network. In addition, any processor can generate an interrupt on all nodes on the network with a single register write.

In response to this interrupt register write, the sending VMIVME-5565 issues a special packet over the network, which contains the command strobe, the sender node ID, the destination node ID, and 32 bits of data. When a receiving node detects the proper combination of destination node ID and command strobe, it stores the sender note ID and the data in one of four 127 location-deep FIFOs. The four FIFOs correspond to the four interrupts. Upon storing this information in a FIFO, the receiving node issues an interrupt to the local processor if it has been software-enabled. The 32 bits of data stored in the FIFO is user-definable and typically is treated as an interrupt vector. As part of an interrupt service routine, the local processor reads this information out of the FIFO and acts accordingly.

VMEbus Initiator/DMA Capabilities: The VMIVME-5565 supports DMA operations. The DMA sequence is initialized by control register writes to the VMIVME-5565 by the host. Therefore, the VMIVME-5565 becomes a VMEbus initiator and moves the specified block of data up to 64 Mbyte without further host intervention. The architecture ensures that the VMIVME-5565 does not monopolize the VMEbus and causes the VMIVME-5565's DMA engine to automatically split large blocks in small bursts. The VMIVME-5565 can be programmed to issue a VMEbus interrupt upon completion of DMA process. There are two independent DMA engines, each capable of reading or writing. It is possible for a read DMA and a write DMA to occur simultaneously.

**Error Management:** Errors are detected by the VMIVME-5565 with the use of the error detection facilities of the Fiber Channel encoder/decoder and additional cyclic redundant encoding and checking. When a node detects an error, the erroneous transfer is removed from the system and an interrupt is generated, if enabled.

Protection Against Lost Data: The product is designed to prevent the FIFOs from becoming full and overflowing. It is important to note the only way that data can start to accumulate in FIFOs is for data to enter the node at a rate greater than the network data rate. Since data can enter from the fiber and from the VMEbus, it is possible to exceed these rates. If the transmit FIFO becomes almost full, a bit in the Status Register is set. This is an indication to the node's software that subsequent WRITEs to the Reflective Memory should be suspended until the FIFO is less than half-full. Once the transmit FIFO is almost full, writes to the Reflective Memory will be acknowledged with an interrupt. No data will be lost.

If the receive FIFO is allowed to become almost full, there is a danger the receiver FIFO can overflow resulting in data loss. In order to prevent this situation, the board will not respond to Read or Write commands which if occurs for a long period of time will cause the system controller to declare a time out.

Redundant Transfer Mode: The VMIVME-5565 can optionally be placed in the redundant transfer mode by the removal of a board jumper shunt. While in the redundant transfer mode, each packet sent on the network by the transmitter is sent twice, regardless of the dynamic packet size. The receiving circuitry of each node on the network evaluates each of the redundant transfers. If no errors are detected in the first transfer, it is used to update the onboard memory and the second transfer is discarded. If, however, the first transfer does contain an error, the second transfer is used to update the onboard memory provided it has no transmission error. In the remote chance that both redundant transfers contain an error, both transfer is used and the data is completely removed from the network.

The redundant transfer mode greatly reduces the chance that any data is dropped from the network. However, the redundant transfer mode also reduces the effective network transfer rates. The single Lword (4 byte) transfer rate drops to approximately 20 Mbyte/s. The 16 Lword (64 byte) transfer rate drops to the redundant rate of 87 Mbyte/s.

**Network Monitor:** There is a bit in the Status Register that can be used to verify that data is traversing the ring (that is, the ring is not broken). This can also be used to measure network latency.

VMISFT-RFM2G Network and Shared Memory Driver: The VMISFT-RFM2G network and shared memory driver provides an applications program with three convenient methods for exchanging data among hosts connected to the same RFM network:

- Programmed I/O (Peek and Poke): An applications program can treat the memory on the RFM device as ordinary memory in which the program can use ordinary load and store accesses.

- 2) Direct Memory Access (DMA): Systems where the performance penalty for individual bus accesses is unacceptably high, the driver utilizes the DMA feature available on some RFM devices in order to transfer data in variable-sized blocks. On UNIX systems, an applications program uses the familiar lseek(2)/read(2)/write(2) system calls to perform the data movement, while on other operating systems a GE Fanuc Embedded Systems-provided application program interface (API) is used for data movement.

- 3) **User Interrupts:** The VMIPCI-5565 provides three network interrupts. Any processor can generate an interrupt on any other node on the network. In addition, any processor can generate an interrupt on all nodes on the network with a single register write.

## **Technical Specifications**

Memory Size: 64 or 128 Mbyte

**Network Nonredundant Transfer Rate:** 43 Mbyte/s (single longword accesses) to 174 Mbyte/s (64 byte bursts)

**Network Redundant Transfer Rate:** 20 Mbyte/s (single longword accesses) to 87 Mbyte/s (64 byte bursts)

## Compatibility

VMEbus: This product complies with the VMEbus specification (ANSI/IEEE STD 1014-1987, IEC 821 and 297), with the following mnemonics:

A32:A24:D32/D16/D08 (EO): Slave: 39/3D:09/0D Form factor: 6U

## Cables

Multimode Fiber Cable: Small form factor (SFF) 850nm, 970 ft, multimode LC connector

Single Mode: Small form factor (SFF) 1,300nm, single mode, 10km or 6.21 miles

## Physical/Environmental Specifications

### **Power Requirements:**

+5VDC (±5 percent), 5.0A maximum

## Temperature:

Operating: 0 to  $+65^{\circ}$  C with forced air cooling

Storage: -40 to +85° C

Relative Humidity: 20% to 80%, noncondensing

MTBF: 163,995 hours (Bellcore)

## **Data Transfers**

Data written into the Reflective Memory is broadcast to all nodes on the network without further involvement of the sending or receiving nodes. Data is transferred from memory locations on the sending nodes to corresponding memory locations on the receiving nodes.

An illustration of a network example using Reflective Memory is shown in Figure 1.

## **Trademarks**

Windows and Windows NT are registered trademarks of Microsoft Corporation. Other registered trademarks are the property of their respective owners.

Figure 1. Network Example Using Reflective Memory System

#### GE Fanuc Embedded Systems Information Centers

Americas:

Huntsville, AL 1 800 322-3616 1 (256) 880-0444

Camarillo, CA 1 (805) 987-9300 Greenville, SC 1 (864) 627-8800

Europe, Middle East and Africa: Edinburgh, UK 44 (131) 561-3520 Paris, France 33 (1) 4324 6007

#### Additional Resources

For more information, please visit the GE Fanuc Embedded Systems web site at: www.gefanuc.com/embedded