### AY-1-1313

# **Priority Latching Network**

### **FEATURES**

- Low Power Consumption

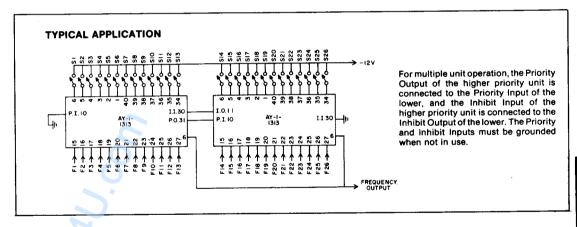

- Two or more units may be connected in tandem

### DESCRIPTION

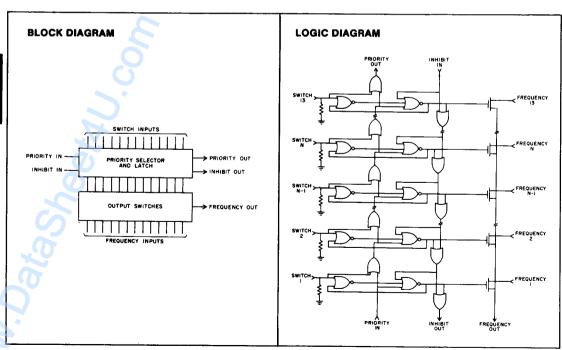

The AY-1-1313 Priority Latching Network is a LSI subsystem designed for use in electronic organ keyboard and pedal latching circuits. When any combination of one or more "switch" inputs is connected to logic "1" the output switch corresponding to the highest priority, or lowest number, input will close, connecting the selected frequency to the output frequency bus. The output switch will remain closed even if the input switch is released, and will remain closed until a new input switch closure occurs.

# ENTER: FAINMENT

# **ELECTRICAL CHARACTERISTICS**

### Maximum Ratings\*

All Pin Voltages with respect to VSS

-30V to +0.3V

Storage Temperature

-55° C to +150° C

Operating Temperature (TA)

-20° C to +70° C

## Standard Conditions (unless otherwise noted)

$V_{DD} = -12\pm1V$   $V_{GG} = -27\pm1.5V$  $V_{SS} = GND$  \*Exceeding these ratings could cause permanent damage. Functional operation of this device at these conditions is not implied—operating ranges are specified below.

| Characteristic                                | Min | Typ** | Max | Units | Conditions                                |

|-----------------------------------------------|-----|-------|-----|-------|-------------------------------------------|

| DC CHARACTERISTICS<br>Switch Inputs Impedance | 15  | _     | 80  | kΩ    | Measured to                               |

| Priority and Inhibit Inputs Impedance         | 1   | _     | _   | МΩ    | Ground                                    |

| Input Logic "0"                               | _   | -     | -2  | l v   |                                           |

| Input Logic "1"                               | -9  | -     | _   | l v   |                                           |

| Output Logic "0"                              | -   | -     | -2  | l v   | } R <sub>L</sub> = 47K to V <sub>DD</sub> |

| Output Logic "1"                              | -9  | _     | _   | V     | THE THE TOTAL                             |

| Frequency Output Switch                       |     |       |     |       |                                           |

| Impedance — "ON"                              | -   | -     | 20  | kΩ    |                                           |

| "OFF"                                         | 5   | -     |     | MΩ    |                                           |

| IDD Supply Current                            |     | _     | 8   | mA    | 1                                         |

| I <sub>GG</sub> Supply Current                | -   | _     | 1   | mA    |                                           |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.