Wired Communications

Edition 2000-07-14

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 16. 8. 00.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

QAP

Quad Analog POTS

PEB 3465 Version 1.2

Wired Communications

| PEB 346<br>PRELIMI<br>Revision |                                        | DS1    |  |

|--------------------------------|----------------------------------------|--------|--|

| Previous                       | Version:                               |        |  |

| Page                           | Subjects (major changes since last rev | ision) |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

|                                |                                        |        |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                          | Table of Contents                                                                                                                                                      |                      |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| 1<br>1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3        | General Description  Features  Pin Configuration (Top View)  Pin Definition and Functions  Functional Block Diagram  Application Diagrams                              | 9<br>10<br>11<br>15  |  |  |  |

| 2<br>2.1<br>2.1.1<br>2.1.2                        | Functional Description  Principles                                                                                                                                     | 19<br>19             |  |  |  |

| <b>3</b><br>3.1<br>3.2                            | Interfaces  MuPP/QAP Interface  QAP/AHV-SLIC Interface                                                                                                                 | 22                   |  |  |  |

| 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3 | Electrical Characteristics Absolute Maximum Ratings Operating Range Electrical Parameters Transmission Values DC Characteristics MuPP-Interface Timing Characteristics | 25<br>26<br>27<br>28 |  |  |  |

| 5                                                 | Package Outlines                                                                                                                                                       | 40                   |  |  |  |

| 6                                                 | Glossary                                                                                                                                                               | 41                   |  |  |  |

| List of Figu | ıres                                                              | Page |

|--------------|-------------------------------------------------------------------|------|

| Figure 1     | Application of an Analog Linecard for 16 Subscribers using MuSLIC | 28   |

| Figure 2     | Pin Configuration (Top View)                                      | 10   |

| Figure 3     | Functional Block Diagram                                          | 15   |

| Figure 4     | QAP with AHV-SLIC and MuPP μC (for one Subscriber)                | 16   |

| Figure 5     | QAP with AHV-SLIC and MuPP IOM-2 (for one Subscriber)             | 16   |

| Figure 6     | Signal Flow Graph: AC                                             | 19   |

| Figure 7     | Signal Flow Graph: DC                                             | 20   |

| Figure 8     | MuPP/QAP Interface: Frame, Bit Structure                          | 22   |

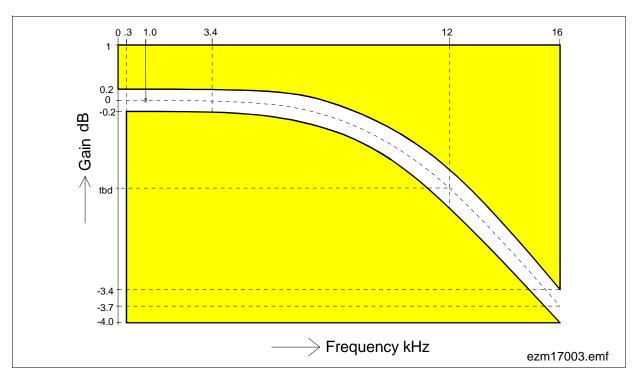

| Figure 9     | Transmission Characteristics                                      | 27   |

| Figure 10    | Frequency Response Transmit                                       | 29   |

| Figure 11    | Frequency Response Receive                                        | 29   |

| Figure 12    | Gain Tracking (Transmit and Receive)                              | 30   |

| Figure 13    | Total Distortion Receive                                          | 31   |

| Figure 14    | Total Distortion Transmit                                         | 32   |

| Figure 15    | DC-Feeding Test Circuit                                           | 34   |

| Figure 16    | Frequency Response Transmit                                       | 36   |

| Figure 17    | Frequency Response Receive                                        | 36   |

| Figure 18    | Frequency Response: Longitudinal Current Input & Auxiliary Inputs | s 38 |

| Figure 19    | MuPP-Interface Timing Characteristics                             | 39   |

| Figure 20    | Package Outline: PEB 3465 (QAP)                                   | 40   |

| List of Table | es                                                                | Page |

|---------------|-------------------------------------------------------------------|------|

| Table 1       | MuSLIC Chip Set ICs                                               | 8    |

| Table 2       | Pin Definition and Functions                                      | 11   |

| Table 3       | List of Components in Application Circuits (Figure 4 & Figure 5). | 17   |

| Table 4       | Total Distortion Receive                                          | 31   |

| Table 5       | Total Distortion Receive                                          | 32   |

# 1 General Description

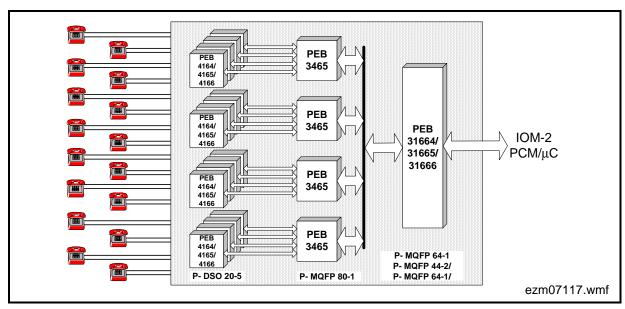

The highly integrated MuSLIC chip set supports to realize an extremely compact Analog Subscriber Line Interface Module. Only a few external components are required and there is no trimming or adjustment necessary to meet worldwide recommendations.

The chip set consists of three out of seven available ICs:

| Table 1                             | MuSLIC Chip So                                     | et ICs                                        |

|-------------------------------------|----------------------------------------------------|-----------------------------------------------|

| PEB 31664<br>PEB 31665<br>PEB 31666 | MuPP μC-S<br>MuPP IOM <sup>®</sup> -2<br>MuPP μC-E | Multichannel Processor for POTS               |

| PEB 3465                            | QAP                                                | Quad Analog POTS                              |

| PEB 4164<br>PEB 4165<br>PEB 4166    | AHV-SLIC-S<br>AHV-SLIC<br>AHV-SLIC-E               | Advanced High Voltage Subscriber Line Circuit |

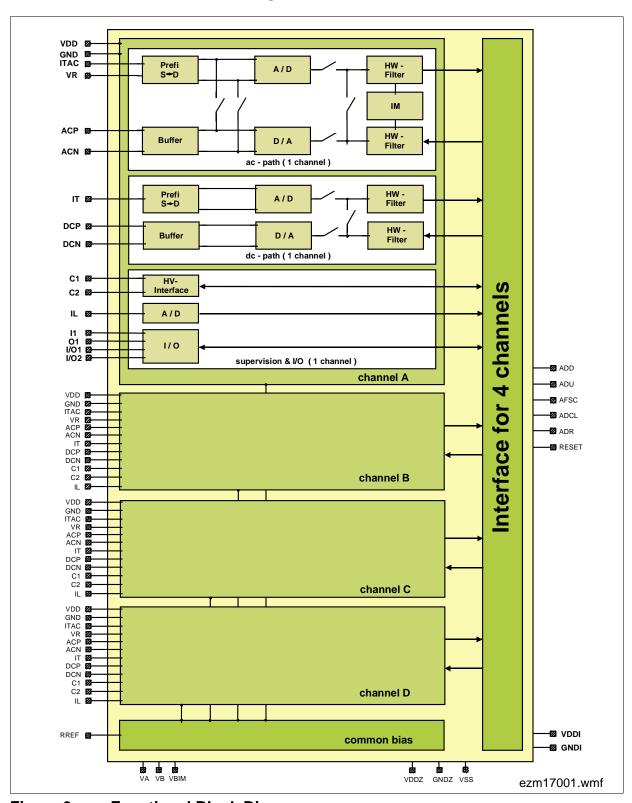

The Quad Analog POTS IC (QAP) PEB 3465 provides all analog frontend functions for four completely independent channels. Each channel is equipped with all necessary A/D- and D/A converters and filter functions for the AC and DC- path as well with a control and supervision interface to the AHV-SLIC, including digital I/O pins for channel specific control functions. Additionally the QAP provides analog input pins for measurement purposes.

Only four signals are needed for the highspeed serial interface to the MuPP IOM-2/MuPP  $\mu$ C ("MuPP"), which provides all signal processing and system interfacing for 16 channels.

Figure 1 Application of an Analog Linecard for 16 Subscribers using MuSLIC

# Quad Analog POTS QAP

**PEB 3465**

#### Version 1.2

### 1.1 Features

- Four channel analog frontend for POTS

- · Only a few external components are required

- No trimming or adjustments are required

- Advanced low power BiCMOS<sup>1)</sup> technology

- High performance AD and DA conversion

- · Four pin serial interface

- Three operating modes: Power Down, Active and Ringing

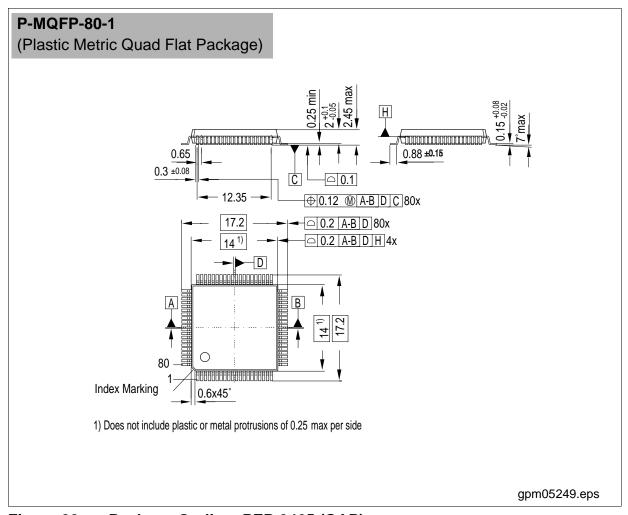

- Standard SMD P-MQFP-80-1 package

<sup>1)</sup> Abbreviations see Page 41

| Туре     | Package     |

|----------|-------------|

| PEB 3465 | P-MQFP-80-1 |

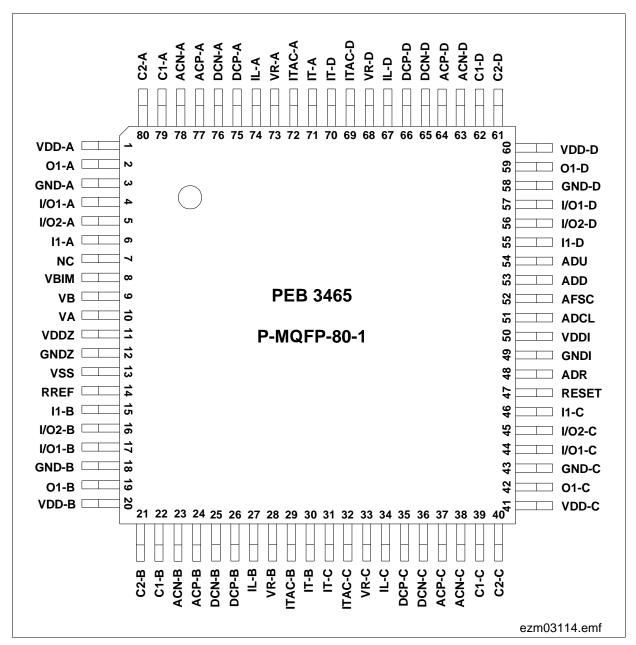

# 1.2 Pin Configuration (Top View)

Figure 2 Pin Configuration (Top View)

### 1.2.1 Pin Definition and Functions

The following tables group the pins according to their functions. They include pin number, pin name, type, a brief description of the function, and cross-references referring to the sections in which the pin functions are discussed.

Table 2 Pin Definition and Functions

| I able Z | Fill Delinition and Functions |      |                                         |

|----------|-------------------------------|------|-----------------------------------------|

| Pin No.  | Name                          | Туре | Function                                |

| Power Su | upply Pins                    |      |                                         |

| 1        | VDD-A                         | _    | + 5 V analog supply voltage (channel A) |

| 20       | VDD-B                         | _    | + 5 V analog supply voltage (channel B) |

| 41       | VDD-C                         | _    | + 5 V analog supply voltage (channel C) |

| 60       | VDD-D                         | _    | + 5 V analog supply voltage (channel D) |

| 3        | GND-A                         | _    | Analog ground (channel A)               |

| 18       | GND-B                         | _    | Analog ground (channel B)               |

| 43       | GND-C                         | _    | Analog ground (channel C)               |

| 58       | GND-D                         | _    | Analog ground (channel D)               |

| 11       | VDDZ                          | _    | + 5 V analog supply voltage (bias)      |

| 12       | GNDZ                          | _    | Analog ground (bias)                    |

| 13       | VSS                           | _    | – 5 V analog supply voltage             |

| 50       | VDDI                          | _    | + 3.3 V or + 5 V digital supply voltage |

# **Interface Pins to MuPP**

**GNDI**

49

| 54 | ADU   | 0 | Analog data upstream          |

|----|-------|---|-------------------------------|

| 53 | ADD   | I | Analog data downstream        |

| 51 | ADCL  | I | Analog data-clock             |

| 52 | AFSC  | I | Analog frame-sync.            |

| 48 | ADR   | I | Select odd or even port nr.   |

| 47 | RESET | I | Interface-reset (active high) |

Digital ground

| Table 2 Pin Definition and Functions (Contin |

|----------------------------------------------|

|----------------------------------------------|

| Pin No. Name Type Function |

|----------------------------|

|----------------------------|

# **Interface to AHV-SLIC**

| 71 | IT-A   | I   | Transversal current input (AC+DC), channel A |

|----|--------|-----|----------------------------------------------|

| 72 | ITAC-A | I   | Transversal current input (AC), channel A    |

| 73 | VR-A   | I   | Reference input, channel A                   |

| 74 | IL-A   | I   | Longitudinal current input, channel A        |

| 77 | ACP-A  | 0   | Two wire output voltage (ACP), channel A     |

| 78 | ACN-A  | 0   | Two wire output voltage (ACN), channel A     |

| 75 | DCP-A  | 0   | Two wire output voltage (DCP), channel A     |

| 76 | DCN-A  | 0   | Two wire output voltage (DCN), channel A     |

| 79 | C1-A   | I/O | Digital interface to AHV-SLIC, channel A     |

| 80 | C2-A   | 0   | Digital interface to AHV-SLIC, channel A     |

| 30 | IT-B   | I   | Transversal current input (AC+DC), channel B |

| 29 | ITAC-B | I   | Transversal current input (AC), channel B    |

| 28 | VR-B   | I   | Reference input, channel B                   |

| 27 | IL-B   | I   | Longitudinal current input, channel B        |

| 24 | ACP-B  | 0   | Two wire output voltage (ACP), channel B     |

| 23 | ACN-B  | 0   | Two wire output voltage (ACN), channel B     |

| 26 | DCP-B  | 0   | Two wire output voltage (DCP), channel B     |

| 25 | DCN-B  | 0   | Two wire output voltage (DCN), channel B     |

| 22 | C1-B   | I/O | Digital interface to AHV-SLIC, channel B     |

| 21 | C2-B   | 0   | Digital interface to AHV-SLIC, channel B     |

| 31 | IT-C   | I   | Transversal current input (AC+DC), channel C |

| 32 | ITAC-C | I   | Transversal current input (AC), channel C    |

| 33 | VR-C   | I   | Reference input, channel C                   |

| 34 | IL-C   | I   | Longitudinal current input, channel C        |

| 37 | ACP-C  | 0   | Two wire output voltage (ACP), channel C     |

| 38 | ACN-C  | 0   | Two wire output voltage (ACN), channel C     |

| 35 | DCP-C  | 0   | Two wire output voltage (DCP), channel C     |

| 36 | DCN-C  | 0   | Two wire output voltage (DCN), channel C     |

Table 2

Pin Definition and Functions (Continued)

| Name   | Туре                                                         | Function                                     |

|--------|--------------------------------------------------------------|----------------------------------------------|

| C1-C   | I/O                                                          | Digital interface to AHV-SLIC, channel C     |

| C2-C   | 0                                                            | Digital interface to AHV-SLIC, channel C     |

| IT-D   | I                                                            | Transversal current input (AC+DC), channel D |

| ITAC-D | I                                                            | Transversal current input (AC), channel D    |

| VR-D   | I                                                            | Reference input, channel D                   |

| IL-D   | I                                                            | Longitudinal current input, channel D        |

| ACP-D  | 0                                                            | Two wire output voltage (ACP), channel D     |

| ACN-D  | 0                                                            | Two wire output voltage (ACN), channel D     |

| DCP-D  | 0                                                            | Two wire output voltage (DCP), channel D     |

| DCN-D  | 0                                                            | Two wire output voltage (DCN), channel D     |

| C1-D   | I/O                                                          | Digital interface to AHV-SLIC, channel D     |

| C2-D   | 0                                                            | Digital interface to AHV-SLIC, channel D     |

|        | C1-C C2-C IT-D ITAC-D VR-D IL-D ACP-D ACN-D DCP-D DCN-D C1-D | C1-C                                         |

|  | Table 2 | Pin Definition and Functions (Co | intinued) |

|--|---------|----------------------------------|-----------|

|--|---------|----------------------------------|-----------|

| Pin No. | Name | Type | Function |

|---------|------|------|----------|

|---------|------|------|----------|

# IO Pins<sup>1)</sup>

| 4  | IO1-A               | I/O | User-programmable I/O pin, channel A |

|----|---------------------|-----|--------------------------------------|

| 5  | IO2-A <sup>2)</sup> | I/O | User-programmable I/O pin, channel A |

| 6  | I1-A                | I   | Fixed input pin, channel A           |

| 2  | O1-A                | 0   | Fixed output pin, channel A          |

| 17 | IO1-B               | I/O | User-programmable I/O pin, channel B |

| 16 | IO2-B <sup>2)</sup> | I/O | User-programmable I/O pin, channel B |

| 15 | I1-B                | I   | Fixed input pin, channel B           |

| 19 | O1-B                | 0   | Fixed output pin, channel B          |

| 44 | IO1-C               | I/O | User-programmable I/O pin, channel C |

| 45 | IO2-C <sup>2)</sup> | I/O | User-programmable I/O pin, channel C |

| 46 | I1-C                | I   | Fixed input pin, channel C           |

| 42 | O1-C                | О   | Fixed output pin, channel C          |

| 57 | IO1-D               | I/O | User-programmable I/O pin, channel D |

| 56 | IO2-D <sup>2)</sup> | I/O | User-programmable I/O pin, channel D |

| 55 | I1-D                | I   | Fixed input pin, channel D           |

| 59 | O1-D                | 0   | Fixed output pin, channel D          |

| -  | 1                   |     | '                                    |

### **Miscellaneous Function Pins**

| 14 | RREF | 0 | Test pin, do not connect  |  |  |  |  |  |

|----|------|---|---------------------------|--|--|--|--|--|

| 10 | VA   | I | Voltage sense A           |  |  |  |  |  |

| 9  | VB   | I | Voltage sense B           |  |  |  |  |  |

| 8  | VBIM | I | Battery image sense input |  |  |  |  |  |

### **Pins not Used**

|   | N 0  |   |                          |

|---|------|---|--------------------------|

| 1 | N.C. | _ | Not connected (not used) |

Unused fixed input pin should be terminatedd with pull up or pull down. Unused programmable pins should be programmed to output.

Data Sheet 14 2000-07-14

<sup>&</sup>lt;sup>2)</sup> If the PEB3465 is used together with the AHV-SLICs PEB4164 or PEB4166 it is recommended to use the IO2-Pin to drive the C3-Pin of the SLIC.

# 1.2.2 Functional Block Diagram

Figure 3 Functional Block Diagram

# 1.2.3 Application Diagrams

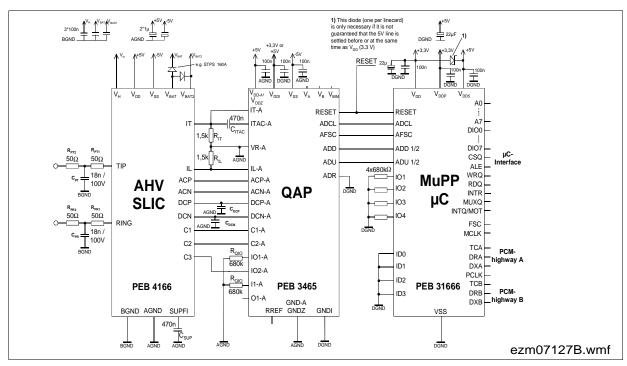

Figure 4 QAP with AHV-SLIC and MuPP μC (for one Subscriber)

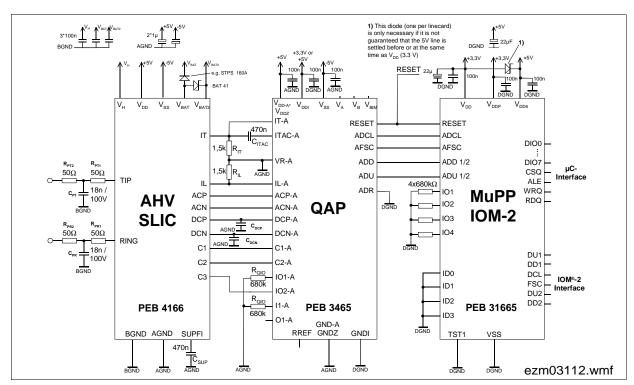

Figure 5 QAP with AHV-SLIC and MuPP IOM-2 (for one Subscriber)

Table 3 List of Components in Application Circuits (Figure 4 & Figure 5)

| Symbol                                                                                                 |      | Value | Unit | Tolerance |       |

|--------------------------------------------------------------------------------------------------------|------|-------|------|-----------|-------|

|                                                                                                        | min. | typ.  | max. |           |       |

| R <sub>PT1</sub> <sup>1)</sup> R <sub>PT2</sub> <sup>2)</sup>                                          | 30   | 50    |      | Ω         | 0,1 % |

| R <sub>PT2</sub> <sup>2)</sup>                                                                         | 0    | 50    |      | Ω         | 0,1 % |

| R <sub>PR1</sub>                                                                                       | 30   | 50    |      | Ω         | 0,1 % |

| R <sub>PR2</sub>                                                                                       | 0    | 50    |      | Ω         | 0,1 % |

| R <sub>IT</sub>                                                                                        |      | 1,5   |      | kΩ        | 1 %   |

| R <sub>IL</sub>                                                                                        |      | 1,5   |      | kΩ        | 1 %   |

| R <sub>QIO</sub>                                                                                       |      | 680   |      | kΩ        | 5 %   |

| R <sub>MIO</sub>                                                                                       |      | 680   |      | kΩ        | 5 %   |

| C <sub>PT</sub>                                                                                        | 0,2  | 18    | 20   | nF        | 10 %  |

| C <sub>PR</sub>                                                                                        | 0,2  | 18    | 20   | nF        | 10 %  |

| C <sub>ITAC</sub>                                                                                      |      | 470   |      | nF        | 10 %  |

| C <sub>DCP/N</sub>                                                                                     |      | 100   |      | nF        | 10 %  |

| R <sub>MIO</sub> C <sub>PT</sub> C <sub>PR</sub> C <sub>ITAC</sub> C <sub>DCP/N</sub> C <sub>SUP</sub> |      | 470   |      | nF        | 10 %  |

<sup>1)</sup> Absolut value not critical, but matching with RPR1 is important

<sup>2)</sup> Absolut value not critical, but matching with RPR2 is important.

# 2 Functional Description

The Multichannel Signal Processing Subscriber Line Interface Codec Filter chip set, MuSLIC, is a logic continuation of the well established family of the Infineon Technologies PCM-Codec-Filter-ICs with the integration of all DC-feeding, supervision and meterpulse injection features on chip as well. Fabricated in advanced CMOS, BiCMOS and High Voltage technology SPT 170 the MuSLIC is tailored for very flexible solutions in analog/digital communication systems.

The chip set consists of the digital signal processor for 16 channels (MuPP, multichannel processor for POTS), the analog/digital and digital/analog converter for 4 channels (QAP, quad analog POTS) and the high voltage interface chip for 1 channel (AHV-SLIC, advanced high voltage subscriber line interface circuit).

The MuPP uses the benefits of a DSP not only for the voice channel but even for line feeding and supervision which leads to a very high flexibility without the need of external components. Based on an advanced digital filter concept, the PEB 31665/PEB 31666/PEB 31664 (MuPP) and the PEB 3465 (QAP) provide excellent transmission performance. The new filter concept leads to a maximum of independence between the different filter blocks. Each filter block can be seen as a one to one representative of the corresponding network element. Together with the software package MuSLICOS, filter optimizing to different applications can be done in a clear and straight forward procedure. The AC frequency behavior is mainly determined by the digital filters. Using the oversampling 1 bit  $\Sigma\Delta$ -AD/DA converters, linearity is only limited by second order parasitic effects.

The digital solution of line feeding offers free programmability of feeding current and voltage as well as very fast settling of the DC-operating point after transitions. A 0.3 Hz lowpass filter in the DC-loop is mainly responsible for the system stability.

Additionally Teletax generation and filtering is implemented as well as free programmable balanced ring generation with zero-crossing injection. Off hook detection with programmable thresholds is possible in all operating modes. To reduce overall power consumption of the linecard, the MuPP, the QAP and the AHV-SLICs provide a Power Down mode with off-hook detection (PDNR).

To program the MuSLIC or to get status information about the chip set or the system, two user interfaces are available: the IOM<sup>®</sup>-2 interface and a 8-bit-parallel simple microcontroller interface.

The AHV-SLICs PEB4165 and PEB4166 provide battery feeding between - 15 V and - 80 V and ringing injection with a differential ring voltage up to 85 Vrms. In order to achieve these high amplitudes, an auxiliary positive battery voltage is used during ringing. This voltage can also be applied to drive very long telephone lines.

The AHV-SLICs are designed for a voltage feeding - current sensing line interface concept and provide sensing of transversal and longitudinal currents on both wires. In

Power Down mode the AHV-SLIC is switched off turning the line outputs to a high impedance state. Off-hook supervision is provided by activating a line current sensor.

# 2.1 Principles

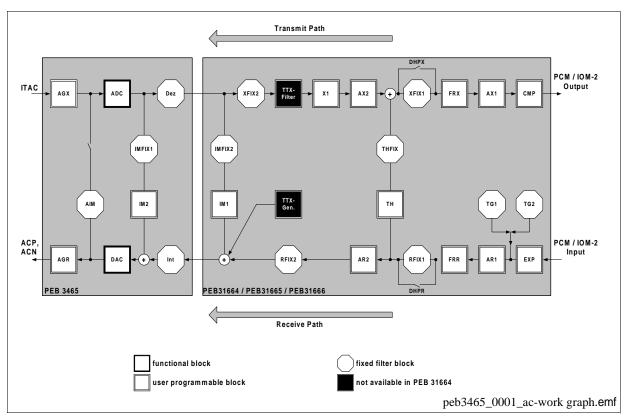

# 2.1.1 Signal Flow Graph: AC

Figure 6 Signal Flow Graph: AC

#### **Transmit Path**

The analog input signal has to be connected to pin ITAC of the QAP by an external capacitor (470 nF) for AC/DC separation. After passing a programmable gain stage (AGX = 0, 3.5 or 9.5 dB) and a simple antialiasing prefilter the voice signal is converted to a 1-bit digital data stream in the  $\Sigma\Delta$ -converter. The first down sampling steps are done in fast running digital hardware filters on the QAP. This down sampled AC-signal (64 kHz sampling rate) is sent to the MuPP via the MuPP/QAP-Interface in the ADU-channel. The following signal processing is done in the DSP-machine of the MuPP. The benefits are the programmability of frequency and the gain behavior. At the end the fully processed signal is transferred to the PCM / IOM-2 Interface (A-law /  $\mu$ -law / 16 bit linear) signal representation.

#### **Receive Path**

The digital input signal is received via the PCM / IOM-2 Interface of the MuPP. Expansion, PCM-lowpass-filtering, gain correction and frequency response correction are the next steps which are done by the DSP-machine. This 64 kHz AC signal is sent from the MuPP to the QAP via the MuPP/QAP-Interface in the ADD-channel. The up sampling interpolation steps are processed by fast hardware structures in the QAP to reduce the DSP-workload. The 1-bit data stream is then converted to an analog equivalent. A subsequent programmable gain stage (AGR = 0 or  $-3.5 \, \text{dB}$ ) and smoothing filter provides the AC output signal at the Pins ACP and ACN of the QAP for direct connection to the AHV-SLIC.

### Loops

There are two different loops implemented: The Impedance Matching (IM) loop which is divided into 3 separate loops to guarantee very high flexibility to various impedances, and the Transhybrid Balancing (TH) loop.

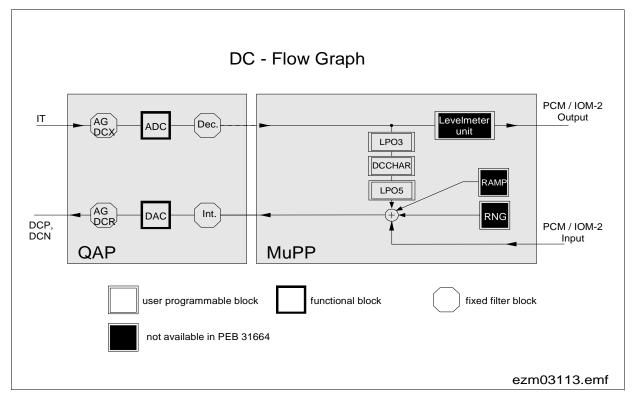

# 2.1.2 Signal Flow Graph: DC

Figure 7 Signal Flow Graph: DC

#### **DC Characteristic**

The incoming information (transmit direction) at pin IT (scaled transversal AC + DCcurrent, transferred to a voltage via an external 1.5 k $\Omega$  resistor at IT) passes first an antialiasing filter and is then converted to a 1-bit digital data stream in the  $\Sigma\Delta$ -converter. Down sampling is done in hardware filters of the QAP. This DC-information (2 kHz sampling rate) is then fed to the MuPP where it is first lowpass filtered (0.3 Hz corner frequency) for stability and noise reasons. The following DC-characteristic consists of three branches which represents different kinds of feeding behavior. In typical applications it acts as a programmable constant current source ( $R_{in} > 30 \text{ k}\Omega$ ). If the desired value cannot be held feeding switches automatically and smoothly to the resistive branch ( $R_{in}$  programmable between 0 ... 1.6 k $\Omega$ ). The third branch is used for feeding long lines - the DC-characteristic switches to a constant voltage behavior. For superimposing voice as well as Teletax pulses the necessary drop at the line can be calculated and taken into account as well. The outgoing bit stream (2 kHz sampling rate), representing the DC-feeding value is then sent back to the QAP where a 1-bit  $\Sigma\Delta$ converter and a following smoothing filter (using 2\*100 nF external capacitor) establish the desired values at the Pins DCP and DCN, respectively. Depending on the operating mode (Active, Ringing, Active with Boosted Battery) a gain of 0 or 4 dB is inserted.

For test purposes it is possible to close a loop to test either the analog part or the digital part of the DC path.

#### **Additional Features**

The QAP provides three general purpose input Pins (VA, VB, VBIM) for measuring. Via the MuPP/QAP-Interface it is possible to select one of these inputs for the measurement. The DC-signal at the selected input is converted to digital using the same  $\Sigma\Delta$ -converter as for Ground Key information (IL, accuracy of  $\pm 8\%$ ) and sent to the MuPP. The input range is between – 2.4 V ... + 2.4 V. As a further selection it is also possible to measure the internal VDDZ-voltage of the QAP. This voltage is internal divided by 4 and can be measured by setting VDDIM.

Data Sheet 21 2000-07-14

# 3 Interfaces

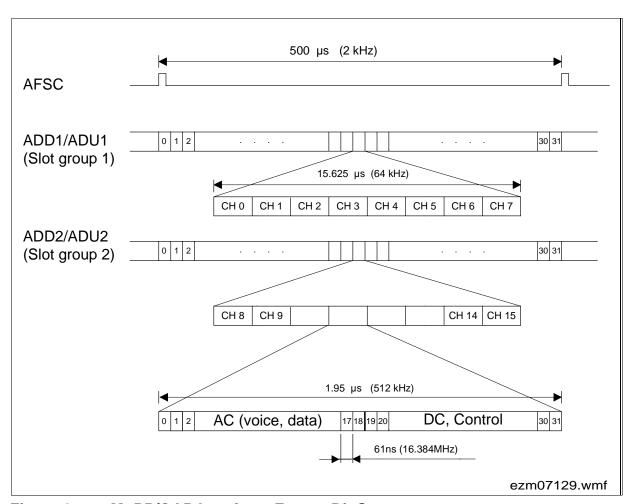

#### 3.1 MuPP/QAP Interface

The MuPP/QAP-Interface, the link between MuPP and QAP is a serial interface based on the 6 signals AFSC (analog frame sync), ADCL (analog data clock), ADU1/ADU2 (analog data upstream) and ADD1/ADD2 (analog data downstream). ADU1 and ADD1 are common to the first group of 8 time slots (channels) and ADU2 and ADD2 to the second 8 time slots (channels). AFSC and ADCL are common to both groups of time slots.

Figure 8 MuPP/QAP Interface: Frame, Bit Structure

### 3.2 QAP/AHV-SLIC Interface

### **Output Voltage AC (ACP, ACN)**

The output voltage at the pins ACP and ACN represents the AC-information together with Teletax information at the receive path. The AC-information is received via the MuPP/QAP-Interface in the ADD channel. The 64 kHz bitstream is converted to analog, passes a programmable gain stage of 0 / – 3.5 dB (TTX is also affected) and is buffered to drive a load of  $R_{\rm L}$  > 15 k $\Omega$  and  $C_{\rm L}$  < 20 pF, which is the input impedance of the AHV-SLIC.

### **Output Voltage DC (DCP, DCN)**

The output voltage at the pins DCP and DCN represents the DC-information together with the Ring Burst at the receive path. The DC-information is received via the MuPP/QAP-Interface in the ADD channel. The 2 kHz bitstream is converted to analog and buffered to drive external smoothing capacitors of 2\*100 nF. The pins are directly connected to the AHV-SLIC.

### **Transversal Current Sense AC - Input (ITAC)**

The pin ITAC is the input voltage pin for the AC transversal current information from the AHV-SLIC in the transmit path. AC/DC separation is done by an external highpass filter (ext. capacitor = 470 nF). The input resistance is larger than 20 k $\Omega$ . Current/voltage conversion is done via an external resistor of 1.5 k $\Omega$  (same for pin IT). The signal passes a programmable gain stage of 0, 3.5 or 9.5 dB, is converted to digital and sent to the MuPP via the MuPP/QAP-Interface in the ADU channel (64 kHz bitstream).

# Transversal Current Sense DC - Input (IT)

The pin IT is the input voltage pin for the DC transversal current information from the AHV-SLIC in the transmit path. The input resistance is larger than 500 k $\Omega$ . Current/voltage conversion is done via an external resistor of 1.5 k $\Omega$  (same for pin ITAC). The voltage at pin IT is lowpass filtered and converted to digital. The bitstream (2 kHz) is sent to the MuPP via the MuPP/QAP-Interface for further signal processing.

# **Longitudinal Current Sense - Input (IL)**

The scaled longitudinal current information transferred from the AHV-SLIC - the current/voltage conversion is done by an external resistor of 1.5 k $\Omega$  - is converted into digital and sent to the MuPP via the MuPP/QAP-Interface in the ADU channel.

# Ternary Interface (C1, C2)

In order to set the AHV-SLICs to the different operating modes, the mode information of the board-contoller is passed through from the IOM-2-channel (PEB 31665) or  $\mu$ C-

Data Sheet 23 2000-07-14

interface (PEB 31666, PEB 31664) via the MuPP/QAP-interface to the ternary AHV-SLIC interface pins C1 and C2.

# 4 Electrical Characteristics

# 4.1 Absolute Maximum Ratings

| Parameter                                      | Symbol    | Limit V     | /alues | Unit | <b>Test Condition</b> |

|------------------------------------------------|-----------|-------------|--------|------|-----------------------|

|                                                |           | min.        | max.   |      |                       |

| VDDA-VDDD referred to                          |           | - 0.3       | 7      | V    |                       |

| GNDA-GNDD                                      |           |             |        |      |                       |

| VDDI referred to GNDI                          |           | -0.3        | 7      | V    |                       |

| VSS referred to all GND pins                   |           | <b>-7</b>   | 0.3    | V    |                       |

| GNDA-GNDD to GNDI                              |           | - 0.3       | 0.3    | V    |                       |

| VDDA-VDDD to VDDI                              |           | - 0.3       | 0.3    | V    |                       |

| Analog input and output voltages               |           |             |        |      |                       |

| referred to VDD = 5 V; (VSS = $-5 \text{ V}$ ) |           | - 10.3      | 0.3    | V    |                       |

| referred to $VSS = -5 V$ ; $(VDD = 5 V)$       |           | - 0.3       | 10.3   | V    |                       |

| All digital input voltages                     |           |             |        |      |                       |

| referred to GNDI = 0 V; (VDDI = 5 V)           |           | - 0.3       | 5.3    | V    |                       |

| referred to VDDI = 5 V; (GNDI = 0 V)           |           | - 5.3       | 0.3    | V    |                       |

| DC input and output current at any             |           |             | 100    | mA   |                       |

| input or output pin (free from latch-up)       |           |             |        |      |                       |

| Storage temperature                            | $T_{STG}$ | <b>- 65</b> | 125    | °C   |                       |

| Ambient temperature under bias                 | $T_{A}$   | <b>- 45</b> | 90     | °C   |                       |

| Power dissipation                              | $P_{D}$   |             | 1      | W    |                       |

Note: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device.

Functional operation under these conditions is not implied.

Exposure to conditions beyond those indicated in the recommended operational conditions of this specification may effect device reliability.

# 4.2 Operating Range

VDDA...VDDD, VDDZ = 5 V  $\pm$  5%; VDDI= 3.3 V  $\pm$  5% VSS = - 5 V  $\pm$  10%; all GND's = 0 V

| Parameter                                   | Symbol               | Li   | mit Val | ues  | Unit | <b>Test Condition</b>      |

|---------------------------------------------|----------------------|------|---------|------|------|----------------------------|

|                                             |                      | min. | typ.    | max. |      |                            |

| $\overline{V_{\mathrm{DD}}}$ supply current |                      |      |         |      |      |                            |

| Power down digital                          | IDDD <sub>PD</sub>   |      | 7       | 10   | mA   | all channels PDown         |

| Power down analog                           | IDDA <sub>PD</sub>   |      | 10      | 13   | mA   | all channels PDown         |

| Active digital                              | IDDD <sub>Act.</sub> |      | 23      | 30   | mA   | all channels active        |

| Active analog                               | IDDA <sub>Act.</sub> |      | 60      | 70   | mA   | all channels active        |

| $\overline{V_{\rm SS}}$ supply current      |                      |      |         |      |      |                            |

| Power down                                  | ISS <sub>PDown</sub> |      | 0.5     | 1    | mA   | all channels PDown         |

| Active                                      | ISS <sub>Act</sub>   |      | 10      | 13   | mA   | all channels active        |

| Power supply rejection-ratio                | PSRR                 |      |         |      |      | ripple: 1 kHz,<br>80 mVrms |

| Receive VDD                                 |                      | 45   | 60      |      | dB   |                            |

| Receive VSS                                 |                      | 45   | 60      |      | dB   |                            |

| Transmit VDD                                |                      | 40   | 60      |      | dB   |                            |

| Transmit VSS                                |                      | 40   | 60      |      | dB   |                            |

| Power dissipation                           |                      |      |         |      |      |                            |

| Power down                                  | P <sub>PDown</sub>   |      | 75      | 108  | mW   | all channels PDown         |

| Active                                      | P <sub>act1</sub>    |      | 175     |      | mW   | 1 channel active           |

| Active                                      | Pact                 |      | 425     | 550  | mW   | all channels active        |

### 4.3 Electrical Parameters

Functionality and performance is guaranteed for  $T_{\rm A}$  = 0 °C to 70 °C by production testing. Extended temperature range operation at – 40 °C <  $T_{\rm A}$  < 85 °C is guaranteed by design, characterization and periodically sampling and testing production devices at the temperature extremes.

The target figures in this specification are based on the subscriber-line board requirements.

Unless otherwise noted, the transmission characteristics are guaranteed within the test conditions.

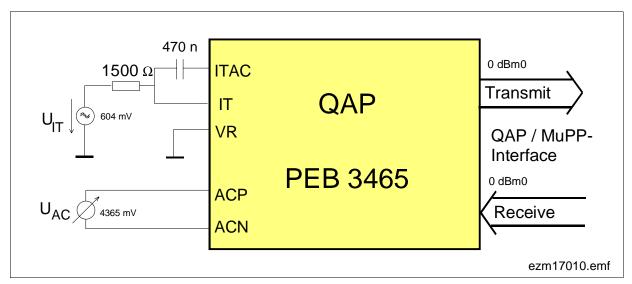

The 0 dBm0 definitions for receive and transmit are different.

A 0 dBm0 signal in transmit direction is equivalent to 604 mVrms.

A 0 dBm0 signal in receive direction is equivalent to 4365 mVrms.

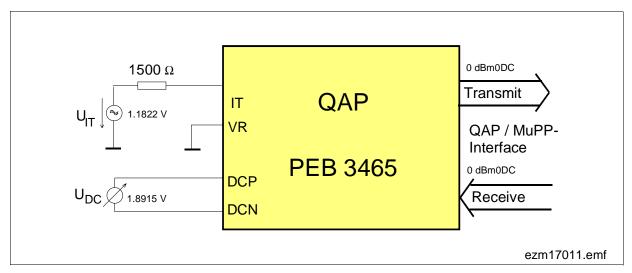

Figure 9 Transmission Characteristics

With  $U_{IT} = 0 \text{ dBm0}|_{QAP} = -2.17 \text{ dBm0}|_{775\text{mV}} = 604 \text{ mV}$  for transmit With  $U_{AC} = 0 \text{ dBm0}|_{QAP} = 15.02 \text{ dBm0}|_{775\text{mV}} = 4365 \text{ mV}$  for receive

# 4.3.1 Transmission Values

all VDD's =  $5V \pm 5\%$ ; VSS =  $-5V \pm 10\%$ ; all GND's = 0 V.

| Parameter                                                 | Symbol | Lir    | nit Valu | ies   | Unit  | <b>Test Condition</b>                                                  | Fig. |

|-----------------------------------------------------------|--------|--------|----------|-------|-------|------------------------------------------------------------------------|------|

|                                                           |        | min.   | typ.     | max.  |       |                                                                        |      |

| Absolute Gain<br>(f = 3003400 Hz)<br>transmit (AG6dB = 0) |        |        |          |       |       |                                                                        |      |

|                                                           | GX0    | - 0.20 | ± 0.05   | 0.20  | dB    | f = 1 kHz                                                              |      |

| receive (AG6dB = 0)                                       | GR0    | - 0.20 | ± 0.05   | 0.20  | dB    | f = 1 kHz                                                              |      |

| transmit (AG6dB = 1)                                      | GXG    | - 0.25 | ± 0.05   | 0.25  | dB    | f = 1 kHz                                                              |      |

| receive (AG6dB = 1)                                       | GRG    | - 0.25 | ± 0.05   | 0.25  | dB    | f = 1 kHz                                                              |      |

| transmit (AG6dB = 1,<br>USGAIN = 1)                       | GRG    | - 0.3  | ± 0.05   | 0.3   | dB    | f = 1 kHz                                                              |      |

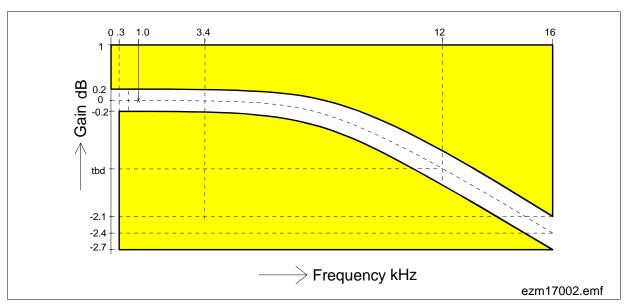

| transmit (TTX-signals)                                    | GTTX-X | - 2.1  | - 2.4    | - 2.7 | dB    | f = 16 kHz                                                             | 10   |

| receive (TTX-signals)                                     | GTTX-R | - 4.0  | - 3.7    | - 3.4 | dB    | f = 16 kHz                                                             | 11   |

| Absolute Gain Variation with temp. – 40° to 85°           |        |        |          | ± 0.1 | dB    |                                                                        |      |

| Total Harmonic distortion                                 |        |        |          |       |       |                                                                        |      |

| transmit                                                  | THDT   |        | - 56     | - 48  | dB    | at – 17 dBm0;<br>f = 1 kHz;<br>2 <sup>nd</sup> , 3 <sup>rd</sup> order |      |

| receive                                                   | THDR   |        | - 56     | - 48  | dB    | at – 17 dBm0;<br>f = kHz;<br>2nd, 3rd order                            |      |

| Idle channel noise                                        |        |        |          |       |       |                                                                        |      |

| transmit                                                  | NTP    |        | - 96     | - 91  | dBm0p | psophometric,<br>VIN = 0 V                                             |      |

|                                                           | NTTXTP |        | - 99     | - 88  | dBm0p | psophometric,<br>VIN = 16 kHz,<br>- 1 dBm0                             |      |

| receive                                                   | NRP    |        | - 100    | - 95  | dBm0p | psophometric, code +0                                                  |      |

|                                                           | NTTXRP |        | - 96     | - 90  | dBm0p | psophometric,<br>VIN = 16 kHz,<br>- 1 dBm0                             |      |

| Crosstalk;<br>any combination of<br>direction and channel | СТ     |        | - 100    |       | dB    | at 0 dBm0, f = 1 kHz;<br>guaranteed by design                          |      |

# **Frequency Response**

1. Transmit: reference frequency 1 kHz, signal level – 17 dBm0:

Figure 10 Frequency Response Transmit

2. Receive: reference frequency 1 kHz, signal level – 17 dBm0:

Figure 11 Frequency Response Receive

### 3. Out-of-Band Signals at Analog Output (Receive)

With a 0 dBm0 sine wave with frequency f (300 Hz to 3.4 kHz) applied to the digital input, the level of any resulting out-of-band signal at the analog output will stay at least 45 dB below a 0 dBm0, 1 kHz sine wave reference signal at the analog output.

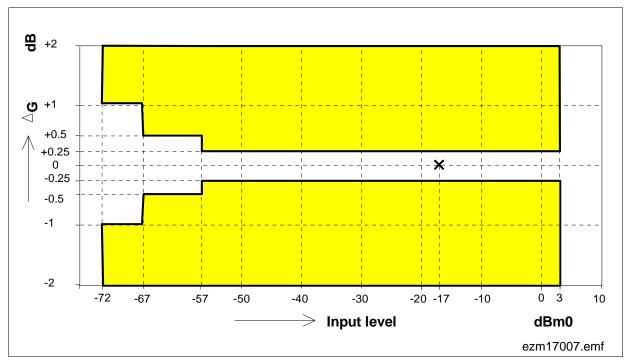

# **Gain Tracking**

The gain deviations stay within the limits in the figure below.

Transmit and Receive:

measured with sine wave f = 1004 Hz; reference level = -17 dBm0

Figure 12 Gain Tracking (Transmit and Receive)

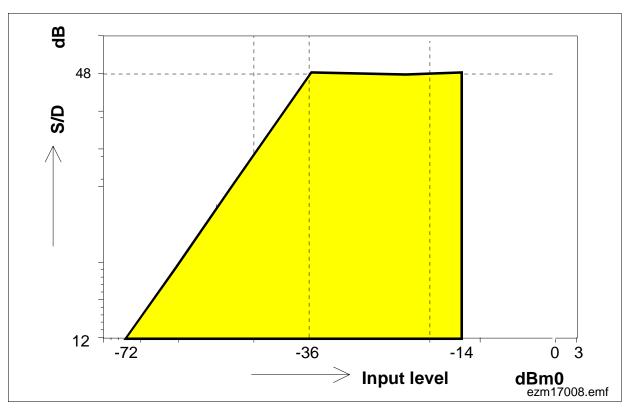

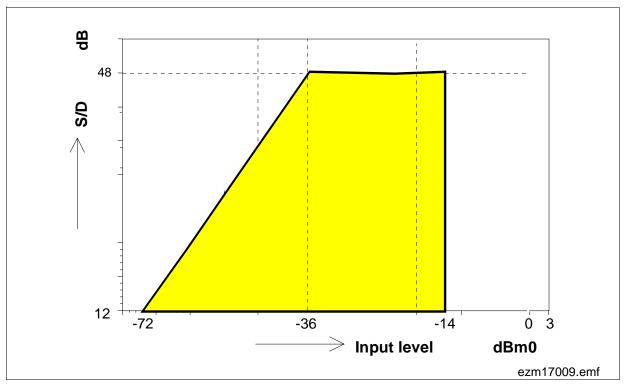

### **Total Distortion**

The signal to distortion ratio exceeds the limits in the following figures:

1. Receive: measured with sine wave f = 1004 Hz.

Figure 13 Total Distortion Receive

**Table 4** Total Distortion Receive

| Parameter            | Symbol          | Limit Values |      | Values |    | Limit Values                  |    | Test Condition | Fig. |

|----------------------|-----------------|--------------|------|--------|----|-------------------------------|----|----------------|------|

|                      |                 | min.         | typ. | max.   |    |                               |    |                |      |

| Signal to Distortion | SD <sub>R</sub> | 48           | 60   |        | dB | Signal $S = -14 \text{ dBm}0$ | 13 |                |      |

# 2. Transmit: measured with sine wave f = 1004 Hz

Figure 14 Total Distortion Transmit

Table 5 Total Distortion Receive

| Parameter            | Symbol          | Limit Values |      | Limit Values |    | Limit Values                  |    | Test Condition | Fig. |

|----------------------|-----------------|--------------|------|--------------|----|-------------------------------|----|----------------|------|

|                      |                 | min.         | typ. | max.         |    |                               |    |                |      |

| Signal to distortion | SD <sub>T</sub> | 48           | 60   |              | dB | Signal $S = -14 \text{ dBm}0$ | 14 |                |      |

# 4.3.2 DC Characteristics

# I/O-Pins

all  $V_{\rm DD}$ 's = 5 V  $\pm$  5%;  $V_{\rm SS}$  = - 5 V  $\pm$  10%; all GND's = 0 V

| Parameter                   | Symbol    | Limit Values |             | Unit | Test Condition                           |  |

|-----------------------------|-----------|--------------|-------------|------|------------------------------------------|--|

|                             |           | min          | max.        |      |                                          |  |

| Digital input pins          |           |              |             |      |                                          |  |

| ADCL, AFSC, ADD, ADR, RESET |           |              |             | V    |                                          |  |

| Low - input voltage         | $V_{IL}$  | - 0.3        | 0.8         | V    |                                          |  |

| High - input voltage        | $V_{IH}$  | 2.0          | VDD<br>+0,3 | V    |                                          |  |

| Input leakage current       | $I_{IL}$  | - 1          | 1           | μΑ   | $-0.3 <= V_{\text{in}} <= V_{\text{DD}}$ |  |

| Spike rejection for RESET   | $t_{rej}$ | 50           | 200         | ns   |                                          |  |

| digital output pin ADU      |           |              |             |      |                                          |  |

| Low-output voltage          | $V_{OL}$  |              | 0.45        | V    | $I_{O} = -2 \text{ mA}$                  |  |

| High-output voltage         | $V_{OH}$  | 2.4          |             | V    | $I_{O}$ = 2 mA                           |  |

| for I/O1 and O1:            |           |              |             |      |                                          |  |

| Low-output voltage          | $V_{OL}$  |              | 0.6         | V    | $I_{\rm O}$ = $-$ 50 mA                  |  |

| High-output voltage         | $V_{OH}$  | 3.5          |             | V    | $I_{O}$ = 2 mA                           |  |

| for I/O2:                   |           |              |             |      |                                          |  |

| Low-output voltage          | $V_{OL}$  |              | 0.5         | V    | $I_{\rm O}$ = $-2$ mA                    |  |

| High-output voltage         | $V_{OH}$  | 3.5          |             | V    | $I_{O}$ = 2 mA                           |  |

# **DC-Feeding**

Figure 15 DC-Feeding Test Circuit

With  $U_{IT}$  = 0 dBm0DC|<sub>QAP</sub> = 1.1822 V for transmit With  $U_{DC}$  = 0 dBm0DC|<sub>QAP</sub> = 1.8915 V for receive

all  $V_{\rm DD}$ 's = 5 V  $\pm$  5%;  $V_{\rm SS}$  = - 5 V  $\pm$  10%; all GND's = 0 V

| Parameter                                                 | Symbol                       | Limit Values   |             |              | Unit     | <b>Test Condition</b>                                         | Fig.     |

|-----------------------------------------------------------|------------------------------|----------------|-------------|--------------|----------|---------------------------------------------------------------|----------|

|                                                           |                              | min.           | typ.        | max.         |          |                                                               |          |

| "Line Current" Measurement (IT):                          |                              |                |             |              |          |                                                               |          |

| Transmit                                                  | $V_{\rm IT~offset}^{\rm 1)}$ | - 50           |             | 50           | mV       |                                                               |          |

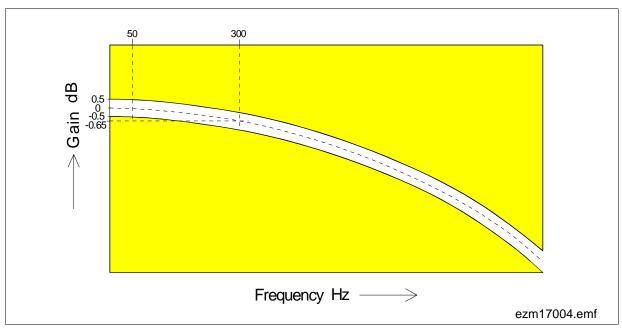

|                                                           | $V_{IT\;gain}$               | - 0.5<br>- 1.2 | 0<br>- 0.65 | 0.5<br>- 0.1 | dB<br>dB | f < 50 Hz<br>f = 300 Hz                                       | 16<br>16 |

|                                                           | $V_{IT\;THD	ext{-}}$         | 40             | 50          |              | dB       | f = 300 Hz                                                    |          |

| Additional gain variation with temperature – 40° to + 85° |                              |                |             | ± 0.1        | dB       |                                                               |          |

| "Line Voltage" Feeding (DCP, DCN):                        |                              |                |             |              |          |                                                               |          |

| Receive                                                   | $V_{DC}$ offset              | - 25           |             | 25           | mV       |                                                               |          |

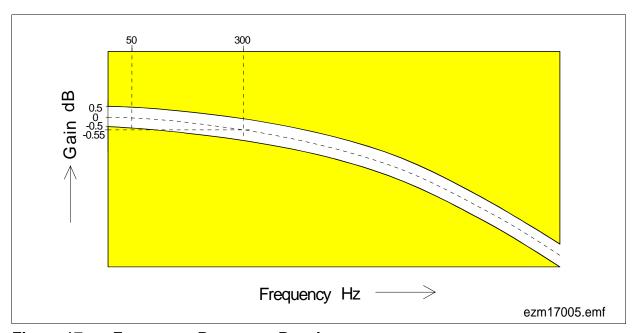

|                                                           | $V_{ m DC\ gain}$            | - 0.5<br>- 1.1 | 0<br>- 0.55 | 0.5<br>0.0   | dB<br>dB | f < 50 Hz,<br>dc_dispofi = 1<br>f = 300 Hz,<br>dc_dispofi = 1 | 17<br>17 |

|                                                           | $V_{DC\;THD}$                | 40             | 50          |              | dB       | f=300 Hz,<br>dc_dispofi = 1                                   |          |

| Receive Boosted                                           | $V_{DC\;Boost}$              | 3.5            | 4.1         | 4.7          | dB       | dc_dacgain = 1                                                |          |

| Additional gain variation with temperature – 40° to + 85° |                              |                |             | ± 0.1        | dB       |                                                               |          |

<sup>1)</sup> This offset can be compensated in the system by performing an offset measurement as described in the Application note "Line and Board Testing with MuSLIC".

Data Sheet 35 2000-07-14

# **DC-Frequency Response**

1. Transmit: reference frequency 50 Hz, signal level 0dBm0<sub>DC</sub>

Figure 16 Frequency Response Transmit

2. Receive: reference frequency 50 Hz, signal level 0dBm0<sub>DC</sub>

Figure 17 Frequency Response Receive

# **AHV-SLIC Interface & Supervision Functions**

all  $V_{\rm DD}$ 's = 5 V  $\pm$  5%;  $V_{\rm SS}$  = - 5 V  $\pm$  10%; all GND's = 0 V

| Parameter                                                              | Symbol                | Limit Values |              |              | Unit     | Test Condition/Result                               | Fig. |

|------------------------------------------------------------------------|-----------------------|--------------|--------------|--------------|----------|-----------------------------------------------------|------|

|                                                                        |                       | min. typ.    |              | max.         |          |                                                     |      |

| Output voltage:<br>AHV-SLIC-<br>Interface C1, C2                       |                       |              |              |              |          |                                                     |      |

| High level                                                             | $V_{OHHV}$            | 3.65         |              |              | V        | $I_{\text{out}}$ < 10 $\mu$ A                       |      |

| Mid level                                                              | $V_{OMHV}$            | 2.2          |              | 2.8          | V        | $I_{\text{out}}$ < 10 $\mu$ A                       |      |

| Low level                                                              | $V_{OLHV}$            |              |              | 1.35         | V        | $I_{\text{out}}$ < 10 $\mu$ A                       |      |

| Current drained from pin C1 in all 3 states                            | $I_{OTLo} \ I_{OTHi}$ | 130          |              | 30           | μA<br>μA | tempa = $0^{1}$<br>tempa = $1$                      |      |

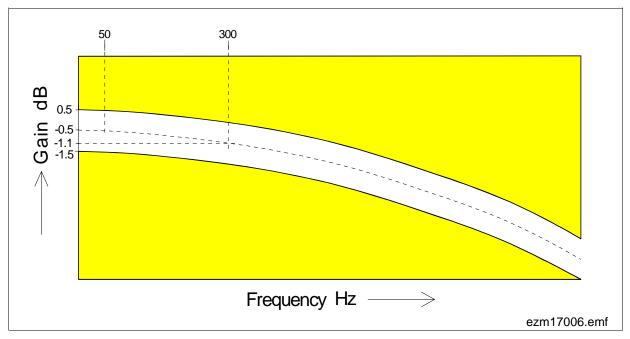

| Longitudinal Current Input (IL)                                        | $V_{IL}$ gain         | - 1.2        | - 0.5        | 0.2          | dB       | f < 50  Hz;<br>$V_{\text{in}} = 0 \text{dBm0}_{DC}$ | 18   |

|                                                                        |                       | - 1.8        | - 1.1        | - 0.4        | dB       | f = 300Hz                                           | 18   |

| Auxiliary Inputs (V <sub>A</sub> , V <sub>B</sub> , V <sub>BIM</sub> ) | $V_{x\;gain}$         | - 1.2        | - 0.5        | 0.2          | dB       | f < 50Hz;<br>$V_{in} = 0dBm0_{DC}$                  | 18   |

|                                                                        |                       | - 1.8        | - 1.1        | - 0.4        | dB       | f = 300Hz                                           | 18   |

| $\overline{V_{DDIM}}$                                                  | $V_{DDIM}$            | 0.22*<br>VDD | 0.24*<br>VDD | 0.26*<br>VDD | V        | internal connected to VDDZ/4                        | 18   |

<sup>1)</sup> TEMPA is reported via the MuPP/QAP-Interface to the MuPP

Figure 18 Frequency Response: Longitudinal Current Input & Auxiliary Inputs

# 4.3.3 MuPP-Interface Timing Characteristics

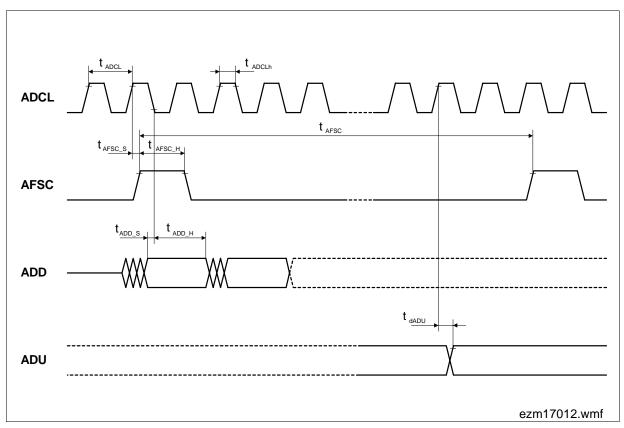

Figure 19 MuPP-Interface Timing Characteristics

| Parameter       | Symbol              |      | Unit    |      |    |

|-----------------|---------------------|------|---------|------|----|

|                 |                     | min. | typ.    | max. |    |

| Period ADCL     | $t_{ADCL}$          |      | 1/16384 |      | ms |

| ADCL duty cycle | $t_{ADCLh}$         | 40   | 50      | 60   | %  |

| Period AFSC     | $t_{AFSC}$          |      | 500     |      | μs |

| AFSC setup      | t <sub>AFSC_S</sub> | 10   |         |      | ns |

| AFSC hold       | t <sub>AFSC_H</sub> | 10   |         |      | ns |

| ADD setup time  | t <sub>ADD S</sub>  | 10   |         |      | ns |

| ADD hold time   | $t_{ADD\;H}$        | 10   |         |      | ns |

| ADU delay       | $t_{\sf dADU}$      |      | 15      | 30   | ns |

# 5 Package Outlines

Figure 20 Package Outline: PEB 3465 (QAP)

### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our data book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm

# 6 Glossary

ACT Active Mode

ADC Analog Digital Converter

AGR Attenuation Receive

AGX Attenuation Transmit

AHV-SLIC Advanced High Voltage Subscriber Line Interface Circuit

BB Boosted Battery

BiCMOS Bipolar Complementary Metal Oxid Semiconductor

C1, 2 Digital Interface between QAP and AHV-SLIC

CMP Compander CODEC Coder Decoder

DAC Digital Analog Converter DCCHAR DC Characteristic block

DCL Data Clock

DD Data Downstream

DSP Digital Signal Processor

EXP Expander

FRR Frequency Response Receive Filter FRX Frequency Response Transmit Filter

FSC Frame Sync.

I1 Fixed Input Pin

IL Longitudinal Current Input IO User Programmable I/O Pin

ISDN Integrated Service Digital Network

IT Transversal Current Input (for AC and DC)

ITAC Transversal Current Input (for AC)

MuPP Multi Channel Processor for POTS

MuSLIC Multi Channel Subscriber Line Interface Circuit

MuSLICOS MuSLIC Oriented Software

O1 Fixed Output Pin

PCM Pulse Code Modulation

POTS Plain Old Telephone Service

PREFI Antialiasing Pre Filter

QAP Quad Analog POTS

RNG Ring Generator

SLIC Subscriber Line Interface Circuit

TST1 Test Pin

TH Transhybrid Balancing

THFIX Transhybrid Balancing Filter (fixed)

TTX Teletax

TTXGEN Teletax Generator

VBIM Battery Image Input

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com