## **CD2481**

### Programmable Four-Channel Communications Controller

### **Datasheet**

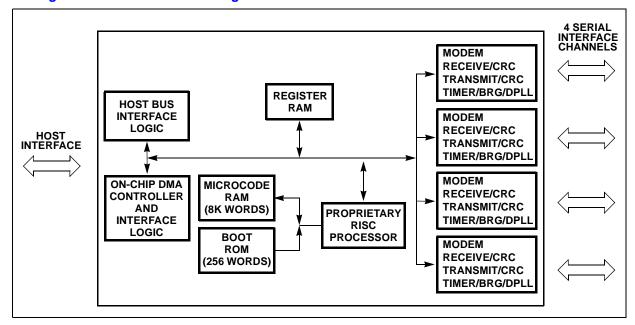

The CD2481 is a four-channel synchronous/asynchronous communications controller specifically designed to reduce host-system processing overhead and increase efficiency in a wide variety of communications applications. A special member of the CD24X1 family, the device allows easy field upgrades and enhancement with an on-chip 8K-word microcode store for downloaded control code. The CD2481 is packaged in a 100-pin MQFP package that offers 10 data/clock/modem pins per channel. The device has four fully independent serial channels to support standard asynchronous, PPP, MNP®4, SLIP, bit-synchronous (HDLC), and byte-synchronous (bisync, X.21) protocols. *The device is non-functional until the microcode is downloaded; only a small boot ROM with code to perform device initialization is included.*

The device is based on a proprietary on-chip RISC processor that performs all the time-critical, low-level tasks otherwise performed by the host system.

The CD2481 boosts system efficiency with eight on-chip DMA channels, on-chip FIFOs (16 bytes/direction), intelligent vectored interrupts, and intelligent protocol processing. The on-chip DMA controller provides 'fire-and-forget' transmit support — the host need only inform the CD2481 of the location of the packet to send. Similarly, on receive, the CD2481 automatically receives a complete packet with no host intervention or assistance. The DMA controller also has a transmit 'Append mode' for use in asynchronous applications.

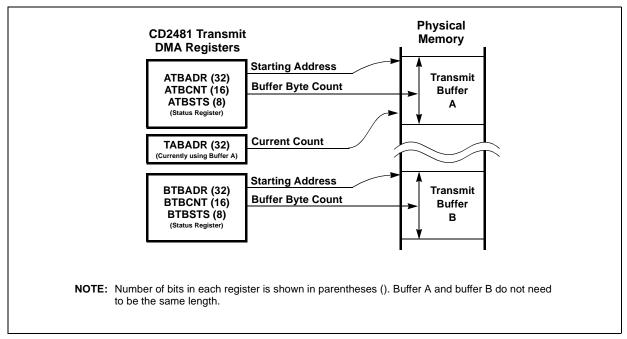

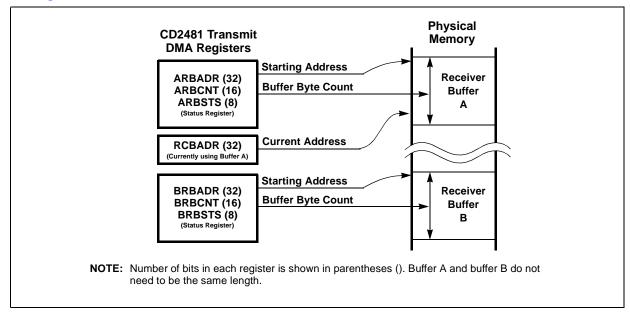

The DMA controller uses a dual-buffer scheme that easily implements simple or complex buffer schemes. Each channel and direction in the dual-buffer scheme has two active buffers.

The CD2481 can be programmed to interrupt the host at the completion of a frame or buffer. In applications where buffers are of a small, fixed size, the dual-buffer scheme allows large frames to be divided into multiple buffers.

For applications where a DMA interface is not desired, the device can be operated as either interrupt-driven or polled. This choice is available for each channel and each direction. For example, a channel can be programmed for DMA transmit and interrupt-driven receive. In either case, 16-byte FIFOs on each channel and in each direction reduce latency time requirements, making both software and hardware designs less time-critical. Threshold levels on the FIFOs are user-programmable.

Vectored interrupts are another way the CD2481 helps system efficiency. Separate interrupts are generated for transmit, receive, and modem-signal/timer changes with unique, user-defined vectors for each type and channel. This allows very flexible interfacing and fast, efficient interrupt coding. For example, the Good Data™ interrupt allows the host to vector directly to a routine that transfers the receive data — no status or error checking is required.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The CD2481 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Feat  | ures           |                                      | 9  |

|-----|-------|----------------|--------------------------------------|----|

|     | 1.1   |                | its                                  |    |

|     | 1.2   | CD2X           | XX Device Family Compatibility       | 12 |

| 2.0 | Con   | ventior        | 1S                                   | 13 |

|     | 2.1   |                | viations                             |    |

|     | 2.2   | Acron          | yms                                  | 14 |

| 3.0 | Pin I | Informa        | ation                                | 15 |

|     | 3.1   | Pin Di         | agram — CD2481                       | 15 |

|     | 3.2   |                | unctions — CD2481                    |    |

|     | 3.3   | Pin De         | escriptions                          | 16 |

| 4.0 | Regi  | ister Su       | ummaries                             | 20 |

|     | 4.1   | Memo           | ry Map                               | 20 |

|     |       | 4.1.1          | Global Registers                     |    |

|     |       | 4.1.2          | Option Registers                     | 21 |

|     |       | 4.1.3          | Bit Rate and Clock Option Registers  | 22 |

|     |       | 4.1.4          | Channel Command and Status Registers | 22 |

|     |       | 4.1.5          | Interrupt Registers                  | 22 |

|     |       | 4.1.6          | DMA Registers                        |    |

|     |       | 4.1.7          | Timer Registers                      |    |

|     | 4.2   | _              | ter Definitions                      |    |

|     |       | 4.2.1          | Global Registers                     |    |

|     |       | 4.2.2          | Option Registers                     |    |

|     |       | 4.2.3          | Bit Rate and Clock Option Registers  |    |

|     |       | 4.2.4          | Channel Command and Status Registers |    |

|     |       | 4.2.5          | Interrupt Registers                  |    |

|     |       | 4.2.6          | DMA Registers                        |    |

|     |       | 4.2.7          | Timer Registers                      |    |

| 5.0 | Fund  |                | Description                          |    |

|     | 5.1   | Host I         | nterface                             |    |

|     |       | 5.1.1          | Host Read and Write Cycles           |    |

|     |       | 5.1.2          | Byte and Word Transfers              |    |

|     | 5.2   |                | ıpts                                 |    |

|     |       |                | Contexts and Channels                |    |

|     |       | 5.2.2          | Interrupt Registers                  |    |

|     |       | 5.2.3          | Groups and Types                     |    |

|     | 5.0   | 5.2.4          | Hardware Signals and IACK Cycles     |    |

|     | 5.3   |                | and Timer Operations                 |    |

|     |       | 5.3.1          | Receive FIFO Operation               |    |

|     |       | 5.3.2          | Transmit FIFO Operation              |    |

|     |       | 5.3.3          | Timers in Synchronous Protocols      |    |

|     |       | 5.3.4          | Timers in Asynchronous Protocols     |    |

|     |       | 5.3.5<br>5.3.6 | Timers in Asynchronous Protocols     |    |

|     |       | ა.ა.ნ          | Transmit Timer                       | 45 |

|            | 5.4  | DMA Operation                                       |      |

|------------|------|-----------------------------------------------------|------|

|            |      | 5.4.1 Bus Acquisition Cycle                         | 46   |

|            |      | 5.4.2 DMA Data Transfer                             |      |

|            |      | 5.4.3 Bus Error Handling                            |      |

|            |      | 5.4.4 A and B Buffers and Chaining                  |      |

|            |      | 5.4.5 Transmit DMA Transfer                         | 49   |

|            |      | 5.4.6 Synchronous Transmitter Examples              | 50   |

|            |      | 5.4.7 Receive DMA Transfer                          | 52   |

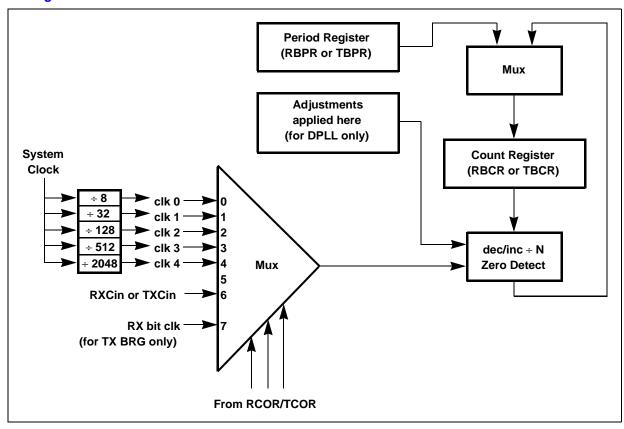

|            | 5.5  | Bit Rate Generation and Data Encoding               |      |

|            | 5.6  | Hardware Configurations                             | 67   |

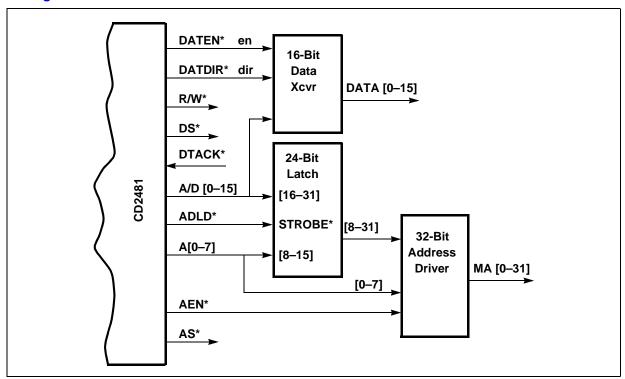

|            |      | 5.6.1 Interface to a 32-Bit Data Bus                |      |

|            |      | 5.6.2 DMA Connections for the CD2481                |      |

|            |      | 5.6.3 Recommended CD2481 as a DTE and DCE Interface | ce68 |

| 6.0        | Micr | ocode Download                                      | 70   |

|            | 6.1  | Microcode Download Information                      | 70   |

|            | 0    | 6.1.1 Registers Specific to Download Operations     |      |

|            |      | 6.1.2 Download Code Example                         |      |

| <b>7</b> 0 | D (  | ·                                                   |      |

| 7.0        | Prot | ocol Processing                                     |      |

|            | 7.1  | HDLC Processing                                     | 75   |

|            |      | 7.1.1 FCS (Frame Check Sequence)                    | 75   |

|            |      | 7.1.2 HDLC Transmit Mode                            | 75   |

|            |      | 7.1.3 HDLC Receive Mode                             |      |

|            | 7.2  | PPP (Point-to-Point Protocol) Mode                  | 77   |

|            |      | 7.2.1 Character Format                              |      |

|            |      | 7.2.2 Frame Format                                  |      |

|            |      | 7.2.3 FCS (Frame Check Sequence)                    |      |

|            |      | 7.2.4 Transparency                                  |      |

|            |      | 7.2.5 Definition of a Valid Frame                   |      |

|            |      | 7.2.6 Transmitter                                   |      |

|            |      | 7.2.7 Receiver                                      |      |

|            | 7.3  | SLIP Processing                                     |      |

|            |      | 7.3.1 Framing                                       |      |

|            |      | 7.3.2 Debugging Aids                                |      |

|            | 7.4  | MNP4,/ARAP Protocol Processing                      |      |

|            |      | 7.4.1 Framing                                       |      |

|            |      | 7.4.2 MNP4,/ARAP FCS (Frame Check Sequence) Calcu   |      |

|            | 7.5  | Async Processing                                    |      |

|            |      | 7.5.1 Transmitter In-Band Flow Control              |      |

|            |      | 7.5.2 Receiver In-Band Flow Control                 |      |

|            |      | 7.5.3 Out-of-Band Flow Control                      |      |

|            |      | 7.5.4 Line Break Detection and Generation           |      |

|            |      | 7.5.5 Special Character Transmission                |      |

|            |      | 7.5.6 Special Character Recognition                 |      |

|            |      | 7.5.7 Special Character Range                       |      |

|            | 7.0  | 7.5.8 UNIX Support Features                         |      |

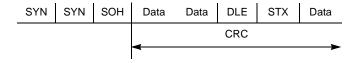

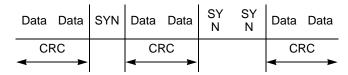

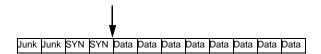

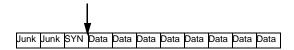

|            | 7.6  | Bisync Protocol                                     |      |

|            |      | 7.6.1 Bisync Transmit Processing                    |      |

|            |      | 7.6.2 Bisync Receive Processing                     | 92   |

|     |      | 7.6.3 CRC Calculation in Bisync Mode                                                  |     |

|-----|------|---------------------------------------------------------------------------------------|-----|

|     |      | 7.6.4 BCC Computation Formulas                                                        | 94  |

|     |      | 7.6.5 Receive State Tables                                                            | 95  |

|     | 7.7  | X.21 Call Set-Up Mode                                                                 | 97  |

|     |      | 7.7.1 X.21 Transmit                                                                   | 97  |

|     |      | 7.7.2 X.21 Receive                                                                    | 97  |

|     | 7.8  | Extended X.21 Mode                                                                    | 99  |

|     |      | 7.8.1 Extended X.21 Transmit                                                          | 99  |

|     |      | 7.8.2 Extended X.21 Receive                                                           | 99  |

|     | 7.9  | Programmable Sync                                                                     | 100 |

|     |      | 7.9.1 Programmable Sync Transmit                                                      | 101 |

|     |      | 7.9.2 Programmable Sync Receive                                                       | 101 |

|     | 7.10 | Non-8-Bit Data Transfers                                                              | 102 |

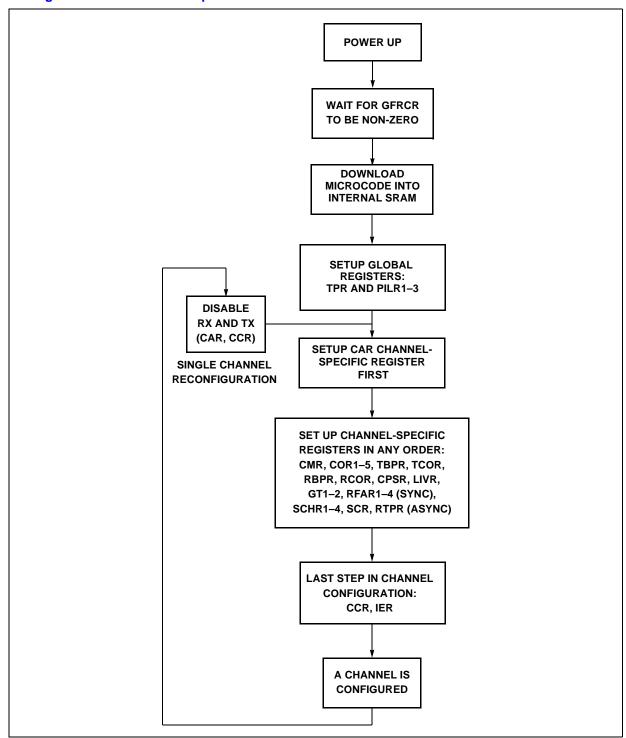

| 8.0 | Prog | ramming Examples                                                                      | 103 |

|     | 8.1  | Global Initialization                                                                 | 105 |

|     | 8.2  | Async Interrupt Setup Example                                                         |     |

|     | 8.3  | HDLC DMA Channel Setup Example                                                        |     |

|     | 8.4  | Receive DMA Interrupt Service Routine                                                 |     |

|     | 8.5  | Transmit Interrupt Service Routine                                                    |     |

|     | 8.6  | Support Files from the Intel FTP Server                                               |     |

|     |      |                                                                                       |     |

| 9.0 | Deta | iled Register Descriptions                                                            |     |

|     | 9.1  | Global Registers                                                                      |     |

|     |      | 9.1.1 Global Firmware Revision Code Register (GFRCR)                                  |     |

|     |      | 9.1.2 Channel Access Register (CAR)                                                   |     |

|     | 9.2  | Option Registers                                                                      |     |

|     |      | 9.2.1 Channel Mode Register (CMR)                                                     |     |

|     |      | 9.2.2 Channel Option Register 1 (COR1)                                                |     |

|     |      | 9.2.3 Channel Option Register 2 (COR2)                                                |     |

|     |      | 9.2.4 Channel Option Register 3 (COR3)                                                |     |

|     |      | 9.2.5 Channel Option Register 4 (COR4)                                                |     |

|     |      | 9.2.6 Channel Option Register 5 (COR5)                                                |     |

|     |      | 9.2.7 Channel Option Register 6 (COR6)                                                | 132 |

|     |      | 9.2.8 Channel Option Register 7 (COR7)                                                | 135 |

|     |      | 9.2.9 Special Character Registers –                                                   |     |

|     |      | Async and Programmable Sync Modes136 9.2.10 Special Character Range – Async Mode Only | 120 |

|     |      | 9.2.11 LNext Character (LNXT) – Async Mode Only                                       |     |

|     |      | 9.2.12 Receive Frame Address Registers – HDLC Sync Mode Only                          |     |

|     |      | 9.2.13 CRC Polynomial Select Register (CPSR)                                          |     |

|     |      | 9.2.14 Transmit Special Mapped Characters – PPP Mode only                             |     |

|     |      | 9.2.15 Transmit Async Control Character Maps –                                        | 14  |

|     |      | Async-HDLC/PPP Mode Only142                                                           |     |

|     |      | 9.2.16 Receive Async Control Character Maps –                                         |     |

|     |      | Async-HDLC/PPP Mode Only143                                                           |     |

|     | 9.3  | Bit Rate and Clock Option Registers                                                   | 145 |

|     | 0.0  | 9.3.1 Receive Baud Rate Generator Registers                                           |     |

|     |      | 9.3.2 Transmit Baud Rate Generator Registers                                          |     |

|     | 9.4  | Channel Command and Status Registers                                                  |     |

|     | J. 1 | 9.4.1 Channel Command Register (CCR)                                                  |     |

|     |      |                                                                                       |     |

|          |       | 9.4.2          | Special Transmit Command Register (STCR)                    |     |

|----------|-------|----------------|-------------------------------------------------------------|-----|

|          |       | 9.4.3<br>9.4.4 | Channel Status Register (CSR)                               |     |

|          | 9.5   |                | Modem Signal Value Registers (MSVR) pt Registers            |     |

|          | 9.5   | 9.5.1          | General Interrupt Registers                                 |     |

|          |       | 9.5.2          | Receive Interrupt Registers                                 |     |

|          |       | 9.5.3          | Transmit Interrupt Registers                                |     |

|          |       | 9.5.4          | Modem Interrupt Registers                                   |     |

|          | 9.6   |                | Registers                                                   |     |

|          | 0.0   | 9.6.1          | DMA Mode Register (DMR)                                     |     |

|          |       | 9.6.2          | Bus Error Retry Count (BERCNT)                              |     |

|          |       | 9.6.3          | DMA Buffer Status (DMABSTS)                                 |     |

|          |       | 9.6.4          | DMA Receive Registers                                       |     |

|          |       | 9.6.5          | DMA Transmit Registers                                      |     |

|          | 9.7   | Timer I        | Registers                                                   |     |

|          |       | 9.7.1          | Timer Period Register (TPR)                                 |     |

|          |       | 9.7.2          | Receive Time-Out Period Register (RTPR) – Async Modes Only. |     |

|          |       | 9.7.3          | General Timer 1 (GT1) – Sync Modes Only                     |     |

|          |       | 9.7.4          | General Timer 2 (GT2) – Sync Modes Only                     |     |

|          |       | 9.7.5          | Transmit Timer Register (TTR) – Async Modes Only            | 200 |

| 10.0     | Elect | rical S        | pecifications                                               | 201 |

| 10.0     |       |                | •                                                           |     |

|          | 10.1  |                | te lectri Maximum Ratings (Revision B at 35 MHz)            |     |

|          | 10.2  |                | ectrical Characteristics (Revision B at 35 MHz)             |     |

|          | 10.3  |                | ctrical Characteristics (Revision B at 35 MHz)              |     |

|          | 10.4  |                | te Maximum Ratings (Revisions B and D at 60 MHz)            |     |

|          | 10.5  |                | ectrical Characteristics (Revisions B and D at 60 MHz)      |     |

|          | 10.6  | AC Ele         | ectrical Characteristics (Revisions B and D at 60 MHz)      | 205 |

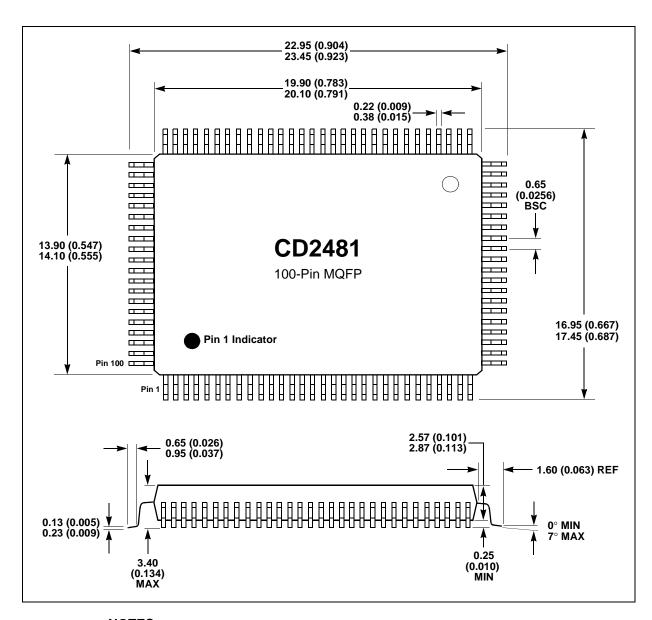

| 11.0     | Pack  | age Sp         | ecifications                                                | 215 |

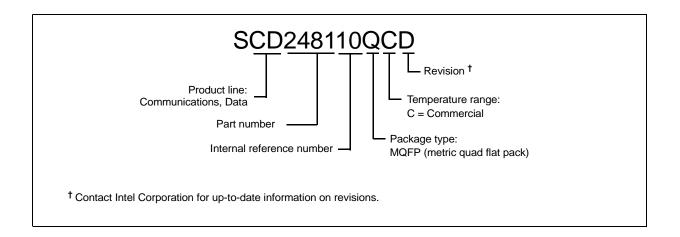

| 12.0     | Orde  | rina Inf       | formation Example                                           | 216 |

|          |       |                |                                                             |     |

| Index    |       |                |                                                             | 217 |

|          |       |                |                                                             |     |

| Figures  |       |                |                                                             |     |

| i iguico | 1     | Functio        | onal Block Diagram                                          | 11  |

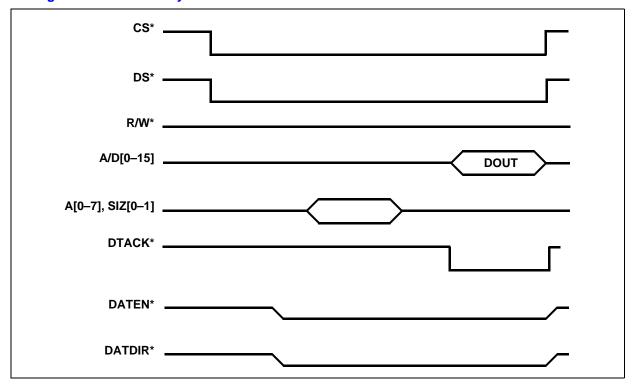

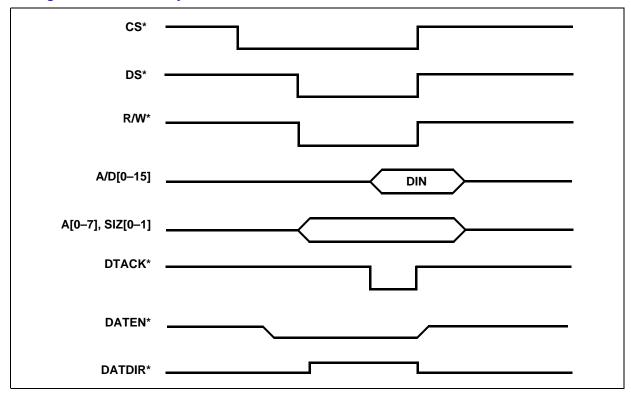

|          | 2     |                | ead Cycle                                                   |     |

|          | 3     |                | /rite Cycle                                                 |     |

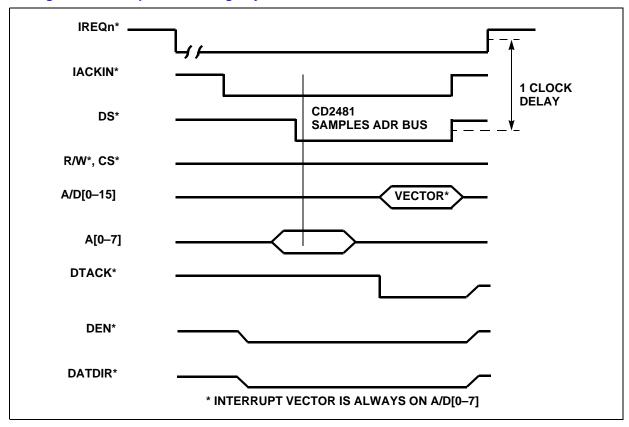

|          | 4     |                | pt Acknowledge Cycle                                        |     |

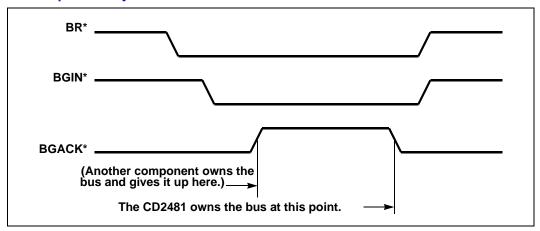

|          | 5     |                | equisition Cycle                                            |     |

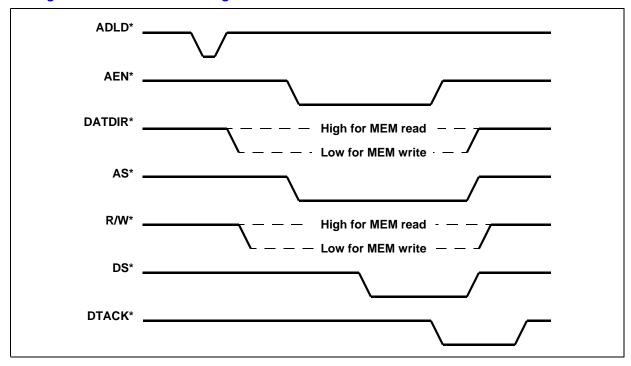

|          | 6     |                | ransfer Timing                                              |     |

|          | 7     |                | nitter A and B Buffers                                      |     |

|          | 8     |                | er A and B Buffers                                          |     |

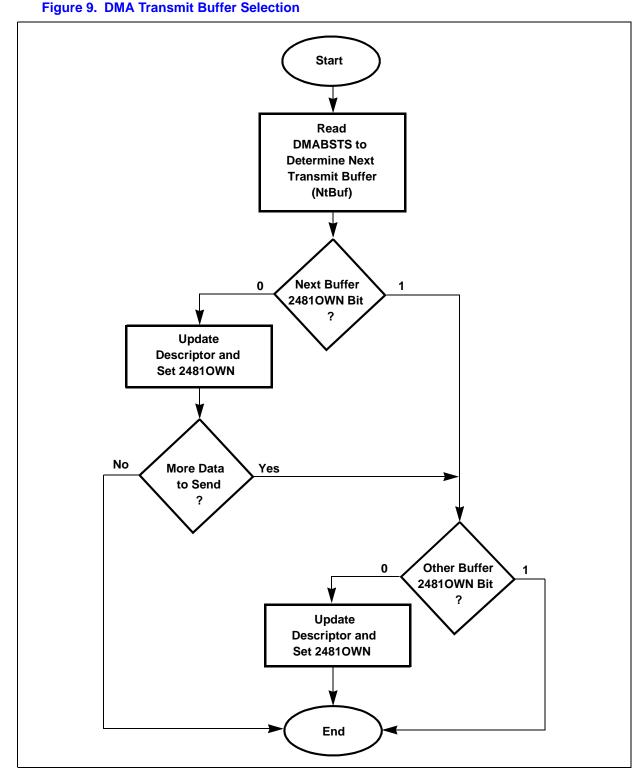

|          | 9     |                | ransmit Buffer Selection                                    |     |

|          | 10    |                | e Generator/DPLL                                            |     |

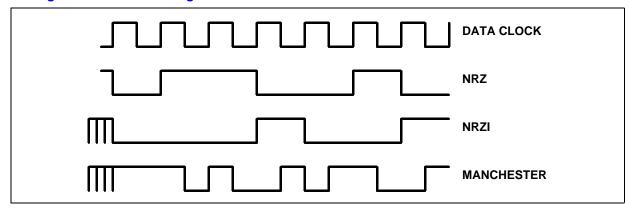

|          | 11    |                | ncoding                                                     |     |

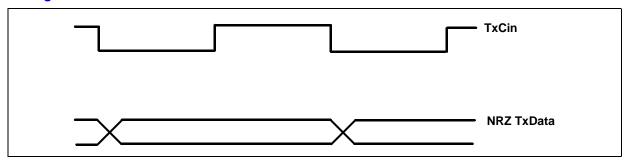

|          | 12    |                | nit Data With External Clock In                             |     |

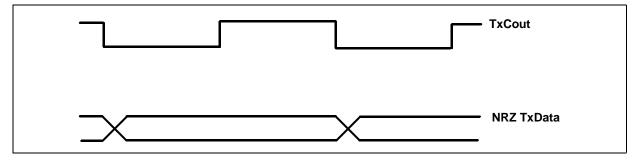

|          | 13    |                | nit Data With External Clock Out                            |     |

**Tables**

## **Programmable Four-Channel Communications Controller — CD2481**

| 14                                                                 | DMA Connections for the CD2481                                                                                                                                                                                                                                                                                                                                                             | 68                   |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

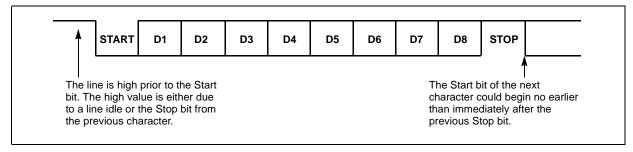

| 15                                                                 | Character Format                                                                                                                                                                                                                                                                                                                                                                           |                      |

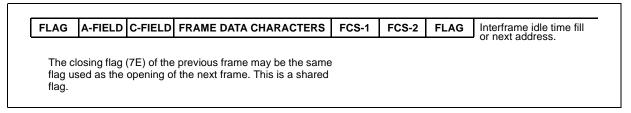

| 16                                                                 | Point-to-Point Protocol Frame                                                                                                                                                                                                                                                                                                                                                              |                      |

| 17                                                                 | ARAP 1.0 Frame                                                                                                                                                                                                                                                                                                                                                                             | 83                   |

| 18                                                                 | ARAP 2.0 Frame                                                                                                                                                                                                                                                                                                                                                                             |                      |

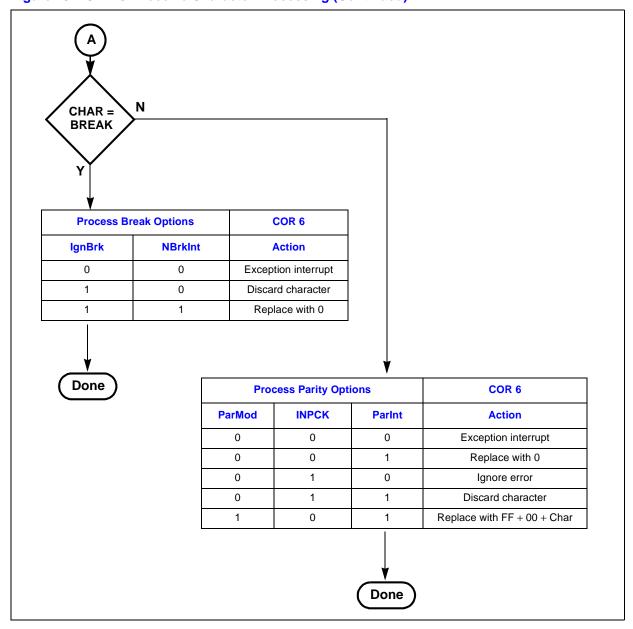

| 19                                                                 | CD2481 Receive Character Processing                                                                                                                                                                                                                                                                                                                                                        |                      |

| 20                                                                 | Initialization Sequence for the CD2481                                                                                                                                                                                                                                                                                                                                                     |                      |

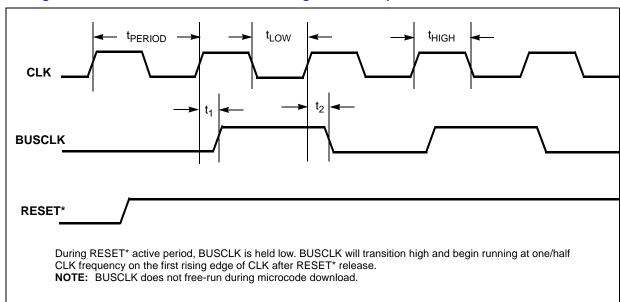

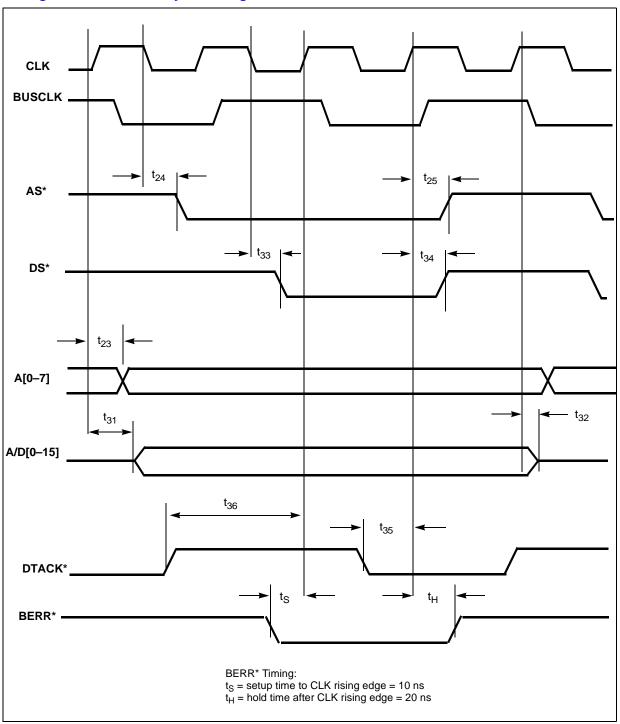

| 21                                                                 | CLK / BUSCLK / RESET* Timing Relationship                                                                                                                                                                                                                                                                                                                                                  | 206                  |

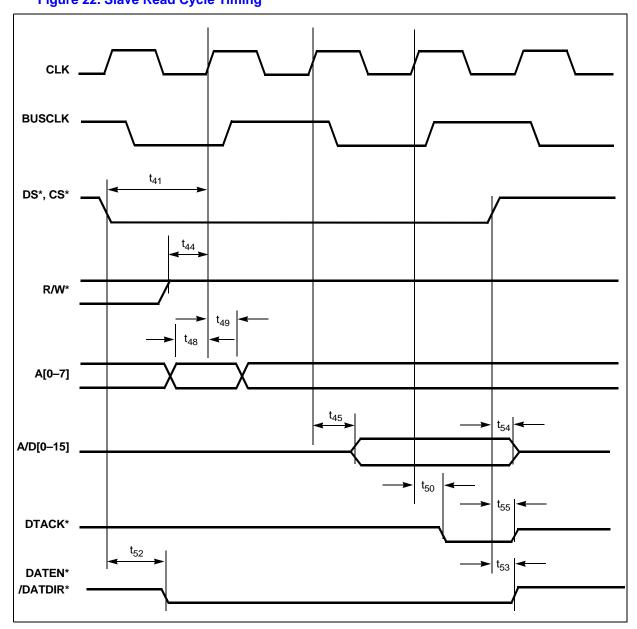

| 22                                                                 | Slave Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                    | 207                  |

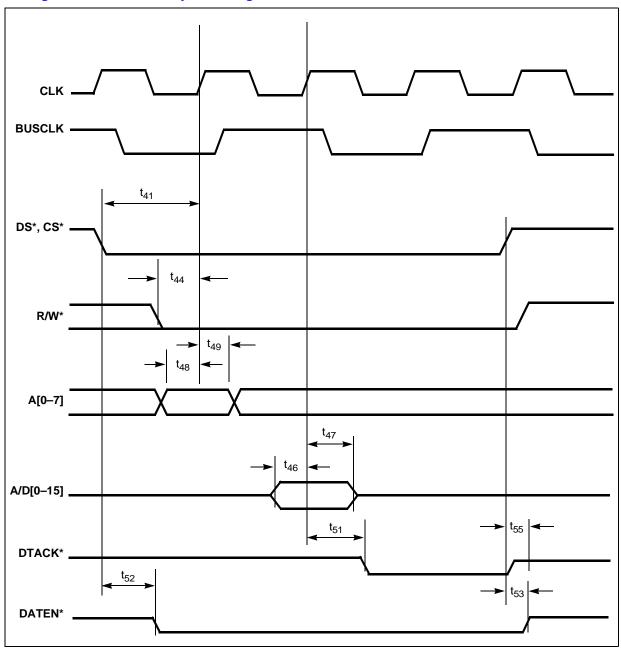

| 23                                                                 | Slave Write Cycle Timing                                                                                                                                                                                                                                                                                                                                                                   |                      |

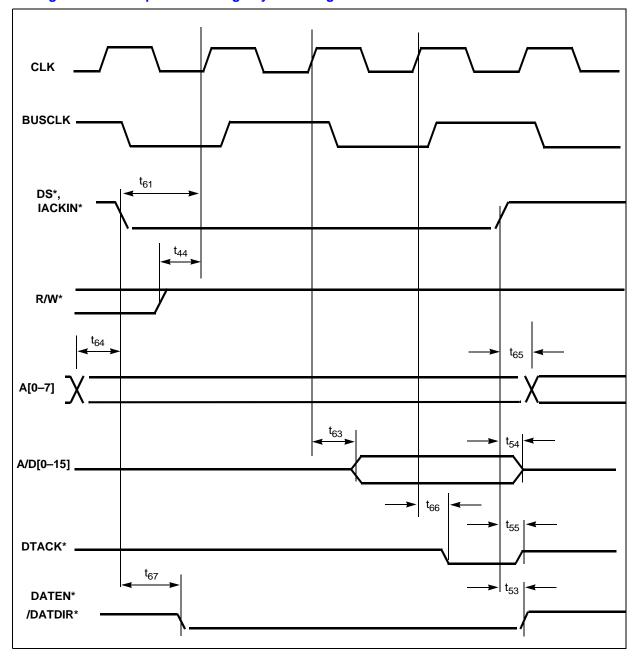

| 24                                                                 | Interrupt Acknowledge Cycle Timing                                                                                                                                                                                                                                                                                                                                                         | 209                  |

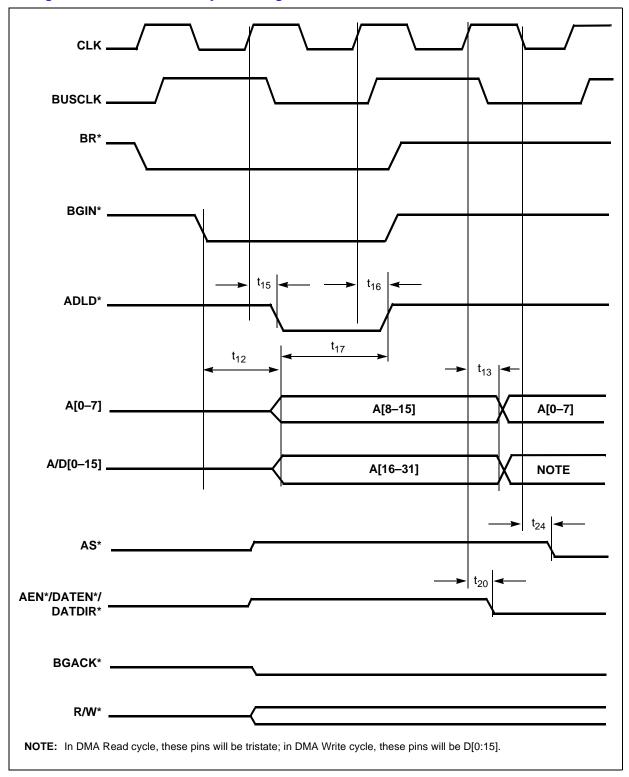

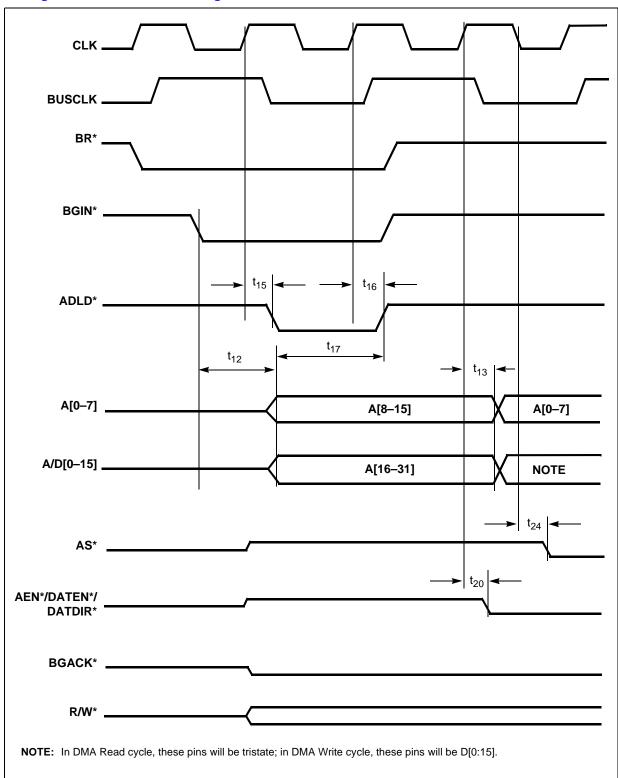

| 25                                                                 | Bus Arbitration Cycle Timing                                                                                                                                                                                                                                                                                                                                                               | 210                  |

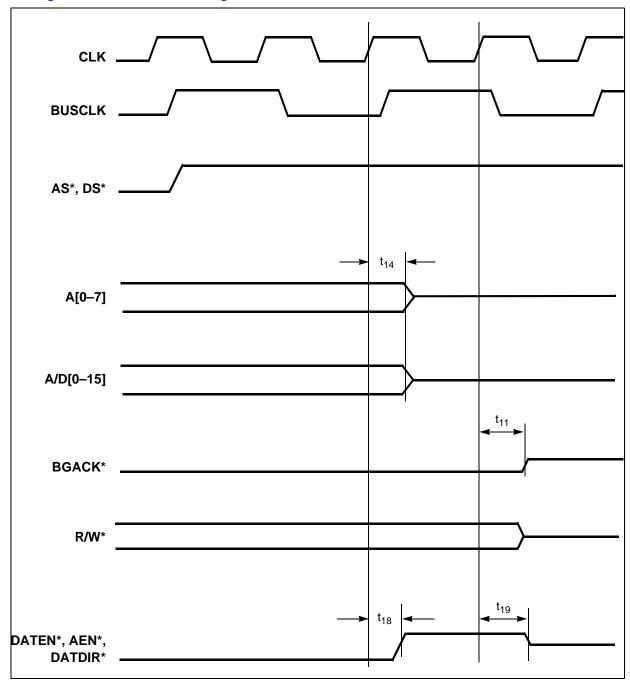

| 26                                                                 | Bus Release Timing                                                                                                                                                                                                                                                                                                                                                                         | 211                  |

| 27                                                                 | Bus Release Timing                                                                                                                                                                                                                                                                                                                                                                         | 212                  |

| 28                                                                 | DMA Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                      | 213                  |

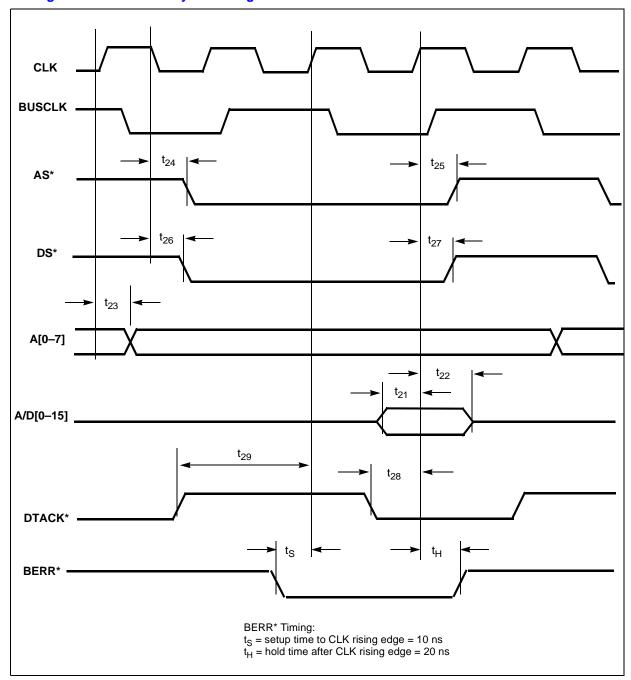

| 29                                                                 | DMA Write Cycle Timing                                                                                                                                                                                                                                                                                                                                                                     | 214                  |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| 1                                                                  | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                           | 17                   |

| 1                                                                  | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                           |                      |

| 2                                                                  | Transmit and Receive Interrupt Service Requests                                                                                                                                                                                                                                                                                                                                            | 42                   |

| 2 3                                                                | Transmit and Receive Interrupt Service Requests                                                                                                                                                                                                                                                                                                                                            | 42<br>48             |

| 2<br>3<br>4                                                        | Transmit and Receive Interrupt Service Requests                                                                                                                                                                                                                                                                                                                                            | 42<br>48<br>62       |

| 2<br>3<br>4<br>5                                                   | Transmit and Receive Interrupt Service Requests                                                                                                                                                                                                                                                                                                                                            | 42<br>48<br>62<br>63 |

| 2<br>3<br>4                                                        | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz                                                                                                                                                                                                                     |                      |

| 2<br>3<br>4<br>5<br>6<br>7                                         | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz                                                                                                                                                                                   |                      |

| 2<br>3<br>4<br>5<br>6                                              | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz  Bit Rate Constants, CLK = 60 MHz                                                                                                                                                 |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8                                    | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz                                                                                                                                                                                   |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                               | Transmit and Receive Interrupt Service Requests.  A and B Buffers and Chaining                                                                                                                                                                                                                                                                                                             |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                         | Transmit and Receive Interrupt Service Requests.  A and B Buffers and Chaining                                                                                                                                                                                                                                                                                                             |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                   | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz  Bit Rate Constants, CLK = 60 MHz  Data Clock Selection Using External Clock  DTE Connections  DCE Connections                                                                    |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12             | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz  Bit Rate Constants, CLK = 60 MHz  Data Clock Selection Using External Clock  DTE Connections  DCE Connections  Special Character Definition                                      |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13       | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz  Bit Rate Constants, CLK = 60 MHz  Data Clock Selection Using External Clock  DTE Connections  DCE Connections  Special Character Definition  SSPC[x] Settings                    |                      |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | Transmit and Receive Interrupt Service Requests  A and B Buffers and Chaining  Clock Source Select  Bit Rate Constants, CLK = 25 MHz  Bit Rate Constants, CLK = 30 MHz  Bit Rate Constants, CLK = 35 MHz  Bit Rate Constants, CLK = 60 MHz  Data Clock Selection Using External Clock  DTE Connections  DCE Connections  Special Character Definition  SSPC[x] Settings  SCdet[x] Settings |                      |

# **Revision History**

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | May 2001 | Initial release. |

## 1.0 Features

- Four full-duplex multi-protocol channels, each running up to 230.4 kbps (with 60-MHz clock)

- Microcode downloadable to on-chip storage supports various asynchronous and synchronous protocols on all channels

- 32-bit address, 16-bit data, double-buffered DMA (direct memory access) controller for each transmitter and receiver; two independent bit-rate generators per channel for transmit and receive

- On-chip NRZ (nonreturn-to-zero), NRZI (nonreturn-to-zero inverted), and Manchester data encoding and decoding

- DPLL (digital phase locked loop) on each receiver

- Two independent timers per channel

### **Protocols Supported**

### PPP (Point-to-Point Protocol) Features

- Supports data link level RFC-1661

- Supports dual async control character maps (32 control characters) RFC-1662

- Compatible with ISO 3309/4335 Addendum 1

- Automatic insertion/deletion of control/escape characters and bit complements

- Automatic generation and detection of 16-bit FCS (frame check sequence)

### **HDLC/SDLC (Non-Multidrop) Features**

- Four 8-bit or two 16-bit frame address matching

- FCS generation and validation

- Programmable leading-pad character transmission

- Supports shared flags on receive frames

- Programmable number of leading flags

### **Asynchronous Features**

- User-programmable and automatic flow control modes

- In-band (software) by XON/XOFF

- Out-of-band (hardware flow control) by RTS/CTS and DTR/DSR

- · Line-break detection and generation

- Special-character and character-range recognition and transmission

- Transmit delay

- 5- to 8-bit character plus optional parity

- Enhanced features for UNIX<sup>®</sup> environment

- Character expansion in transmit (for example, sending <LF> expands to <CR> <LF> automatically)

- Programmable translation of receiving character with error to different pattern

- Flow-control transparency and LNext

### MNP®4 V.42 Features

• AppleTalk® Remote Access protocol 1.0/2.0

#### **SLIP Features**

• Supports data link level — RFC-1055

### **Bisync Features**

- Supports ASCII or EBCDIC encoding

- Supports transparent Bisync

- Recognition of all special characters enabling:

- Block separation

- CRC generation and validation

- Chaining of long receive blocks into multiple buffers

#### X.21 Features

- Full support for X.21 protocol

- Detection of steady-state conditions

- Transmission of steady-state conditions synchronized to modem lead

- Programmable SYN character, 1 or 2 SYN detect option

- Idle in any line condition

### **Programmable Sync Features**

- Programmable for 5-, 6-, 7-, and 8-bit characters

- User-defined SYN (2) and EOF (4) characters

- Allows use in almost any character-sync environment

#### **DMA Controller Features**

- Dual configuration register sets to reduce realtime constraints

- · Append (async only) and Block mode DMA

- Chain/unchain long frames into multiple buffers

- 32-bit address and 8- or 16-bit data transfer

#### **Other Features**

- · Improved interrupt schemes

- Vectored interrupts per channel allow direct jump into proper service routines

- Good Data™ interrupts eliminate need for status checks

- Easily cascaded for multiple-device configurations

- 16-byte receive and transmit FIFOs

- Programmable Big- or Little-endian orientation

- Ten data / clock / modem control signals per channel

Figure 1. Functional Block Diagram

### 1.1 Benefits

- Substantially reduced host CPU overhead resulting in more channels and faster overall throughput

- No time-critical host software enabling faster and easier software development

- Smallest possible footprint for multi-channel device

#### **CD2XXX Device Family Compatibility** 1.2

| Features                                                   | CD2481                  | CD2401             | CD2431             | CD2231                 |

|------------------------------------------------------------|-------------------------|--------------------|--------------------|------------------------|

| Number of serial channels                                  | 4                       | 4                  | 4                  | 2                      |

| Interrupt on-chip DMA mechanism                            | √1                      | √                  | √                  | V                      |

| FIFO depth (per channel and per direction)                 | 16                      | 16                 | 16                 | 16                     |

| Data size (bits)                                           | 5-8                     | 5-8                | 5-8                | 5-8                    |

| Async                                                      | Downloaded <sup>2</sup> | √                  | √                  | √                      |

| HDLC/SDLC                                                  | Downloaded              | √                  | √                  | V                      |

| X.21, Bisync                                               | Downloaded              | √                  | n/a                | n/a                    |

| Async-HDLC, PPP (point-to-point protocol)                  | Downloaded              | n/a                | √                  | V                      |

| Programmable sync                                          | Downloaded              | n/a                | n/a                | n/a                    |

| Serial data rate (kbps)                                    | 230.4 <sup>3</sup>      | 134.4 <sup>4</sup> | 134.4 <sup>5</sup> | 256/230.4 <sup>6</sup> |

| Number of modem leads (per channel, including RxD and TxD) | 10                      | 10                 | 10                 | 10                     |

| On-chip timers                                             | √                       | √                  | √                  | √                      |

| UNIX® character processing                                 | Downloaded              | √                  | √                  | √                      |

| Special character Tx and recognition                       | Downloaded              | √                  | √                  | √                      |

| Package                                                    | 100-pin MQFP            | 100-pin MQFP       | 100-pin MQFP       | 100-pin MQFP           |

| Pin compatibility                                          | CD24X1                  | CD24X1             | CD24X1             | CD24X1 <sup>7</sup>    |

$<sup>1.\</sup>sqrt{}$  indicates identical operation and register setting. 2.Device microcode is not user-programmable; standard microcode is supplied by Intel.

<sup>3.</sup>Clock frequency of 60 MHz is required for 230.4 kbps. Applies to Revision B or later CD2481 devices.

<sup>4.</sup>Clock frequency of 35 MHz is required for 134.4 kbps (CD2401/CD2431); 256 kbps (sync)/230.4 kbps (async) (CD2231). 5.Clock frequency of 35 MHz is required for 134.4 kbps (CD2401/CD2431); 256 kbps (sync)/230.4 kbps (async) (CD2231).

<sup>6.</sup>Clock frequency of 35 MHz is required for 134.4 kbps (CD2401/CD2431); 256 kbps (sync)/230.4 kbps (async) (CD2231). 7.Compatible with all pins, except those supporting channels 2 and 3 on other family members. These pins are 'no connects' on the CD2231 or must be pulled up to  $V_{CC}$  through a 4.7-k $\Omega$  resistor (see the CD2481 datasheet).

## 2.0 Conventions

## 2.1 Abbreviations

| Symbol               | Units of measure                  |

|----------------------|-----------------------------------|

| °C                   | degree Celsius                    |

| μF                   | microfarad                        |

| μs                   | microsecond (1,000 nanoseconds)   |

| Hz                   | hertz (cycle per second)          |

| Kbit                 | kilobit (1,024 bits)              |

| kbits/second<br>kbps | kilobit (1,000 bits) per second   |

| Kbyte                | kilobyte (1,024 bytes)            |

| Kbytes/second        | kilobyte (1,000 bytes) per second |

| kHz                  | kilohertz                         |

| kΩ                   | kilohm                            |

| Mbyte                | megabyte (1,048,576 bytes)        |

| MHz                  | megahertz (1,000 kilohertz)       |

| mA                   | milliampere                       |

| ms                   | millisecond (1,000 microseconds)  |

| ns                   | nanosecond                        |

| pV                   | picovolt                          |

| V                    | volt                              |

| W                    | watt                              |

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

## 2.2 Acronyms

| Acronym | Definition                              |

|---------|-----------------------------------------|

| AC      | alternating current                     |

| CMOS    | complementary metal-oxide semiconductor |

| DC      | direct current                          |

| DMA     | direct-memory access                    |

| DRAM    | dynamic random-access memory            |

| FIFO    | first in/first out                      |

| HDLC    | high-level data link control            |

| ISA     | industry standard architecture          |

| LSB     | least-significant bit                   |

| MSB     | most-significant bit                    |

| PPP     | point-to-point protocol                 |

| MQFP    | plastic quad-flat pack                  |

| RAM     | random-access memory                    |

| R/W     | read/write                              |

| SDLC    | synchronous data link control           |

| TTL     | transistor-transistor logic             |

## 3.0 Pin Information

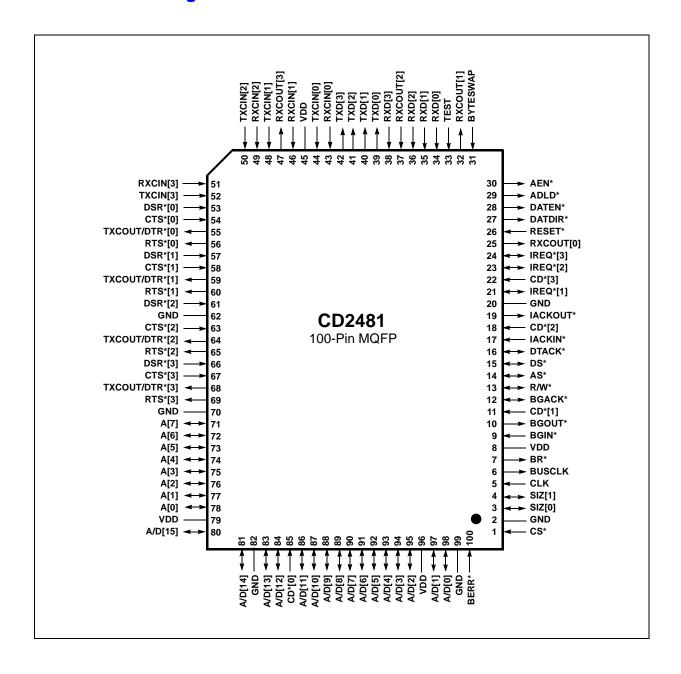

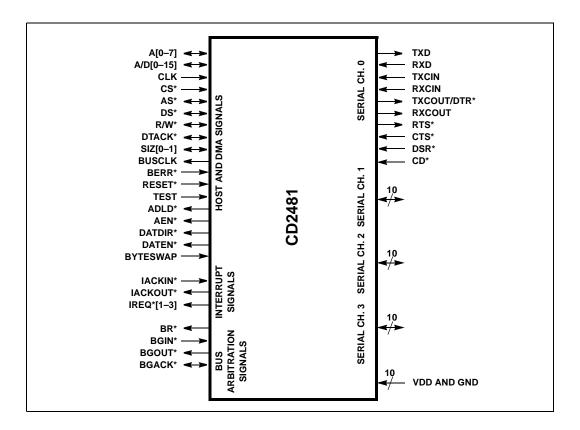

## 3.1 **Pin Diagram** — **CD2481**

## 3.2 Pin Functions — CD2481

## 3.3 Pin Descriptions

The following conventions are used in the pin-description tables:

- (\*) after a pin name indicates that the signal is active-low

- 'I' indicates the pin is input-only

- 'O' indicates the pin is output-only

- 'I/O' indicates the pin is bidirectional

- 'OD' indicates open-drain

- 'TS' indicates tristate

- '-' indicates ascending pin numbers

- ':' indicates descending pin numbers

Table 1. Pin Descriptions (Sheet 1 of 3)

| Symbol     | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS*        | I        | CHIP SELECT*: When low, the CD2481 registers may be read from or written to by the host processor.                                                                                                                                                                                                                                                                                                                 |

| AS*        | I/O (TS) | <b>ADDRESS STROBE*:</b> When the CD2481 is a bus master, this pin is an output, which indicates that R/W*, A[0–7], and the externally latched A[8–31] are valid.                                                                                                                                                                                                                                                   |

| DS*        | I/O (TS) | <b>DATA STROBE*:</b> When the CD2481 is not a bus master, this is an input used to strobe data into registers during write cycles and enable data onto the bus during read cycles. When the CD2481 is a bus master, DS* is an output used to control data transfer to and from system memory.                                                                                                                      |

| R/W*       | I/O (TS) | <b>READ/WRITE*:</b> When the CD2481 is not a bus master, this pin is an input which determines if a read or write operation is required when the CS* and DS* signals are active. When the CD2481 is a bus master, R/W* is an output and indicates whether a read from or a write to system memory is being performed.                                                                                              |

| DTACK*     | I/O (OD) | <b>DATA TRANSFER ACKNOWLEDGE*:</b> When the CD2481 is not a bus master, this is an output and indicates to the host when a read or write to the CD2481 is complete. When BR* is driven low by the CD2481, DTACK* is an input, which indicates that the system bus is no longer in use. When the CD2481 is a bus master, DTACK* is an input, which indicates when system memory read and write cycles are complete. |

| SIZ[0-1]   | I/O (TS) | SIZE [0–1]: When not the active bus master, these are inputs which determine the size of the operand being read or written by the host.  SIZ[1] SIZ[0]  0                                                                                                                                                                                                                                                          |

| IACKIN*    | I        | INTERRUPT ACKNOWLEDGE IN*: This input qualified with DS* and A[0–6] acknowledges CD2481 interrupts.                                                                                                                                                                                                                                                                                                                |

| IACKOUT*   | 0        | INTERRUPT ACKNOWLEDGE OUT*: This output is driven low during interrupt acknowledge cycles for which no internal interrupt is valid.                                                                                                                                                                                                                                                                                |

| IREQ*[1-3] | I/O (OD) | <b>INTERRUPT REQUEST*</b> [1–3]: These outputs signal that the CD2481 has a valid interrupt for modem-lead activity (IREQ*[1]), transmit activity (IREQ*[2]), or receive activity (IREQ*[3]).                                                                                                                                                                                                                      |

| BR*        | O (OD)   | <b>BUS REQUEST*:</b> This output is used to signal to the (open-drain) host processor or bus arbiter that bus mastership is required by the CD2481.                                                                                                                                                                                                                                                                |

| BGIN*      | I        | <b>BUS GRANT IN*:</b> This input indicates that the bus is available after the current bus master relinquishes the bus.                                                                                                                                                                                                                                                                                            |

| BGOUT*     | 0        | <b>BUS GRANT OUT*:</b> This output is asserted when BGIN* is low and no internal bus request has been made. A daisy-chain scheme of bus arbitration can be formed by connecting BGOUT* to BGIN* of the next device in the chain. If a priority scheme is preferred, bus requests must be prioritized externally and bus grant routed to the BGIN* of the appropriate device.                                       |

| BGACK*     | I/O (OD) | <b>BUS GRANT ACKNOWLEDGE*:</b> As an input, this signal is used to determine if another alternate bus master is in control of the bus. As an output, it signals to other bus masters that this device is in control of the bus.                                                                                                                                                                                    |

Table 1.

Pin Descriptions (Sheet 2 of 3)

| Symbol      | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BERR*       | I        | <b>BUS ERROR*:</b> If this input becomes active while the CD2481 is a bus master, the current bus cycle will be terminated, the bus relinquished, and an interrupt generated to indicate the error to the host processor.                                                                                                                                                                                                                                                                                                                                                                                                         |

| A[0-7]      | I/O (TS) | ADDRESS [0–7]: When the CD2481 is not a bus master, these pins are inputs used to determine which registers are being accessed, or which interrupt is being acknowledged. When ADLD* is low, A[0–7] output address bits 8–15 for external latching. When the CD2481 is a bus master, A[0–7] output the least-significant byte of the transfer address.                                                                                                                                                                                                                                                                            |

| A/D[0-15]   | I/O (TS) | ADDRESS/DATA [0–15]: When the CD2481 is not a bus master, these pins provide the 16-bit data bus for reading and writing to the CD2481 registers. When ADLD* is low, A/D[0–15] provide the upper address bits for external latching. When the CD2481 is a bus master, A/D[0–15] provide a multiplexed address/data bus for reading and writing to system memory.                                                                                                                                                                                                                                                                  |

| ADLD*       | O (TS)   | ADDRESS LOAD*: This is a strobe used to externally latch the upper portion of the system address bus A[8–31]. While ADLD* is low, address bits 16–31 are available on A/D[0–15], and address bits 8–15 on A[0–7].                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AEN*        | O (TS)   | ADDRESS ENABLE*: This output is used to output enable the external address bus drivers during CD2481 DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DATEN*      | O (TS)   | <b>DATA ENABLE*:</b> This output is active when either the CD2481 is a bus master, or the CS* and DS* pins are low. It is used to enable the external data bus buffers during host register read/ write operations or during DMA operations. For operations on 32-bit buses, this signal needs to be gated with A[1] to select the correct half of the data bus.                                                                                                                                                                                                                                                                  |

| DATDIR*     | O (TS)   | <b>DATA DIRECTION*:</b> This output is active when either the CD2481 is a bus master, or the CS* pin is low. It is used to control the external data buffers; when low, the buffers should be enabled in the CD2481 to system bus direction.                                                                                                                                                                                                                                                                                                                                                                                      |

| CLK         | I        | CLOCK: System clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BUSCLK      | 0        | <b>BUS CLOCK:</b> This is the system clock divided by two, which is used internally to control certain bus operations. This pin is driven low during hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RESET*      | I        | <b>RESET*:</b> This signal should stay valid for a minimum of 20 ns. The reset state of the CD2481 will be guaranteed at the rising edge of this signal. When RESET* is removed, the CD2481 also performs a software initialization of its registers.                                                                                                                                                                                                                                                                                                                                                                             |

| TEST        | ı        | <b>TEST:</b> In normal operation, this pin should be kept low. For board-level testing purposes, it provides a mechanism for forcing normal output pins to High-Impedance mode. When the TEST pin is high, the following pins will be in High-Impedance mode: BUSCLK, BGOUT*, IACKOUT*, RXCOUT[0–3], RTS*[0–3], DTR*[0–3], and TXD[0–3].                                                                                                                                                                                                                                                                                          |

| 1201        |          | To ensure that all CD2481 outputs are high-impedance, either of the following two conditions must be met: the RESET* pin can be driven low, and the TEST pin driven high; or the CD2481 is kept in the bus idle state (not accessed for read/write operations nor DMA active), and the TEST pin is driven high.                                                                                                                                                                                                                                                                                                                   |

| RTS*[0-3]   | 0        | <b>REQUEST TO SEND* [0–3]:</b> This output can be controlled automatically by the CD2481 to indicate that data is ready to be sent on the TXD pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TXCOUT/DTR* | 0        | TRANSMIT CLOCK OUT/DATA TERMINAL READY* [0–3]: This output can be controlled automatically by the CD2481 to indicate that a programmable threshold has been reached in the receive FIFO. It can also be programmed to output the transmit data clock. Following reset, this pin will be high and stays high in Clock mode until the transmit channel is enabled for the first time; after that it remains active independent of the state of the transmit enable. In all modes, the clock transitions every bit time, even during idle fill in Asynchronous mode. Data transitions are made on the negative going edge of TXCOUT. |

| RXCOUT[0-3] | 0        | RECEIVE CLOCK OUT [0–3]: This output provides a one-time bit rate clock for the receive data in all modes, except when an input (RXCIN) one-time receive clock is used. After reset, this pin will be low until the channel is receive enabled for the first time, after which it remains active, independent of the state of receive-enable. When in Asynchronous mode, the output only transitions while receiving data and not during inter-character fill. The receive data is sampled on the positive-going edge of this clock.                                                                                              |

## Programmable Four-Channel Communications Controller — CD2481

**Table 1. Pin Descriptions** (Sheet 3 of 3)

| Symbol    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CTS*[0-3] | 1    | CLEAR TO SEND* [0–3]: This input can be programmed to control the flow of transmit data, for out-of-band flow control applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| TXCIN     | I    | TRANSMIT CLOCK: This pin inputs the transmit clock to the bit rate generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| CD*       | 1    | <b>CARRIER DETECT*</b> : This pin is always visible in the MSVR register. CD* is a general purpose modem input and can be used to cause modem group interrupts upon signal level transitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| RXCIN     | I    | RECEIVE CLOCK: This pin inputs the receive clock to the bit rate generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| DSR*      | 1    | <b>DATA SET READY*</b> : This pin is always visible in the MSVR register. DSR* can be used to validate receive data as well as cause modem group interrupts upon signal level transitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| TXD[0-3]  | 0    | TRANSMIT DATA [0-3]: Serial data output for each channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| RXD[0-3]  | I    | RECEIVE DATA [0-3]: Serial data input for each channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| BYTESWAP  | 1    | BYTESWAP: This pin alters the byte ordering of data during certain 16-bit transfers. It also changes that half of the data bus on which byte transfers are made, to comply with Intel® or Motorola® processor systems. BYTESWAP does not alter the bus handshake signals. When the BYTESWAP pin is high, the byte on A/D[0–7] precedes that on A/D[8–15] in a string of transmit or receive bytes. When BYTESWAP is low, A/D[8–15] precedes A/D[0–7]. When the BYTESWAP pin is high, bytes are transferred on A/D[0–7] when A[0] is low, and on A/D[8–15] when A[0] is high. When BYTESWAP is low, bytes are transferred on A/D[8–15] when A[0] is low, and A/D[0–7] when A[0] is high. A different register map is used, depending on the state of this pin.  Byteswap Byte Alignment  0 Motorola byte alignment  1 Intel byte alignment |  |

## 4.0 Register Summaries

Registers in the CD2481 are either Global or Per-Channel. The column 'Address mode' in the memory map on the following pages defines this attribute for each register. Only one set of Global registers exists, and is accessible by the host at any time. Two sets of Per-Channel registers exist, and the set accessible at any one time is determined by the currently active channel number. The channel number is selected by the host in normal (non-interrupt) processing by writing to the Channel Access register. The channel number in the Channel Access register remains in force until changed by the host. The channel number is provided automatically by the CD2481 during interrupt service routines and DMA transfers.

In the following list, some register locations appear twice. They have different names and functions for asynchronous and synchronous protocol operations. See Chapter 9.0 on page 112 on of this datasheet for detailed descriptions of all register functions.

Note also that not all registers are valid at any one time, depending on which functions are included in the microcode image which has been downloaded. Please refer to end-company dependent documentation for descriptions of the microcode images.

## 4.1 Memory Map

### 4.1.1 Global Registers

| Name  | Description                            | Addr.<br>Mode <sup>1</sup> | INT <sup>2</sup> | MOT <sup>3</sup> | Size | Access | Page |

|-------|----------------------------------------|----------------------------|------------------|------------------|------|--------|------|

| GFRCR | Global Firmware Revision Code Register | G                          | 82               | 81               | В    | R/W    | 112  |

| CAR   | Channel Access Register                | G                          | EC               | EE               | В    | R/W    | 112  |

The following notes are applicable for Section 4.1.1 through Section 4.1.7.

#### NOTES:

- Address mode G: Global register one set is always accessible.

Address mode P: Per-Channel register four sets, one per channel, accessible by CAR or interrupt context.