# **PN7220**

# NFC controller with NCI interface supporting EMV and NFC Forum applications

Rev. 3.0 — 5 July 2023

Product data sheet

# 1 General description

This document describes the functionality and electrical specification of the PN7220 high-power NFC controller family with NCI interface.

As an NCI 2.2 compliant NFC controller with high RF output (2 W) and high receiver sensitivity, the NXP PN7220 is a robust solution for payment terminals and all readers that must generate a strong RF field in a difficult environment. Offering full compliance with EMVCo 3.1 L1 analog and digital, the PN7220 simplifies designs while ensuring interoperability with a broad range of smartcards and mobile phones.

In addition to the reader/writer functionality, the device supports the emulation of ISO14443-A cards up to 848 kbit/s.

The PN7221 is based on the PN7220 and supports all features of PN7220 plus "Enhanced Contactless Polling" (ECP) by Apple (see Ref. [12]) - this description is not part of this document. Note, that the ECP feature is available after formal authorization only.

The PN7220 communicates to a connected host by a physical I<sup>2</sup>C interface using the NCI 2.2 protocol.

The PN7221 communicates to a connected host by a physical I<sup>2</sup>C interface using the NCI 2.2 protocol and supports Apple ECP.

#### Planned, but not available yet:

The PN7222 communicates to a connected host by one physical I<sup>2</sup>C interface using the NCI 2.2 protocol and one dedicated SPI interface.

The PN7223 communicates to a connected host by one physical I<sup>2</sup>C interface using the NCI 2.2 protocol and one dedicated SPI interface and supports Apple ECP.

The PN7220 product family supports highly innovative and unique features which do not require any host controller interaction. These features include dynamic power control (DPC), adaptive waveform control (AWC), and fully automatic EMD error handling.

Additional documents supporting a design-in of the are available from NXP, this additional design-in information is not part of this document.

In this document, the term "MIFARE card" refers to a contactless card with an embedded MIFARE IC.

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 2 Features and benefits

## 2.1 RF functionality

#### 2.1.1 ISO/IEC14443-A

Reader/writer mode supporting ISO/IEC 14443-A R/W up to 848 kbit/s

#### 2.1.2 ISO/IEC 14443-B

Reader/writer mode supporting ISO/IEC 14443-B up to 848 kbit/s

#### 2.1.3 FeliCa

Reader/writer mode supporting FeliCa 212 kbit/s and 424 kbit/s (without crypto)

#### 2.1.4 Tag type reading

Supports reading of all NFC tag types (type 2, type 3, type 4A and type 4B, type 5)

#### 2.1.5 MIFARE card reading

Reader/writer communication mode for the MIFARE card family including MIFARE Classic Crypto supporting MIFARE Classic en-/decryption is integrated in hardware

#### 2.1.6 ISO/IEC 15693

- Reader/writer mode supporting ISO/IEC 15693 (ICODE)

- RX: "Manchester" encoding with 424 kHz single-subcarrier (SSC) and 6.6 kBd

- RX: "Manchester" encoding with 424 kHz single-subcarrier (SSC) and 26 kBd

- RX: "Manchester" encoding with 424 kHz single-subcarrier (SSC) and 53 kBd

- TX: "1 of 4" encoding with 10 % modulation (53 kBd)

- TX: "1 of 4" encoding with 100 % modulation (53 kBd).

#### 2.1.7 NFC Forum compliancy

• NFC Forum compliance for R/W - analog and digital

#### 2.1.8 EMVCo compliancy

- EMVCo 3.1 compliance for R/W digital

- EMVCo 3.1 compliance for R/W analog can be achieved, but depends on connected antenna geometry and size, matching network and RF settings.

#### 2.1.9 Host interface

The devices PN7220 and PN7221 support one host interface using a single interface connection based on a I<sup>2</sup>C interface host interface (host interface 1) with data rates up to 3.4 Mbit/s.

The logical interface layer of the host interfaces is based on the NCI 2.0 interface specification, enhanced by NXP proprietary commands.

PN7220

All information provided in this document is subject to legal disclaimers.

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

The devices PN7222 and PN7223 support two host interfaces using one interface connection based on a I<sup>2</sup>C interface (host interface 2) and one SPI interface (host interface 1).

#### 2.2 Transmitter

- Transmitter with high RF output power of 2.0 W

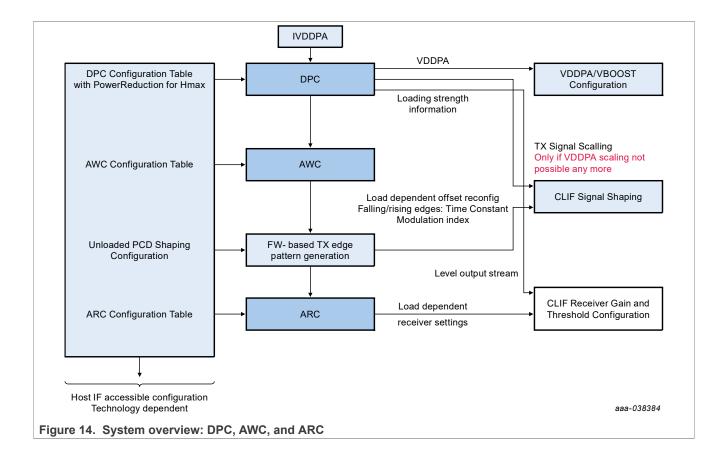

- Dynamic power control 2.0 (DPC) (dynamic power control without processing load on host MCU)

- Adaptive waveshaping control (AWC)

#### 2.3 Receiver

Robust receiver: Automatic configuration, advanced insensitivity against TFT display noise for higher RF performance

# 2.4 Integrated polling loop

- · RF polling loop according to NFC Forum

- RF Polling loop according to EMVCo 3.1, integrated EMVCo L1 software stack

- Integrated EMVCo L1 contact stack

# 2.5 Integrated DC-DC

The PN7220 implements an integrated DC-DC which can be used to supply the transmitter. Since the supply voltage of the transmitter LDO can be up to 6.0 Volts, this simplifies the design of the power supply.

A single supply concept for the RF system, for example, with single 3.3 V supply, is possible and allows making use of the maximum RF output power by providing a maximum transmitter supply voltage.

The integrated DC-DC is used by the dynamic power control (DPC) to reduce the maximum power dissipation of the chip.

The usage of the DC-DC is optional.

For applications making use of the low-power card detection, the DC-DC is available.

# 2.6 RF debugging support

- RF debugging without external probing of test signals possible by sampling debug data into chip-internal memory based on pre-define trigger conditions ideal debugging solution for PCI-compliant POS terminals

- · One digital and one analog debug signal is provided by the chip for connection of an oscilloscope

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 3 Applications

- Payment terminals following the COTS security requirements with full EMVCo3.1 analog and digital compliancy

- Multi-Application terminals

- Ticket validators for the controlling staff in public transport

- E-Vehicle charging stations

- · Vending machines

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 4 Quick reference data

Table 1. Quick reference data

| Symbol                 | Parameter                                                              | Conditions                                                                                                                                                                          | Min  | Тур | Max  | Unit |

|------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| VDD <sub>(VBAT)</sub>  | supply voltage on pin VBAT (analog and digital supply)                 | VBAT ≥ VDDIO                                                                                                                                                                        | 2.4  | -   | 5.5  | V    |

| VDD <sub>(VDDIO)</sub> | supply voltage on pin VDDIO                                            | 1.8 V supply                                                                                                                                                                        | 1.62 | -   | 1.98 | V    |

|                        | (supply for host interface and GPIOs)                                  | 3.3 V supply                                                                                                                                                                        | 2.4  | -   | 3.6  | V    |

| VDD <sub>(VDDPA)</sub> | supply voltage on pin VDDPA (input of the transmitter power amplifier) | PN7220 - supply with VDDPA from internal VDDPALDO with DC-DC                                                                                                                        | 1.5  | -   | 5.7  | V    |

| pd                     | power down current                                                     | VDD <sub>(VDDPA)</sub> = VDD <sub>(VDDIO)</sub><br>=VDD <sub>(VDD)</sub> 3.0 V; hard power<br>down state; pin VEN set LOW,<br>T <sub>amb</sub> = 25 °C, External supply by<br>VDDIO | -    | 40  | 105  | μА   |

| stb                    | standby current                                                        | T <sub>amb</sub> = 25 °C                                                                                                                                                            | -    | 45  | 110  | μΑ   |

| IDD <sub>(VDDPA)</sub> | supply current on pin VDDPA                                            | supplied via VUP_TX (TX_LDO active)                                                                                                                                                 | -    | -   | 350  | mA   |

|                        |                                                                        | supplied without DC-DC and TXLDO active                                                                                                                                             | -    | -   | 400  | mA   |

| P <sub>(PA)</sub>      | transmitter output power                                               | supplied via VUP_TX (TX_LDO active)                                                                                                                                                 | -    | -   | 2.0  | W    |

|                        |                                                                        | supplied without DC-DC and TXLDO active                                                                                                                                             | -    | -   | 2.3  | W    |

| $\Gamma_{ m amb}$      | ambient operating temperature                                          | in still air with exposed pins soldered on a 4 layer JEDEC PCB,                                                                                                                     | -40  | -   | +85  | °C   |

| $\Gamma_{ m amb}$      | ambient operating temperature                                          | in still air with exposed pins soldered on a 4 layer JEDEC PCB,                                                                                                                     | -40  | -   | +85  | °C   |

|                        |                                                                        | in still air with exposed pins<br>soldered on a 4 layer JEDEC PCB,<br>TX current = 120 mA @ VDDPA =<br>3.6 V                                                                        | -40  | -   | +105 | °C   |

| Γ <sub>stg</sub>       | storage temperature                                                    | no supply voltage applied                                                                                                                                                           | -55  | -   | +150 | °C   |

| Γ <sub>j_max</sub>     | maximum junction temperature                                           | -                                                                                                                                                                                   | -    | -   | +125 | °C   |

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 5 Ordering information

Table 2. Ordering information

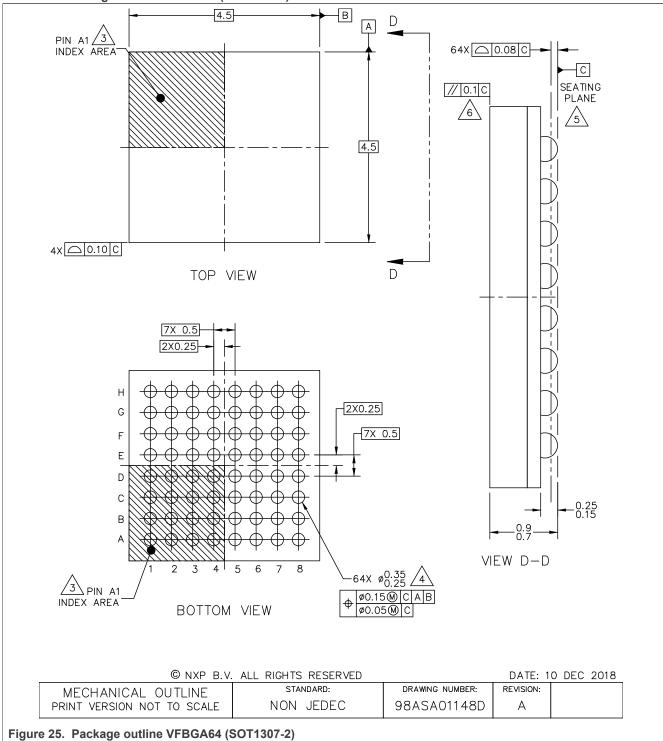

| Type number  | Package |                                                                                                                                                                                                                                                                                                                                 |           |  |  |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|              | Name    | Description                                                                                                                                                                                                                                                                                                                     | Version   |  |  |

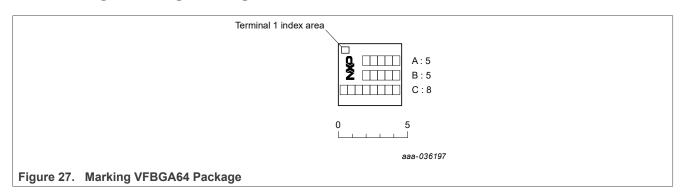

| PN7220EV/C1  | VFBGA64 | Plastic thin fine-pitch ball grid array package; 64 balls, body 4.5 x 4.5 x 0.9 mm, delivered in 5 trays, MSL = 3. Minimum order quantity = 5 x 490 pcs The ending "K" in the product name is indicating the packing "multiple tray"; 12NC (order number) ending - 557 Version for connection to 1 host microcontroller         | SOT1307-2 |  |  |

| PN7220EV/C1J | VFBGA64 | Plastic thin fine-pitch ball grid array package; 64 balls, body 4.5 x 4.5 x 0.9 mm, delivered on reel 13", MSL = 3. Minimum order quantity = 4000 pcs  The ending Y in the product name is indicating the packing "reel"; 12NC (order number) ending - 518  Version for connection to 1 host microcontroller                    | SOT1307-2 |  |  |

| PN7221EV/C1  | VFBGA64 | Plastic thin fine-pitch ball grid array package; 64 balls, body 4.5 x 4.5 x 0.9 mm, delivered in 5 trays, MSL = 3. Minimum order quantity = 5 x 490 pcs The ending "K" in the product name is indicating the packing "multiple tray"; 12NC (order number) ending - 557 Version for connection to 1 host microcontroller and ECP | SOT1307-2 |  |  |

| PN7221EV/C1J | VFBGA64 | Plastic thin fine-pitch ball grid array package; 64 balls, body 4.5 x 4.5 x 0.9 mm, delivered on reel 13", MSL = 3. Minimum order quantity = 4000 pcs  The ending Y in the product name is indicating the packing "reel"; 12NC (order number) ending - 518  Version for connection to 1 host microcontroller and ECP            | SOT1307-2 |  |  |

# NFC controller with NCI interface supporting EMV and NFC Forum applications

# 6 Block diagram

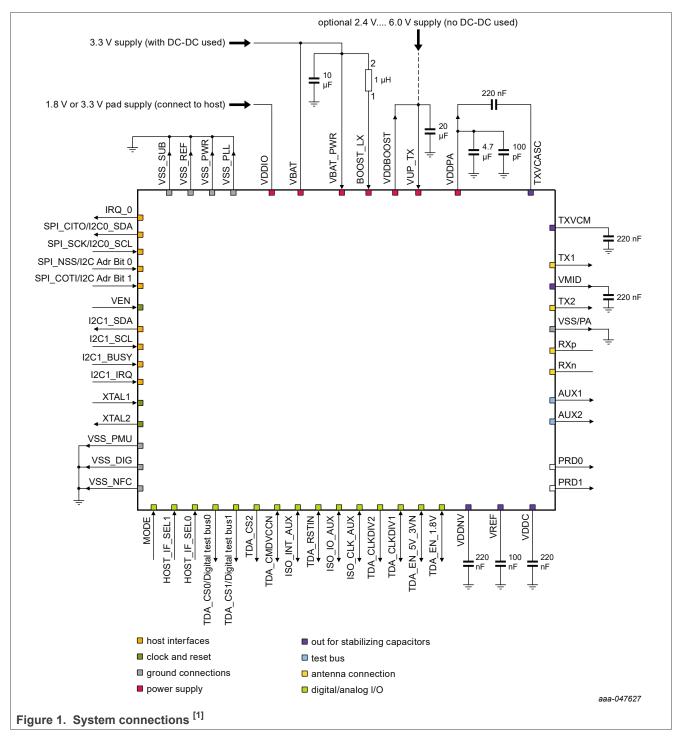

[1] The replacement of "MOSI/MISO" to "COTI/CITO" in this document follows the recommendation of the NXP - I<sup>2</sup>C standards organization.

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

The PN7220 is connected to an application processor / host CPU based on an NCI interface.

The device offers high compatibility to existing solutions which offer an NCI interface (Host IF\_1). The physical interface used for the connection is a I2C interface.

Host IF 1 allows I<sup>2</sup>C data rates up to 3.4 Mbit/s.

#### I<sup>2</sup>C address:

The PN7220 host interface 1 supports the 7-bit addressing mode, first 5-bits are fixed and is decimal 40, last two bits are configurable using ADDR0 and ADDR1 pins. This provides maximum flexibility even in cases where the  $I^2$ C bus is shared with other devices on top of the PN7220.

#### Default mode after boot:

The system is always booting in mode (EMVCo polling or NFC Forum polling) defined by the level on the pin MODE/GPIO2.

#### Switching between NFC Forum and EMVCo polling:

Switching to a EMVCo polling loop is done based on a physical signal "MODE/GPIO2" controlled by the application processor / host CPU. All previous data from earlier communications are erased, and the NCI software stack is being reset. The system enters then the new EMVCo polling mode. Switching back to NFC Forum mode again clears all previous data from earlier communication and resets the NCI software stack.

NFC controller with NCI interface supporting EMV and NFC Forum applications

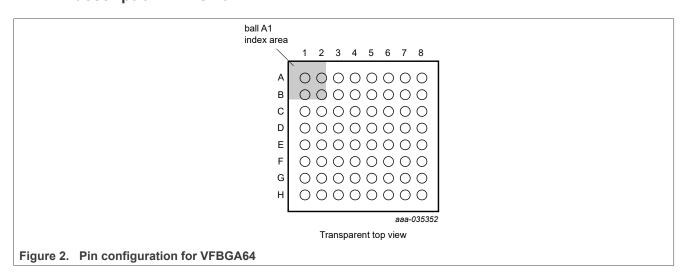

# 7 Pinning information

# 7.1 Pin description VFBGA64

Table 3. Pin description VFBGA64

| Pin Number                                | Symbol <sup>[1]</sup>       | Туре         | Description [1]                                                                                                                                                                                                                                        |

|-------------------------------------------|-----------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface 1 (I <sup>2</sup> C / SPI) |                             |              |                                                                                                                                                                                                                                                        |

| SPI CITO / I2C1_ Output SDA               |                             | Output       | PN7220 / PN7221: I <sup>2</sup> C1_ SDA                                                                                                                                                                                                                |

|                                           |                             |              | PN7222 / PN7223: SPI CITO                                                                                                                                                                                                                              |

| E5                                        | SPI SCK / I2C1_<br>SCL      | Input        | PN7220 / PN7221: I <sup>2</sup> C1_SCL                                                                                                                                                                                                                 |

|                                           |                             |              | PN7222 / PN7223: SPI SCK                                                                                                                                                                                                                               |

| D6                                        | SPI NSS / I2C<br>Adr Bit 0  | Input        | PN7220 / PN7221: I <sup>2</sup> C Adr Bit 0 (Address is configured using 5 fixed bits (40d - 028h ) and 2 Bits from D5/D6) I <sup>2</sup> C interface address can be configured to 0x28 (00), 0x29 (01), 0x2A (10), 0x2B (11) based on D6 and D5 Pins  |

|                                           |                             |              | PN7222 / PN7223: SPI NSS                                                                                                                                                                                                                               |

| D5                                        | SPI COTI / I2C<br>Adr Bit 1 | Input        | PN7220 / PN7221: I <sup>2</sup> C Adr Bit 1 ((Address is configured using 5 fixed bits (40d - 028h ) and 2 Bits from D5/D6) I <sup>2</sup> C interface address can be configured to 0x28 (00), 0x29 (01), 0x2A (10), 0x2B (11) based on D6 and D5 Pins |

|                                           |                             |              | PN7222 / PN7223: SPI COTI                                                                                                                                                                                                                              |

| B7                                        | IRQ1                        | Output       | Host communication IF1 / event interrupt signal                                                                                                                                                                                                        |

| Host Interface                            | 2 (I2C)                     |              |                                                                                                                                                                                                                                                        |

| A6                                        | I2C2_SDA                    | Input/Output | PN7220 / PN7221: n.c.                                                                                                                                                                                                                                  |

|                                           |                             |              | PN7222 / PN7223: I <sup>2</sup> C 2 SDA                                                                                                                                                                                                                |

# NFC controller with NCI interface supporting EMV and NFC Forum applications

Table 3. Pin description VFBGA64...continued

| Pin Number                              | Symbol <sup>[1]</sup> | Туре       | Description <sup>[1]</sup>                                                                                                       |

|-----------------------------------------|-----------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| B6                                      | I2C2_SCL              | Input      | PN7220 / PN7221: n.c.                                                                                                            |

|                                         |                       |            | PN7222 / PN7223: I <sup>2</sup> C 2 SCL                                                                                          |

| D7                                      | WAKEUP                | input      | PN7220 / PN7221: n.c. ; Wakeup signal for 2 CPU system                                                                           |

|                                         |                       |            | PN7222 / PN7223: BUSY host Interface 2                                                                                           |

| H8                                      | I2C2_IRQ              | Output     | PN7220 / PN7221: n.c.                                                                                                            |

|                                         |                       |            | PN7222 / PN7223: Host communication interface 2 event interrupt signal                                                           |

| Hardware reset                          | i i                   |            |                                                                                                                                  |

| B3                                      | VEN                   | Input      | Hardware reset, low active (independent from V <sub>VDDIO</sub> )                                                                |

| Host interface<br>and Mode<br>selection |                       |            |                                                                                                                                  |

| E7                                      | MODE                  | Input      | Mode selection (EMVCo or NFC Forum polling loop)                                                                                 |

|                                         |                       |            | Input H: EMVCo polling mode Input L: NFC Forum polling mode                                                                      |

|                                         |                       |            | Input defines always EMVCo or NFC Forum polling loop, but the used host interface is different dependent on configuration of C7: |

|                                         |                       |            | C7= H at boot (1 CPU system): NFC Forum and EMVCo polling loop data transfer is done always using host inerface 1                |

|                                         |                       |            | C7 = L at boot (2 CPU system): NFC Forum polling loop is doing                                                                   |

|                                         |                       |            | data transfer using host interface 2 and EMVCo polling loop is doing data transfer using host interface 1                        |

| C6                                      | HOST_IF_SEL1          | Input      | Shall always be on GND on PN7220                                                                                                 |

| C7                                      | HOST_IF_SEL0          | Input      | Host interface select 0 - selection of 1 or 2 CPU system                                                                         |

|                                         |                       |            | 0: Host Interface1 active after boot (I2C Host Interface 2 has no function)                                                      |

|                                         |                       |            | 1: Host Interface 2 is always active after boot, SPI Interface 1 is active only after selecting EMVCo mode on E7 - MODE/GPIO2    |

|                                         |                       |            | HIF_SEL0 pin is read by FW after POR or reset via VEN or boot from low-power mode (OFF, standby, LPCD etc.).                     |

| XTAL connection                         | on                    |            |                                                                                                                                  |

| F8                                      | XTAL1                 | Input      | Crystal / system clock input                                                                                                     |

| G8                                      | XTAL2                 | Output     | Clock output (amplifier-inverted signal output) for crystal                                                                      |

| Supply pins                             |                       |            |                                                                                                                                  |

| H2                                      | VSS_PA                | Supply GND | Transmitter ground                                                                                                               |

| G3                                      | VSS_PLL               | Supply GND | PLL ground (low noise)                                                                                                           |

| A2                                      | VSS_PWR               | Supply GND | DC-DC boost ground                                                                                                               |

| D3                                      | VSS_REF               | Supply GND | PMU ground                                                                                                                       |

| B2, E3                                  | VSS_SUB               | Supply GND | Substrate ground                                                                                                                 |

| C3                                      | VSS_PMU               | Supply GND | PMU ground                                                                                                                       |

| F4                                      | VSS_DIG               | Supply GND | Digital ground                                                                                                                   |

| F3                                      | VSS_NFC               | Supply GND | NFC ground                                                                                                                       |

PN7220

All information provided in this document is subject to legal disclaimers.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

Table 3. Pin description VFBGA64...continued

| Pin Number    | Symbol <sup>[1]</sup> | Туре             | Description [1]                                                                                                                                   |  |  |

|---------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| E1            | VBAT                  | Supply           | System supply, used to supply the analog and digital blocks, memory and internal voltage references                                               |  |  |

| A8            | VDDIO                 | Supply           | I/O pads power supply                                                                                                                             |  |  |

| G1            | VDDPA                 | Supply           | Transmitter supply                                                                                                                                |  |  |

| F1            | VUP_TX                | Supply           | Input supply voltage for transmitter LDO                                                                                                          |  |  |

| B1            | VDDBOOST              | Supply           | DC-DC boost supply                                                                                                                                |  |  |

| A1            | BOOST_LX              | Output           | Boost inductance loopback, to be connected to boost inductor                                                                                      |  |  |

| A3            | VBATPWR               | Supply           | To be connected to boost inductor and transmitter power supply                                                                                    |  |  |

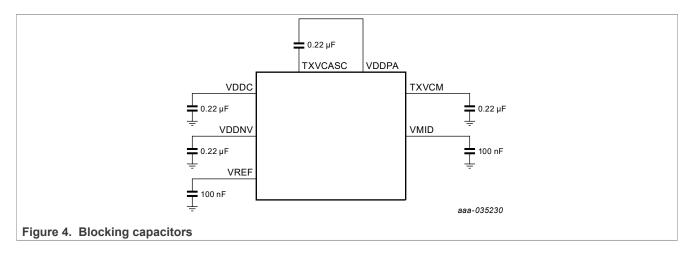

| Outputs for s | tabilizing cap        |                  |                                                                                                                                                   |  |  |

| A4            | VDDNV                 | Output           | Non-volatile memory power supply, to be connected to ground via 220 nF blocking cap                                                               |  |  |

| D2            | VREF                  | Output           | High quiescent reference voltage, to be connected to ground via 100 nF blocking cap                                                               |  |  |

| C1            | VDDC                  | Output           | Power supply for Digital Core, to be connected to ground via 220 nF blocking cap                                                                  |  |  |

| G2            | TXVCM                 | Output           | Transmitter voltage common mode, to be connected to ground via 220 nF blocking cap                                                                |  |  |

| F2            | TXVCASC               | Output           | TX decoupling cap, to be connected to VDDPA                                                                                                       |  |  |

| H6            | VMID                  | Output           | Stabilizing capacitor connection output, to be connected to electrical symmetry point of antenna (typically antenna ground by 100 nF blocking cap |  |  |

| RF Debug sig  | nals                  | <del>-</del>     |                                                                                                                                                   |  |  |

| G7            | AUX_1                 | Output           | Test bus 1                                                                                                                                        |  |  |

| F7            | AUX_2                 | Output           | Test bus 2                                                                                                                                        |  |  |

| Antenna con   | nections              |                  |                                                                                                                                                   |  |  |

| H5            | RXP                   | Input            | Receiver input "Positive"                                                                                                                         |  |  |

| H4            | RXN                   | Input            | Receiver input "Negative"                                                                                                                         |  |  |

| H1            | TX1                   | Output           | Antenna driver output 1                                                                                                                           |  |  |

| H3            | TX2                   | Output           | Antenna driver output 2                                                                                                                           |  |  |

| Analog/Digita | al inputs and output  | s                |                                                                                                                                                   |  |  |

| E8            | TDA_CS0 /<br>GPIO0    | Output           | Digital test bus0 / TDA chip select 0                                                                                                             |  |  |

| D8            | TDA_CS1 /<br>GPIO1    | Output           | Digital test bus1 / TDA chip select 1                                                                                                             |  |  |

| Security Feat | ure                   | ,                |                                                                                                                                                   |  |  |

| B4            | PRD1                  | Input/<br>Output | Package removal detection, internally connected to PRD2                                                                                           |  |  |

| G4            | PRD2                  | Input/<br>Output | Package removal detection, internally connected to PRD1                                                                                           |  |  |

# NFC controller with NCI interface supporting EMV and NFC Forum applications

Table 3. Pin description VFBGA64...continued

| Pin Number     | Symbol <sup>[1]</sup>       | Туре           | Description [1]                                                                                                                          |

|----------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| TDA8035 Interf | face                        |                |                                                                                                                                          |

| A7             | TDA_CS2                     | Output         | TDA chip select 2 (TDA_CS2)  Note: Pulldown resistor required. EEPRM configuration to configure as TDA_CS. Default is TDA_CS = disabled. |

| B5             | TDA_<br>CMDVCCN /<br>GPIO5  | Input/Output   | TDA_CMDVCCN                                                                                                                              |

| C4             | ISO_INT_AUX                 | Input/Output   | Auxiliary Card Interrupt                                                                                                                 |

| C5             | TDA_RSTIN /<br>GPIO4        | Input/Output   | TDA_RSTIN                                                                                                                                |

| D4             | ISO_IO_AUX                  | Input/Output   | Auxiliary Card I/O                                                                                                                       |

| E4             | ISO_CLK_AUX                 | Input          | Auxiliary Card Clock                                                                                                                     |

| F5             | TDA_CLKDIV2 /<br>SPIM_COTI  | Input          | TDA_CLKDIV2                                                                                                                              |

| F6             | TDA_CLKDIV1 /<br>SPIM_CITO  | Input / Output | TDA_CLKDIV1                                                                                                                              |

| G5             | SPIM_SCLK /<br>TDA_EN_5V_3V | Input / Output | TDA_EN5V_3V                                                                                                                              |

| G6             | SPIM_SSN /<br>TDA_EN_1.8V   | Input / Output | TDA_EN_1.8V                                                                                                                              |

| Pins not to be | connected                   |                |                                                                                                                                          |

| A5             | PVDD_OUT                    | Output         | Do not connect                                                                                                                           |

| B8             | SWDIO                       | Input/Output   | Do not connect                                                                                                                           |

| C2             | TEST                        | Input/Output   | Do not connect.                                                                                                                          |

| C8             | SWD_CLK                     | Input          | Do not connect                                                                                                                           |

| D1             | USB_VBUS                    | Supply         | Do not connect                                                                                                                           |

| E2             | AD1                         | Input          | Do not connect                                                                                                                           |

| H7             | VTUNE1                      | Output         | Do not connect                                                                                                                           |

<sup>[1]</sup> The replacement of "MOSI/MISO" to "COTI/CITO" in this document follows the recommendation of the NXP - I2C standards organization.

For good RF performance, all blocking capacitors shall be placed on the same side of the PCB, traces from pin to capacitor shall be as short as possible.

All Supply GND connections shall be connected by low-ohmic connections on the PCB.

PN7220 is a planned product, the pin allocation is provided for information only.

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 8 Functional description

PN7220 can be connected on a host controller through the physical Pulldown resistor required. EEPRM configuration to configure as TDA\_CS. Default is TDA\_CS = disabled. interface. The logical interface toward the host controller is NCI 2.0-compliant Ref. [2] with additional commands for NXP-specific product features.

The device implements an EMVCo3.1 compliant polling loop and allows to be compliant to EMVCo L1 digital.

Enhanced RF debugging and easy configuration are supported by usage of the SPI interface, analog and digital debug outputs (AUX) and the CLIF test station.

#### 8.1 Functional overview

The PN7220 is an NFC controller with high transmitter output power. It implements the RF functionality like an antenna driving and receiver circuitry and all the low-level functionality to realize an NFC Forum and EMVCo compliant reader.

#### Connection to host controller

The PN7220 connects to a host microcontroller with a I2C interface for configuration, NFC data exchange, and a high-level NCI 2.0 protocol implementation extended by proprietary commands.

The processing of the NCI commands had been improved on the PN7220 compared to previous NFC reader generations with NCI interface which eases the meeting of EMVCo timing requirements.

#### Integrated EMVCo3.1 L1 polling loop

The PN7220 implements an integrated EMVCo3.1 PCD-compliant polling loop. The polling loop can be configured to poll as well for FeliCa compliant cards following the EMVCo specification for "other technologies". Alternatively, the device can be configured to poll for FeliCa cards exclusively. In addition, the PN7221 allows to configure the ECP. The firmware of the device had been optimized for low latency which helps to achieve the EMVCo timing requirements even with Android-based host systems.

#### Integrated NFC Forum polling loop

All supported RF technologies can be independently enabled within this PCD polling loop. The sequence of RF technologies within the PCD polling loop cannot be modified.

#### Selection of dedicated polling loop NFC Forum or EMVCo

The selection of a dedicated polling loop is done based on a hardware input "MODE".

After reset, the polling loop which can be activated depends on the MODE selection. It can be either EMVCo or NFC Forum compliant pollinig.

Switching the polling loop from one mode to the other is done by changing the level of the MODE input pin. Switching from NFC Forum polling mode to the EMVCo polling mode resets the NCI stack, clears all data in the buffers, performs an RF reset and allows then to activate the polling according to EMVCo 3.1. Switching back to the NFC Forum polling mode, again reset resets the NCI stack, performs an RF reset, clears all data in the buffers and is ready to receive NCI Interface commands to activate NFC Forum polling.

In addition to the selection of the polling loop, the mode activates a dedicated user defined set of RF configuration parameters. With this, a different RF behaviour for EMVco and NFC Forum can be realized.

This switching of modes based on an external mode pin is working faster than alternative solutions based on loading configuration files, and allows a more secure implementation of the sowftware on the host MCU.

PN7220

NFC controller with NCI interface supporting EMV and NFC Forum applications

#### **Clock supply**

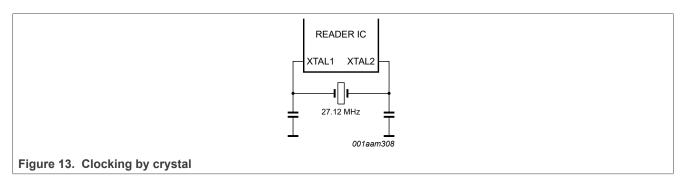

The PN7220 uses an external 27.12 MHz crystal as clock source for generating the RF field and its internal digital logic. Alternatively, an internal PLL allows using an accurate external clock source of either 24 MHz, 32 MHz, and 48 MHz (configured in EEPROM register CLK\_INPUT\_FREQ, 0012h)). This allows saving the 27.12 MHz crystal in systems which implement one of the mentioned clock frequencies.

#### **Integrated DC-DC**

The DC-DC is a step-up converter and is able to deliver an output voltage from approx. 2.8 V up to 6.0 V. The targeted output voltage can be configured by software. It allows a single supply voltage (for example, 3.3 V) while delivering maximum RF output power. Dependent on the application target either a direct transmitter supply or a transmitter supply by the integrated DC-DC can be chosen. The DC-DC is controlled by the Dynamic Power Control 2.0 to keep the power dissipation of the chip minimized in antenna loading cases which require a reduction of the RF output power.

#### Transmitter LDO (TX\_LDO)

The Transmitter output drivers are supplied by a transmitter LDO which reduces external noise and is used for the DPC functionality to lower the supply voltage of the transmitters. The high granularity of 100 mV for setting the TX\_LDO output voltage together with a sophisticated control loop and true current measurement ensures that a DPC regulation is not accidentally treated as received data.

#### Low-power card detection

The low-power card detection (LPCD) allows saving battery charge during polling for NFC counterparts like cards and mobile phones. In general, the low-power card detection provides a functionality, which allows to power down the reader for a certain amount of time to safe energy. After some time, the reader becomes active again to poll for cards. If no card is detected, the reader can go back to the power down state. During the polling time, a host controller can be set to a power-saving mode. An interrupt request from the PN7220 allows waking up the host controller in case an antenna detuning by a card or cell phone had been detected.

#### Dynamic power control 2.0

The next generation Dynamic Power Control (DPC2.0) with true transmitter current measurement works autonomous without host interaction. Avoiding additional host controller processing load is important for time critical applications like payment. A fast control response time of less than 1 ms allows using optimized antenna matchings.

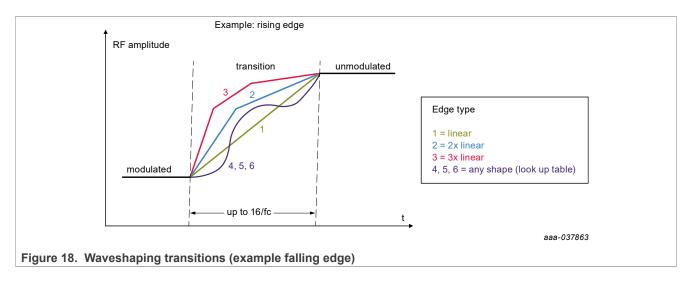

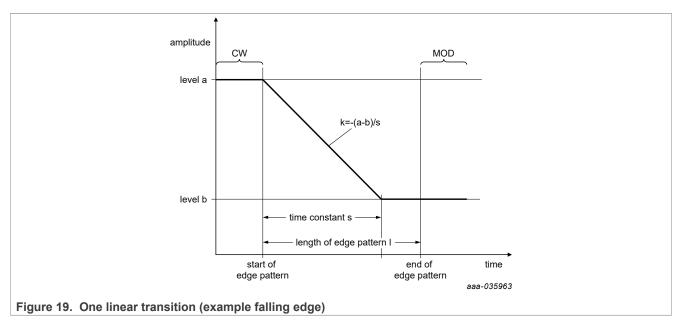

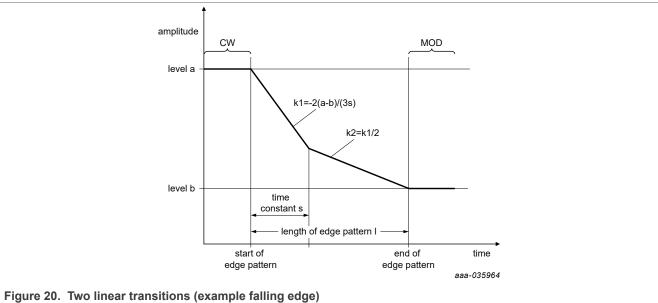

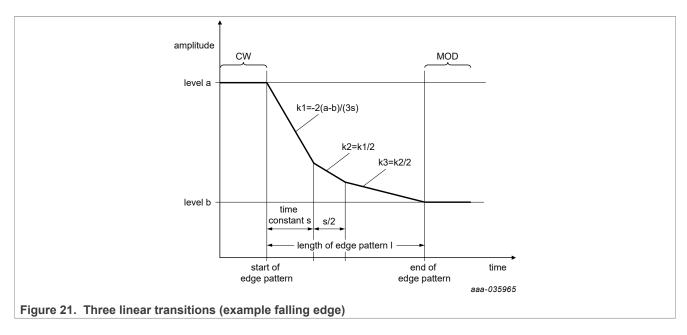

#### Adaptive wave shape control

The Adaptive Wave Shape Control (AWC) helps to keep the waveshapes within specification limits, even in case of antenna detuning. This simplifies the time-consuming antenna matching procedure and does not require any matching compromises to be taken.

#### Receiver signal level control

The receiver signal chain consists of an automatic controller RF input attenuator and a true Baseband Amplifier (BBA). This feature delivers an outstanding communication range with tags, labels, cards, and mobile phones.

## **RF Debugging**

Comprehensive and innovative debug features are implemented to support the NFC reader development even for difficult and non-standard compliant cards and mobile phones. An integrated contactless test station allows performing a non-intrusive debugging of receiver signals without the need of connecting additional wires to the chip. Capturing of chip-internal signals is done by configuring flexible trigger conditions, sampled internal data is stored in RAM memory, transferred by SPI to a host microcontroller and visualized on a PC by the NFC Cockpit

PN7220

All information provided in this document is subject to legal disclaimers.

NFC controller with NCI interface supporting EMV and NFC Forum applications

development tool. A virtual comfort interface (VCOM) is supported by the NFC cockpit tool, which allows to use the NFC cockpit together with any host microcontroller. Analog and digital debug signals (AUX1, AUX2) are available as well and allow the connection of an Oscilloscope for analog and digital signal debugging.

The receiver signal processing is optimized to cope with noisy environments. This is beneficial, especially in case a TFT display or DC-DCs are part of the NFC system design.

#### **Automatic EMD error handling**

An automatic EMD handling performed without host interaction relaxes the timing requirements on the host controller. Automatic EMD error handling according to ISO/IEC14443 and EMVCo 3.0 is supported. In addition, the EMD error handling is widely configurable, which allows adaptions in case of future possible specification changes.

#### Firmware update

The PN7220 supports a secure update of the implemented firmware. In Secure Firmware update mode, the PN7220 requires no dedicated physical handling of the SPI interface lines. The firmware download does not require any additional hardware pin to be handled, instead the download mode is activated by a command, followed by a hardware reset. After booting from reset, the PN7220 will be in download mode.

#### **EEPROM** configuration

Non-Volatile EEPROM memory of the PN7220 is used to store configuration data that must be preserved in case the PN7220 is not connected to any supply voltage. The configuration for dedicated RF protocols and antenna-dependent configuration is defined in this non-volatile memory as well as other configuration data which must be preserved during power supply disconnect is stored in this EEPROM memory. Examples for these are settings for receiver sensitivity, DPC, waveshaping, LPCD, and power supply configurations.

#### RF configuration

The PN7220 allows an automatic RF protocol selection based on the actual polling loop state. Pre-defined user configuration data is stored in non-volatile memory (EEPROM) and is automatically loaded for the modulation scheme currently activated by the polling loop.

Two dedicated configuration sets do exist for the RF configuration: One defining the settings in case the EMVCo polling loop is active, and another one on case the NFC Forum polling loop is active. Activating a dedicated polling loop automatically causes the related RF configuration to be loaded from the non-volatile memory. There is no need to load configuration files like it is required by other products supporting the NCI interface.

The loading of the RF configuration to the non-volatile memory is typically done only once during production.

#### Note:

Frequent automatic reloading of the RF configuration in the application is not recommended, since the number of possible configuration updates (EEPROM programming cycles) is technically limited.

#### 8.2 NCI interface

The functionality of the NCI interface is described in the user manual and the NCI 2.0 Interface standard.

#### 8.3 Byte and bit order

The byte and bit order describes the order of bytes or bits within a binary representation of a value in the memory, which can be a register or EEPROM.

"Array size" defines the number of elements of "type size". Type size can be uint8 (8 bit), uint16 (16 bit) or uint32 (32 bit).

PN7220

All information provided in this document is subject to legal disclaimers.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

The location of byte-sized data (8 bit) with an array size of 2 is as follows:

Value hex: 0x1234

address x: 12 address x+1: 34

The location of word-sized data (16 bit) is as follows:

Value hex: 0x1234

address x: 34 address x+1: 12

The location of word-sized data (16 bit) in an array size of 2 is as follows:

The placement of the array is large endian, the placement of nibbles of the variable is small endian.

Value hex: 0xAABBCCDD

address x: BB address x+1: AA address x+2: DD address x+3: CC

The location of double word-sized data (32 bit) is as follows:

Value hex: 0xAABBCCDD

address x: DD address x+1: CC address x+2: BB

address x+3: AA

| Byte sized data (8 bit) with an array size of 2  Data: 0x1234     | Data in Memory 12 34 Address X X+1               |

|-------------------------------------------------------------------|--------------------------------------------------|

| Word sized data (16 bit) with an array size of 1                  | Data in Memory 34 12                             |

| Data: 0x1234                                                      | Address X X+1                                    |

| Word sized data (16 bit) with an array size of 2 Data: 0xAABBCCDD | Data in Memory BB AA DD CC Address X X+1 X+2 X+3 |

| Word sized data (32 bit)                                          | Data in Memory DD CC BB AA                       |

| Data: 0xAABBCCDD                                                  | Address X X+1 X+2 X+3                            |

|                                                                   | aaa-036897                                       |

| Figure 3. Byte and bit order examples                             |                                                  |

Data from the EEPROM is read in little-endian format - LSB first. This means that the byte at the lower address is read first.

PN7220

All information provided in this document is subject to legal disclaimers.

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

The PN7220 is a little-endian system. This means that the byte at the lower address is read first.

#### 8.4 Initial calibration

The PN7220 requires a calibration before the RF field is switched on for the first time with unloaded condition.

"Unloaded" means: Without any additional metal in proximity of the antenna, except for the NFC reader components itself.

During development of new readers, this calibration shall be done each time the antenna design, antenna matching, or EMC filter is modified.

The calibration sequence is the following:

Write EEPROM CfgNovCal - 0x00

Write REGISTER TX\_NOV\_CALIBRATE\_AND\_STORE\_VAL - 0x01

Write EEPROM CfgNovCal - 0x02

## 8.5 System power states

The PN7220 can operate in different power states. The functionality and current consumption is dependent on the actual system power state.

Power states can be changed by the level on the pin VEN and by connecting/disconnecting the power supply of VBAT. Power state change will also be triggered by certain events - VDDIO Loss, overcurrent detection, overtemperature.

In addition, state changes are triggered possible by host commands.

Disconnecting and connecting the power supply on VBAT restarts the PN7220 always in Active State after releasing the pin VEN (transition low to high).

A transition of low to high on pin VEN restarts the PN7220 always in Active State.

The following power states are supported:

| Power state     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               | Typical current consumption |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| Power off       | The NFC system (supply pin VBAT, RF transmitter) is not supplied by a battery/system PMU. Other domains might be supplied (for example, I/O pad interface on pin VDDIO).  Device is not functional                                                                                                                                                                                                                                        | -                           |  |

| PMU off         | The NFC system is disabled by the host via a low signal on pin VEN. No internal clocks of the PN7220 are active. Entry to PMU OFF can also be triggered by power loss on VDDIO. Wake-up events to change PMU OFF state: Power reset on pin VBAT, VEN rising edge, VDDIO restore.                                                                                                                                                          | 5 μΑ                        |  |

| ULP standby     | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                             | -                           |  |

| Hard power down | The NFC system is disabled by the host system via the reset/enable signal on VEN or by detecting an external condition (for example, battery voltage monitor). The power dissipation is reduced to a minimum. No power dissipation or leakage is expected on the different interfaces. Low-power resources are enabled (VDDC_LP, VHV_LP, LQ_REF, LQ-BIAS). LFO clock is available. PCRM is supplied and is running in low-power state. I/ | 40 μΑ                       |  |

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

| Power state | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Typical current consumption       |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

|             | Os are supplied by VDDC_HP. Wake-up events: Power reset on pin VBAT, VEN rising edge,                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |  |

| Standby     | The NFC system can switch after a specific time of inactivity automatically into a low-power mode to minimize power dissipation. The state of external interfaces is maintained properly. PMU operates in low-power state. Wake-up counter clock is available. PCRM is supplied and running in low-power mode. I/Os are supplied by VDDC_LP. PMU FSM in PCRM manages the transition in power state. Wake-up sources: Activity on host IF, SWPM communication, LPDET, wake-up counter, power loss on VDDIO, GPIO, RxPROT, No High Temp on TX and so on. | 45 μΑ                             |  |

| Active      | The PN7220 is able to process internal or external events or data. All external power supply sources and the external clock must be available, and all internal clocks are active.                                                                                                                                                                                                                                                                                                                                                                     | 20 mA (system without RF current) |  |

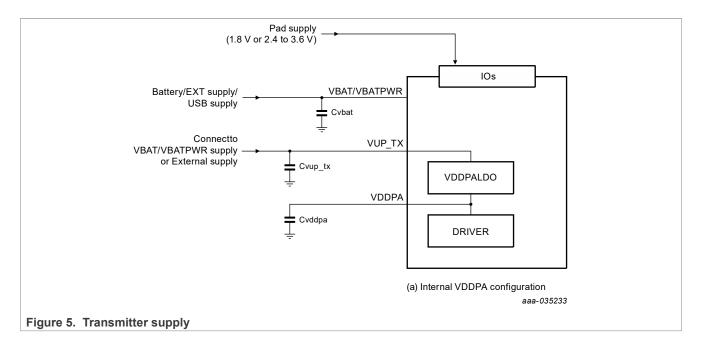

# 8.6 Power supply

The device allows to configure different power supply options for the transmitter power amplifier. To make use of them, a combination of external connections and chip internal configurations must be done. The following supply options are available:

- Internal VDDPA configuration: The TX power amplifier is supplied by the internal voltage regulator (TX\_LDO). In this configuration the DPC, current measurement and overcurrent protection is available. In addition, the TX LDO is adding an improved rejection of noise on the supply lines.

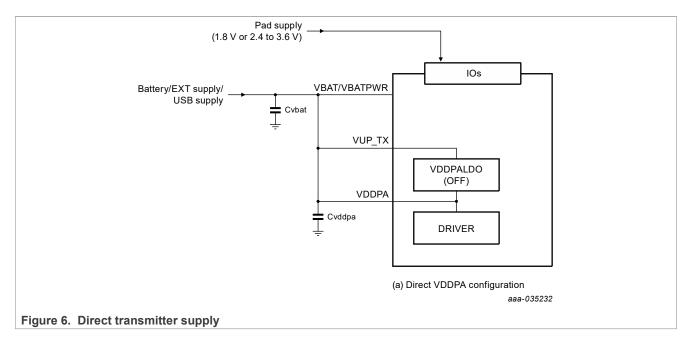

- Direct VDDPA configuration: This configuration is recommended for applications which require highest

efficiency, like battery supplied devices. In this configuration, a battery can be connected directly to the

transmitter supply avoiding the voltage drop of approximately 0.3 V caused by the TX\_LDO. A clean supply

voltage without noise is required to achieve a good RF performance.

In this configuration the DPC, current measurement and overcurrent protection is not available.

# 8.6.1 System power supply overview

The PN7220 is using three different supplies each for the following functional blocks:

- 1. Supply for the host interface and GPIOs (VDDIO)

- 2. Supply for the analog and digital blocks (VBAT/VBAT PWR)

- 3. Supply of the RF drivers (VDDPA), DC-DC (VBAT\_PWR), and TX\_LDO (VUP)

The functionality of the GPIOs, host interface and internal analog and digital blocks is independent from the supply of the RF driver. This allows to configure a dedicated transmitter supply configuration at any time. Care shall be taken to switch on the RF field only after the transmitter-related power supply had been configured according to the external physical supply connections (VDDPA, VBAT\_PWR, VUP).

The power supply configuration is configured in EEPROM and therefore will not get lost in case of power supply loss or reset of the chip. Typically, this configuration is only performed once during the production of a reader.

RF field shall not be turned on without setting the correct power supply configuration in the EEPROM.

Note: The Voltage on pin VDDIO must always be smaller or equal to the Voltage on pin VBAT.

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 8.6.2 Connecting blocking capacitors

Some pins are connected to blocking supply capacitors. PCB traces to these capacitors must be as short as possible, and a low-ohmic grounding of the GND-side of the capacitors is required for optimized RF performance.

#### 8.6.3 Transmitter power supply

The PN7220 is configured by EEPROM for the different power supply options.

The following EEPROM Addresses are used to configure the power supply of the transmitter:

DCDC\_PWR\_CONFIG (0000h) - Enables/disables and configures the DC-DC according to the external supply connections.

TX\_LDO\_CONFIG (address 0002h) - Enables/disables and configures the TX\_LDO.

TX LDO VDDPA HIGH (address 0006h) - initial out voltage when DPC is used.

TX\_LDO\_VDDPA\_LOW (address 0007h) - lowest VDDPA when DPC is used.

TX\_LDO\_VDDPA\_MAX\_RDR (address 0008h) - maximum voltage to be set in reader mode used by DPC.

TX\_LDO\_VDDPA\_MAX\_CARD (address 0009h) - VDDPA maximum voltage to be set in card mode used by DPC.

No specific registers are required to configure the pad supply (VDDIO) or the supply for the analog and digital blocks (VUP).

#### 8.6.3.1 TX LDO transmitter supply

TX\_LDO supplied VDDPA configuration: The TX power amplifier is supplied by the internal voltage regulator (TX\_LDO).

In this configuration the DPC, current measurement and overcurrent protection is available. In addition, the TX LDO is adding an improved rejection of noise on the supply lines.

A decoupling cap is required on VDDPA pin.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

# 8.6.3.2 Direct transmitter supply

Direct VDDPA configuration:

TX\_LDO must be configured OFF by SW configuration. VUP\_TX and VDDPA connected to VBAT/VBATPWR.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

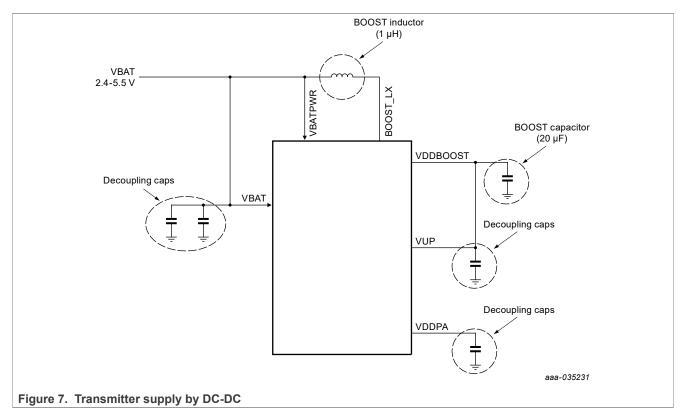

# 8.6.3.3 DC-DC (boost) supply

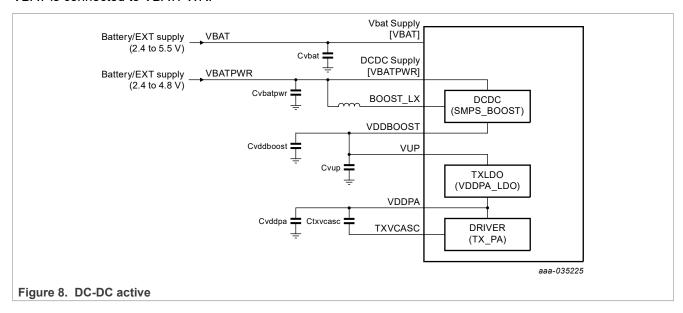

# 8.6.3.4 Configuration example 1: TX\_LDO transmitter supply - DC-DC active

VBAT is connected to VBATPWR.

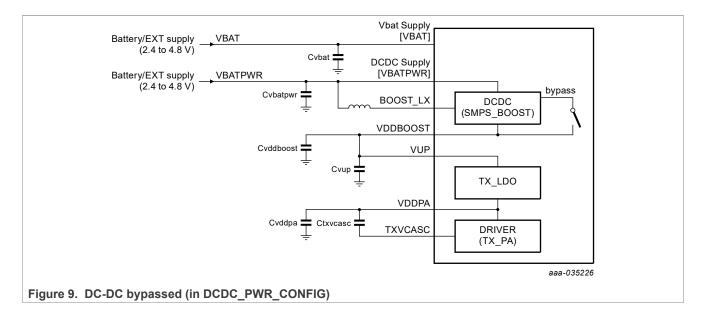

# 8.6.3.5 Configuration example 2: TX\_LDO transmitter supply - DC-DC bypassed

VBAT is connected to VBATPWR.

17220 All information provided in this document is subject to legal disclaimers.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

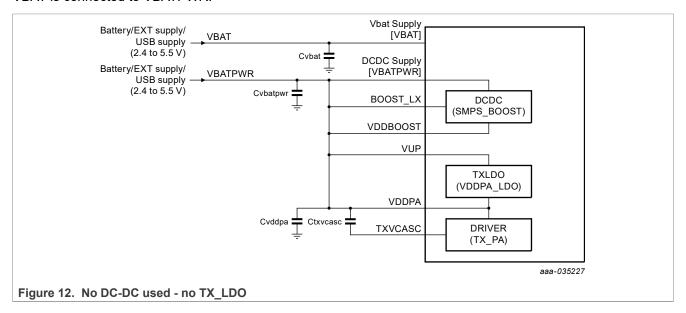

# 8.6.3.6 Configuration example 3: TX\_LDO transmitter supply connected to VBAT - no DC-DC VBAT is connected to VBATPWR.

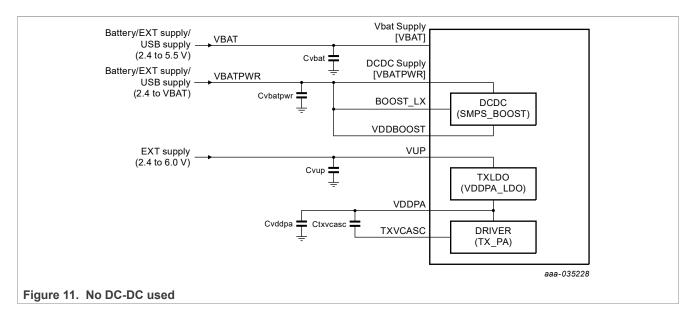

# 8.6.3.7 Configuration example 4: TX\_LDO supplied independent from VBAT - no DC-DC VBAT is connected to VBATPWR.

# NFC controller with NCI interface supporting EMV and NFC Forum applications

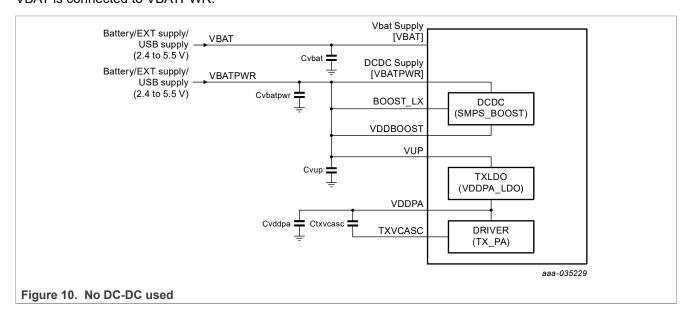

#### 8.6.3.8 Configuration example 5: TX\_LDO not used - no DC-DC

#### VBAT is connected to VBATPWR.

NFC controller with NCI interface supporting EMV and NFC Forum applications

# 8.6.3.9 Supply voltage range for transmitter supply configuration examples

Table 4. Supply voltage range configuration

| Supply                                        | Config1: TX_LDO transmitter supply DC-DC active           | Config2:<br>TX_LDO<br>transmitter supply<br>DC-DC bypassed | Config3:<br>TX_LDO<br>transmitter<br>supply connected<br>to VBAT<br>no DC-DC | Config4:<br>TX_LDO supplied<br>independent from<br>VBAT<br>no DC-DC | Config5:<br>TX_LDO not used<br>no DC-DC |

|-----------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------|

| EEPROM c                                      | onfiguration for DPC ENAB                                 | LED - configured in DF                                     | C_CONFIG (address                                                            | s 0076h)                                                            |                                         |

| DCDC_<br>PWR_<br>CONFIG<br>(address<br>0000h) | - 0xE4(Variable BOOST with Auto Bypass) 0xE2(Fixed BOOST) | 0xE4 (Variable<br>BOOST with Auto<br>Bypass)               | 0x01                                                                         | 0x01                                                                | NA                                      |

| TXLDO_<br>VDDPA_<br>HIGH<br>(0x06)            | 0x0 (1.5 V)                                               | 0x0(1.5 V)                                                 | 0x0(1.5 V)                                                                   | 0x0(1.5 V)                                                          | NA                                      |

| TXLDO_<br>VDDPA_<br>MAX_<br>RDR<br>(0008h)    | 0x2A(5.7 V)                                               | 0x2A(5.7 V)                                                | 0x2A(5.7 V)                                                                  | 0x2A(5.7 V)                                                         | NA                                      |

| BOOST_<br>DEFAULT_<br>VOLTAGE<br>(000Ah)      | 0x1D (6 V).                                               | NA                                                         | NA                                                                           | NA                                                                  | NA                                      |

| EEPROM c                                      | onfiguration - DPC DISABL                                 | ED - configured in DPC                                     | C_CONFIG (address                                                            | 0076h)                                                              |                                         |

| DCDC_<br>PWR_<br>CONFIG<br>(address<br>0000h) | - 0xE4(Variable BOOST with Auto Bypass) 0xE2(Fixed BOOST) | 0xE4 (Variable<br>BOOST with Auto<br>Bypass)               | 0x01                                                                         | 0x01                                                                | 0x00                                    |

| TXLDO_<br>VDDPA_<br>HIGH<br>(0x06)            | 0x0 (1.5 V)                                               | 0x0(1.5 V)                                                 | 0x0(1.5 V)                                                                   | 0x0(1.5 V)                                                          | 0x0(1.5 V)                              |

| TXLDO_<br>VDDPA_<br>MAX_<br>RDR<br>(0008h)    | NA                                                        | NA                                                         | NA                                                                           | NA                                                                  | NA                                      |

| BOOST_<br>DEFAULT_<br>VOLTAGE<br>(000Ah)      | 0x1D (6 V).                                               | NA                                                         | NA                                                                           | NA                                                                  | NA                                      |

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

Table 5. Supply voltage range

| Supply  | Config1:<br>TX_LDO transmitter<br>supply<br>DC-DC active | DC-DC bypassed                  | Config3:<br>TX_LDO<br>transmitter<br>supply connected<br>to VBAT<br>no DC-DC | Config4:<br>TX_LDO supplied<br>independent from<br>VBAT<br>no DC-DC |             |

|---------|----------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------|

| VBAT    | 2.8 V 4.8 V                                              | 2.8 V 4.8 V                     | 2.4 V 5.5 V                                                                  | 2.4 V 5.5 V                                                         | 2.4 V 5.5 V |

| VBATPWR | 2.8 V 4.8 V                                              | 2.8 V 4.8 V                     | 2.4 V 5.5 V                                                                  | 2.4 V 5.5 V                                                         | 2.4 V 5.5 V |

| VUP     | 3.1 V 6.0 V                                              | 2.8 V 6.0 V                     | 2.4 V 6.0 V                                                                  | 2.4 V 6.0 V                                                         | 2.4 V 5.5 V |

| VDDPA   | VUP-0.3V drop of<br>TX_LDO. max 5.7 V                    | VBATPWR - 0.5 V<br>voltage drop | internally<br>connected to<br>TX_LDO                                         | internally connected to TX_LDO                                      | 2.4 V 5.5 V |

# 8.7 Clock generation

The device supports the operation with two clock options, which is configured in EEPROM address CLK INPUT FREQ (0012h).

One option is clocking by a crystal (default), the other a clocking by an external clock input frequency.

It is important to consider additional phase noise introduced, for example by clock drivers in the design. Phase noise of the external clock has an impact on the RF performance which can be achieved.

#### 8.8 External interfaces

The PN7220 requires the connection of a power supply, and a clock source like crystal or external clock and a host microcontroller connected to at least one NCI host interface for operation.

Additional connections of the package require the connection of stabilizing capacitors and ground.

The RF interface connects transmitter and receiver to the EMC filter of a connected antenna matching network. Additional connections are available for the GPIOs (on PN7220 only outputs are implemented).

The device supports the connection of up to 3x TDA8035 contact reader ICs which allow to realize ISO/IEC7816 compliant interfaces.

# 8.9 Transmitter overcurrent and temperature protection

The PN7220 implements different mechanisms to protect the chip against damage.

PN7220

All information provided in this document is subject to legal disclaimers.

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

On the one hand, an overcurrent protection exists which shuts down the transmitter driver if there is a out of spec current. This can be enabled in EEPROM TXLDO\_CONFIG (0002h), bit 11: overcurrent enable (0: disable, 1: enable)

An NCI notification is used to indicate the shut-down of the transmitter driver to a connected host.

On the other hand, an internal temperature sensor allows to monitor the temperature of the chip. This is configured in the EEPROM TEMP\_WARNING (0648h). Three temperatures can be configured: 114 °C, 2:125 °C, 3:130 °C.

An NCI notification is used to indicate this temperature warning to a connected host.

The actual measured temperature is available in the register TEMP\_SENSOR (005Bh). The chip will go into standby immediately.

This is a safety feature only. A design shall not functionally rely on this feature since the operating conditions will be violated if the overcurrent detection becomes active.

## 8.10 Dynamic power control (DPC)

The DPC is used for a special antenna tuning, called "symmetric antenna tuning". For an "asymmetric antenna tuning", the DPC is not required.

However, even for "asymmetric antenna tuning" with high output power needs, it might turn out that the RF field is too strong near of the antenna to be compliant with ISO/IEC14443 requirements. In this case, the DPC can be used as well to reduce the RF output power dependent on the distance of the card from the reader antenna.

The DPC works very well with a tuning called "symmetric tuning". With symmetric tuning, a detuning of the antenna is causing a reduction of the antenna impedance. This low antenna impedance might lead to a current which is too high for the targeted application. The DPC allows to limit the transmitter current even under antenna detuning conditions.

#### DPC is useful:

- To achieve NFC Forum and ISO/IEC 14443 compliancy (e.g. NFC Forum Power Transfer Maximum, ISO/IEC 14443 Field Emission Maximum)

- · To improve interoperability

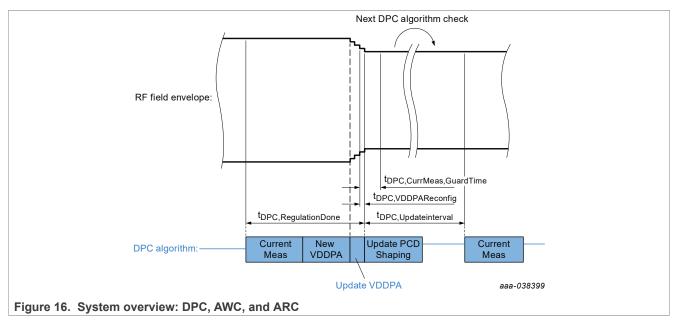

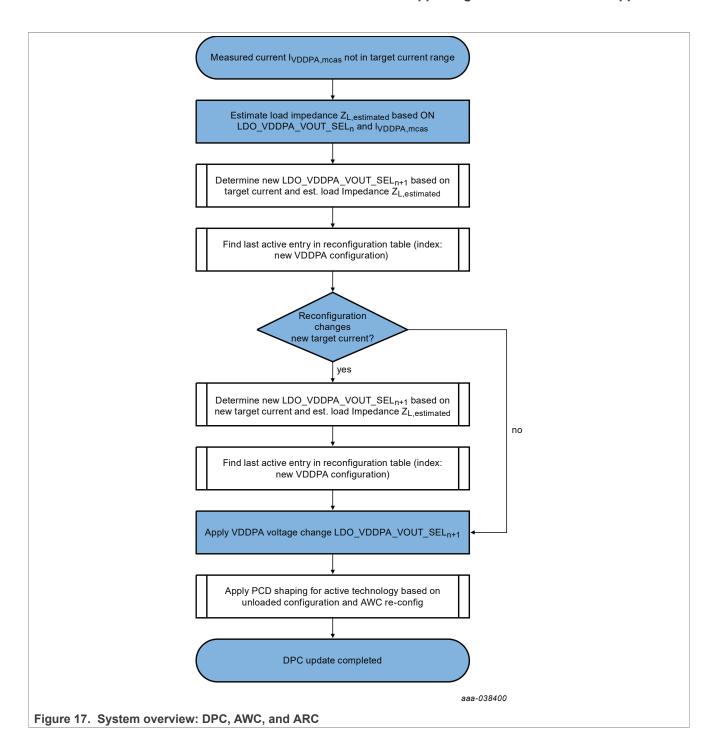

The Dynamic Power Control (DPC 2.0) allows controlling the transmitter driver voltage in 100 mV steps dependent on the actual transmitter current.

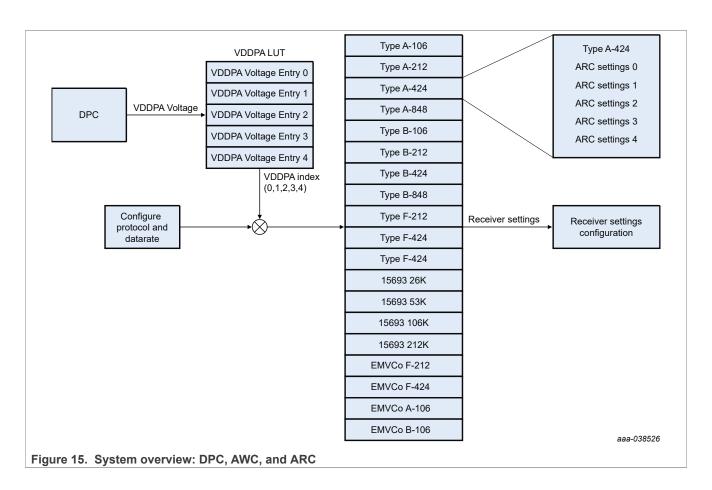

A lookup table is used to configure the transmitter output voltage and by this control the RF output power.

The DPC allows to define two different targets current and maximum VDDPA settings for the two available modes to address EMVCo and NFC-related requirements with the same antenna.

Features of the Dynamic power control (DPC 2.0):

- True current measurement provides maximum information for the regulation loop

- The transmitter current can be limited and additionally reduced according to detected transmitter current condition / antenna detuning condition

- DPC works autonomously without host interaction causing no additional processing load on the host

- Fastest response time of 1 ms for regulation

- Used for adaptive waveshape control (AWC)

- Used for adaptive RX sensitivity control (ARC)

The DPC is able to operate in two modes:

1. Current limiting mode

All information provided in this document is subject to legal disclaimers.

#### NFC controller with NCI interface supporting EMV and NFC Forum applications

## 2. Current limiting + Current reduction mode

The DPC is configured in the EEPROM, this configuration is used after startup. This avoids that the host must configure the chip after each reset or power off.

The following EEPROM registers are most relevant for the DPC configuration:

DPC\_Config: Enables/Disables the DPC (enable: 0x39, disable: 0x00)

**DPC\_TargetCurrent:** Unloaded VDDPA target current in mA, the target current +/- Hysteresis is limiting the current for the DPC.

• The DPC\_TargetCurrent is the current which can be measured for the selected antenna impedance and transmitter supply voltage in unloaded condition. This is the current the system is designed to operate at. For each of the modes - NFC Forum and EMVCo, one dedicated configuration does exist:

DPC\_TargetCurrent\_EMVCO

DPC TargetCurrent NFC

VDDPA\_max\_EMVCo

VDDPA max NFC

All other DPC-related settings are used for both modes.

DPC\_Hysteresis: Absolute difference to current target current in mA that triggers a DPC update event.

• The configuration of the hysteresis ensures, that the DPC is not regulating if small changes of the transmitter current occur due to external disturbances. A typical value for the DPC Hysteresis is e.g. 20 mA.

DPC\_Lookup\_Table: configures the current reduction

The DPC\_LOOKUP\_TABLE allows in addition to the limitation of the current, to configure

- an additional current reduction on top of the current limitation, achieved by further lowering the transmitter supply voltage